# A Software Fault-Tolerance Mechanism for Mixed-Critical Real-Time Applications on Consumer-Grade Many-Core Processors

vorgelegt von Peter Munk, M.Sc. geb. in Ostfildern

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften - Dr.-Ing. -

genehmigte Dissertation

Promotionsausschuss:

Vorsitzender:

Gutachter:

Gutachter:

Prof. Dr. Ben Juurlink

Prof. Dr. Hans-Ulrich Heiß

Prof. Dr.-Ing. Michael Glaß

Gutachterin:

Prof. Dr. Sabine Glesner

Tag der wissenschaftlichen Aussprache: 22. Juli 2016

### **Abstract**

The number of cores per processor continues to increase due to higher integration rates and smaller feature sizes. This development of many-core processors leads to a higher susceptibility to soft errors, which are caused by high-energy particle strikes.

At the same time, the complexity and computational demand of automotive applications is rising steadily, following the vision of highly automated driving. Due to their computational performance and their comparatively low costs, commercial off-the-shelf many-core processors become attractive in cost-driven mass markets such as the automotive domain. In order to execute safety-critical automotive applications on such processors and fulfill the obligatory safety standards, fault-tolerance mechanisms have to be installed. However, hardware-implemented fault-tolerance mechanisms increase the unit costs and are uncommon in consumer-grade many-core processors, which are designed for applications without safety requirements.

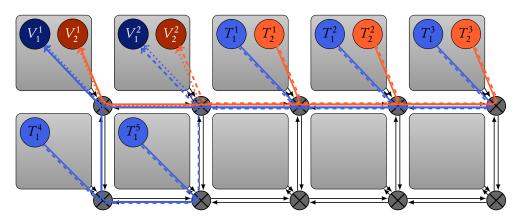

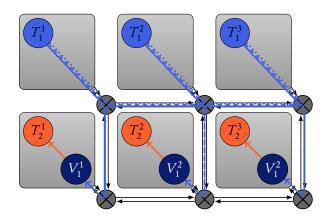

In this thesis, we present an adaptive software-implemented fault-tolerance mechanism that is based on the N modular redundancy principle, leveraging the spatial redundancy of many-core processors. In order to eliminate the voter as a single point of failure, our mechanism employs two fail-silent voters that check and repair each other. The fail-silent behavior is achieved by an encoded voting procedure. Our fault-tolerance mechanism includes a state-conserving repair procedure to recover from replica and voter failures. In contrast to related work, we consider failures in all software components, including the OS kernel.

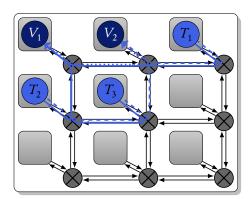

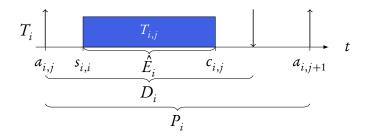

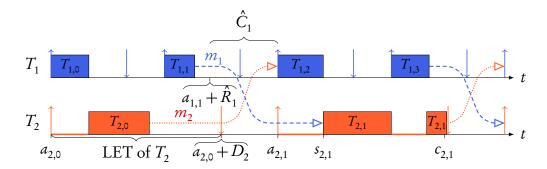

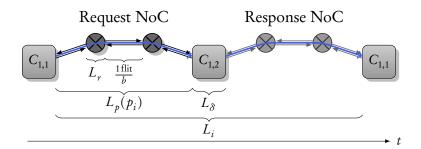

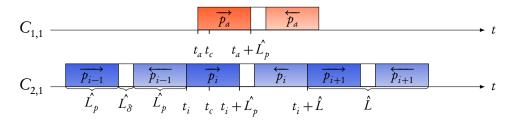

In order to meet the real-time requirement of automotive applications, our fault-tolerance mechanism utilizes well-known scheduling policies. However, consumer-grade many-core processors do not commonly provide an inter-core communication with latency and bandwidth guarantees. Therefore, we propose a software-based approach that guarantees a bounded latency for dynamic communication. The main principle of our approach is to limit the packet injection rate for all sources.

Furthermore, we present a framework that eases the development of safety-critical real-time applications on consumer-grade many-core processors. The framework adapts our fault-tolerance mechanism for each task of a mixed-critical task set such that the task's reliability and availability requirements are satisfied with minimum resource usage. A discrete Markov chain model of our mechanism is used to determine the resulting reliability and availability of each task. Measurements on a cycle-accurate and bit-accurate many-core processor simulator with realistic fault injections show the advantage of our adaptive software fault-tolerance mechanism and demonstrate the trade-off between resource usage and fault-tolerance level.

# Zusammenfassung

Aufgrund schrumpfender Strukturbreiten und eines steigenden Integrationsgrads wächst die Anzahl der Rechenkerne pro Prozessor kontinuierlich. Diese Entwicklung von Many-Core Prozessoren bedingt allerdings eine höhere Anfälligkeit für transiente Fehler, welche aus energiereichen Partikeleinschlägen resultieren.

Getrieben von der Vision des hochautomatisierten Fahrens nehmen die Komplexität und der Rechenbedarf von Software im Automobilbereich stetig zu. Aufgrund ihrer Rechenleistung und ihrer vergleichsweise geringen Stückkosten wird der Einsatz von auf dem Markt erhältlichen Many-Core Prozessoren in stückkostengetrieben Massenmärkten wie dem Automobilereich zunehmend attraktiv. Um sicherheitskritische Anwendungen auf solchen Prozessoren auszuführen und die entsprechenden Sicherheitsnormen zu erfüllen, werden Fehlertoleranzmechanismen benötigt. In Hardware umgesetzte Mechanismen erhöhen die Stückkosten und sind nicht in gängigen Many-Core Prozessoren verbaut, welche für Anwendungen ohne Sicherheitsanforderungen ausgelegt sind.

In dieser Dissertation präsentieren wir einen adaptiven, in Software umgesetzten Fehlertoleranzmechanismus, welcher aufgrund des Prinzips der N Modular Redundancy die räumliche Redundanz von Many-Core Prozessoren ausnutzt. Um die Vergleichseinheit als singuläre Fehlerursache auszuschließen, enthält unser Mechanismus zwei Vergleichseinheiten, welche sich gegenseitig überprüfen und reparieren. Wir verwenden ein kodiertes Vergleichsverfahren, um sicherzustellen, dass jede Vergleichseinheit im Fehlerfall keine falschen Ergebnisse ausgibt. Unser Fehlertoleranzmechanismus enthält eine zustandserhaltende Reparaturprozedur, um Ausfälle von Repliken und Vergleichseinheiten zu kompensieren. Im Gegensatz zu verwandten Arbeiten berücksichtigt unser Ansatz Fehler in allen Softwarekomponenten, einschließlich dem Betriebssystem.

Um die Echtzeitanforderungen der Anwendung zu erfüllen, arbeitet unser Fehlertoleranzmechanismus mit bestehenden Scheduling-Verfahren. Allerdings bieten gängige Many-Core Prozessoren typischerweise keine Hardwareunterstützung für den Informationsaustausch zwischen den Rechenkernen mit garantierter Latenz und Bandbreite. Deshalb stellen wir einen softwarebasierten Ansatz vor, welcher die Latenzen dynamischer Kommunikation zwischen den Rechenkernen garantiert. Das zugrundeliegende Prinzip unseres Ansatzes ist es, die Paketinjektionsrate für alle Quellen zu beschränken.

Zudem präsentieren wir ein Framework, welches die Umsetzung von sicherheitskritischen Echtzeitanwendungen auf gängigen Many-Core Prozessoren erleichtert. Das Framework passt unseren Fehlertoleranzmechanismus für jede Softwareeinheit so an, dass deren Zuverlässigkeits- und Verfügbarkeitsanforderungen mit minimalem Ressourceneinsatz erreicht werden. Ein Modell des Fehlertoleranzmechanismus als diskrete Markow-Kette ermöglicht die Berechnung der sich ergebenden Zuverlässigkeit und Verfügbarkeit jeder Softwareeinheit. Messungen auf unserem zyklen- und bitakkurat simulierten Many-Core Prozessor mit realistischer Fehlerinjektion zeigen den Vorteil unseres adaptiven Software-Fehlertoleranzmechanismus und demonstrieren den Kompromiss zwischen Ressourcenverbrauch und Fehlertoleranzniveau.

## **Acknowledgment**

Writing this thesis would not have been possible without the support of many people. First and foremost, I want to thank Prof. Dr. Hans-Ulrich Heiß for supervising my thesis and providing insightful comments and helpful advice. I thank my co-advisors Prof. Dr. Sabine Glesner and Prof. Dr. Michael Glaß for their valuable feedback on my thesis. Special thanks go to Prof. Dr. Jan Richling, Dr. Helge Parzjegla, and Prof. Dr. Reinhard Karnapke for all the fruitful discussions we had and their helpful comments. I would like to thank all team members of the KBS research group at the TU Berlin, especially Anselm Busse and Matthias Druve, for the answers to all my questions and their support, and Dr. Matthias Diener for proof-reading this thesis.

As an industrial PhD student at the Robert Bosch GmbH, I had the opportunity to gain insights into academia and industry at the same time. I thank my supervisor Dr. Björn Saballus for his guidance on my way as a PhD student and his kind way to increase my motivation and improve the focus of my work. I would like to thank all members of the ManyCore Project and the CR/AEA department, especially Dr. Jochen Härdtlein and Dr. Dirk Ziegenbein, for giving me the opportunity to work in such an open-minded and friendly environment. Special thanks go to Dr. Rai Devendra, Dr. Dakshina Dasari, and Dr. Matthias Freier for proof-reading this thesis. I feel lucky to share my workplace with my fellow PhD students Hendrik Röhm, Alexander Biewer, Martin Lowinski, Dr. Matthias Freier, Felix Rützel, and Sören Braunstein. Thank you for the inspiring discussions about work and about life in general as well as the good times we had together.

I am grateful for having received a fellowship from the Software Campus development program, which is funded by Germany's Federal Ministry of Education and Research. This fellowship initiated a strong and fruitful collaboration with Dr. Mohammad Shadi Alhakeem and Ralphael Lisicki, both of which I owe a debt of heartfelt gratitude. Without their support, this thesis would not have been possible in the way it is today.

Last but not least, I want to thank my parents Roland and Mechthild Munk and my brother Dr. Martin Munk for paving me the way to where I am today and their continuous encouragement. These acknowledgements would be incomplete without wholeheartedly thanking my wife Sandra for her never-ending support, including proof-reading this thesis, and all the joyful moments in my life.

# **Contents**

| 1 | Intr | oduction                                | 1              |  |  |  |  |

|---|------|-----------------------------------------|----------------|--|--|--|--|

|   | 1.1  | Motivation                              | 1              |  |  |  |  |

|   | 1.2  | Problem Statement                       | 3              |  |  |  |  |

|   | 1.3  | Research Questions                      | 4              |  |  |  |  |

|   | 1.4  | Proposed Solution                       |                |  |  |  |  |

|   | 1.5  | Main Contributions                      | 6              |  |  |  |  |

|   | 1.6  | Context                                 | 7              |  |  |  |  |

|   | 1.7  | Outline                                 | 7              |  |  |  |  |

| 2 | Fun  | damentals                               | 9              |  |  |  |  |

|   | 2.1  | Embedded Systems                        | 9              |  |  |  |  |

|   |      | 2.1.1 Real-Time Systems                 | 9              |  |  |  |  |

|   |      |                                         | 15             |  |  |  |  |

|   | 2.2  |                                         | 19             |  |  |  |  |

|   |      |                                         | 20             |  |  |  |  |

|   |      |                                         | 21             |  |  |  |  |

|   |      |                                         | 23             |  |  |  |  |

|   |      |                                         | 28             |  |  |  |  |

|   |      |                                         | 28             |  |  |  |  |

|   | 2.3  |                                         | 33             |  |  |  |  |

|   |      |                                         | 33             |  |  |  |  |

|   |      |                                         | 34             |  |  |  |  |

|   |      |                                         | 36             |  |  |  |  |

|   | 2.4  | Summary                                 | 39             |  |  |  |  |

| 3 | Rela | ated Work                               | <b>ļ</b> 1     |  |  |  |  |

|   | 3.1  | Dynamic GS Communication on NoCs        | 41             |  |  |  |  |

|   |      | ·                                       | 41             |  |  |  |  |

|   |      |                                         | <del>1</del> 2 |  |  |  |  |

|   | 3.2  |                                         | 43             |  |  |  |  |

|   |      | <b>I I</b>                              | 14             |  |  |  |  |

|   |      |                                         | <del>1</del> 5 |  |  |  |  |

|   | 3.3  |                                         | 53             |  |  |  |  |

| 4 | Dyn  | amic Guaranteed Service Communication 5 | 55             |  |  |  |  |

|   | 4.1  |                                         | 55             |  |  |  |  |

|   | 4.2  |                                         | 56             |  |  |  |  |

|   |      |                                         | 57             |  |  |  |  |

|   |      | •                                       | 58             |  |  |  |  |

|   |      | · · · · · · · · · · · · · · · · · · ·   | 60             |  |  |  |  |

|   | 4.3  | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61               |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|   | 4.4  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62               |

| 5 | Soft | ware Fault-Tolerance Mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63               |

| J | 5.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63               |

|   | 5.2  | r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66               |

|   | 3.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67               |

|   |      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67<br>69         |

|   |      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0)<br>72         |

|   | 5.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72<br>73         |

|   | 5.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 73<br>74         |

|   |      | - <b>r</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74<br>75         |

|   |      | <b>T</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |

|   |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76<br>76         |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76<br>77         |

|   | - 4  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77<br><b>7</b> 0 |

|   | 5.4  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 78<br><b>7</b> 8 |

|   |      | Tr.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78<br><b>7</b> 0 |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79<br><b>-</b> 2 |

|   |      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79               |

|   |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80               |

|   | 5.5  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 81               |

|   |      | 11 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 82               |

|   |      | O Company of the Comp | 82               |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84               |

|   | 5.6  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 86               |

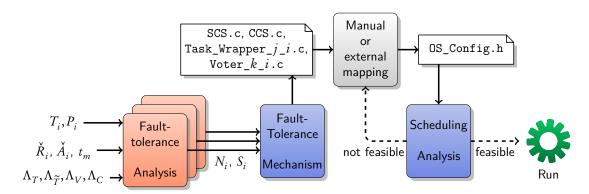

| 6 | Soft | ware Fault-Tolerance Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87               |

|   | 6.1  | Fault-Tolerance Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87               |

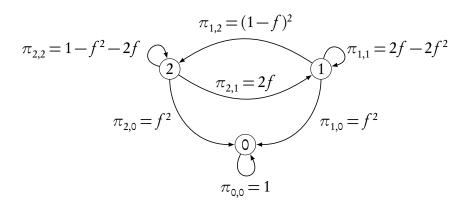

|   | 6.2  | Markov Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 88               |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89               |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90               |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90               |

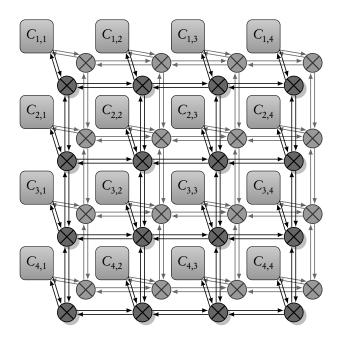

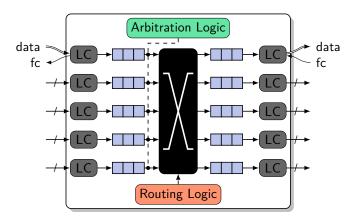

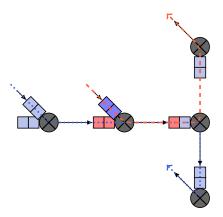

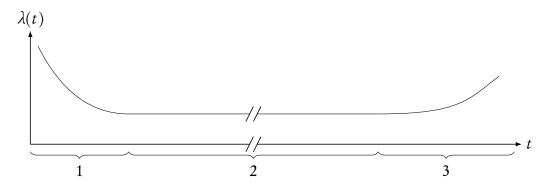

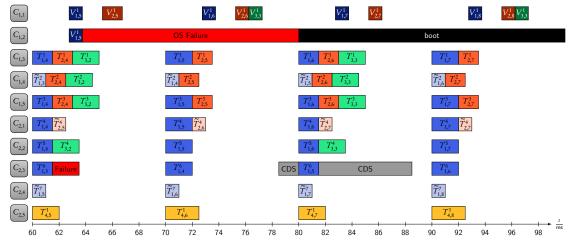

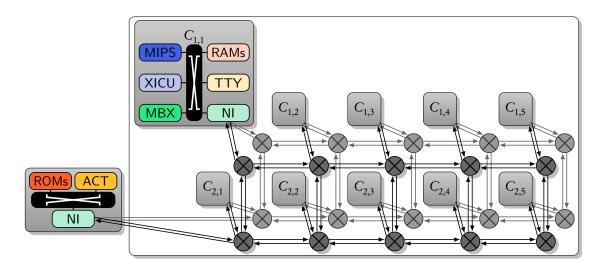

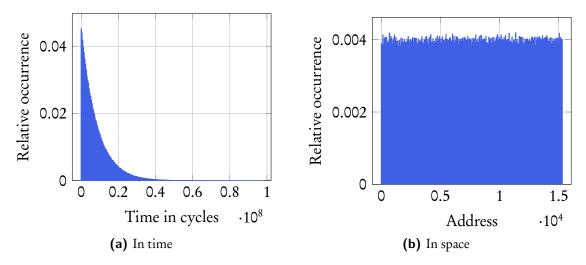

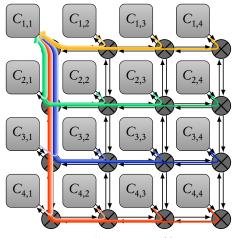

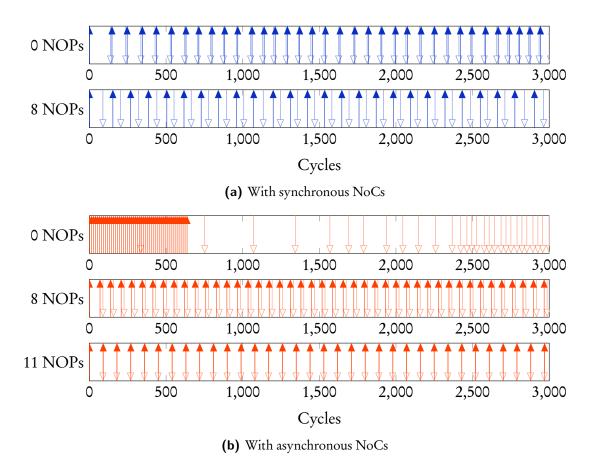

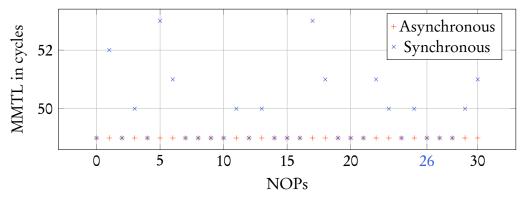

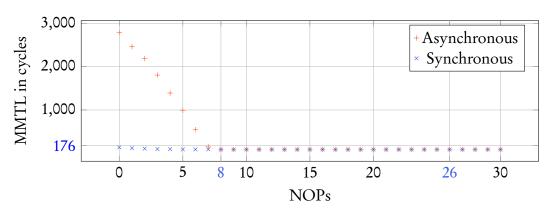

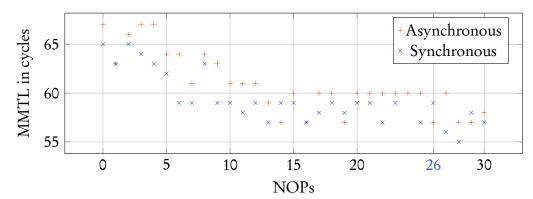

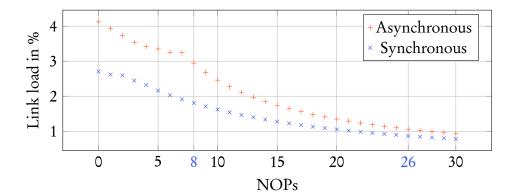

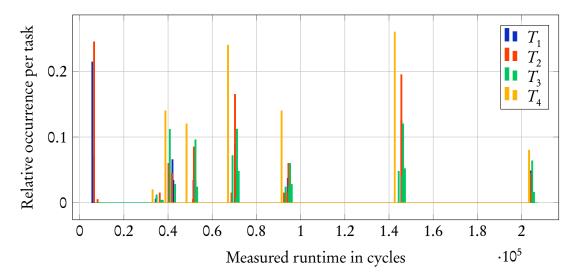

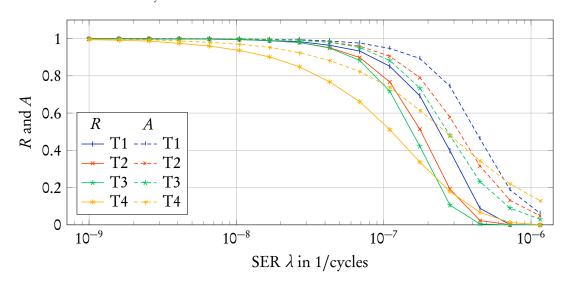

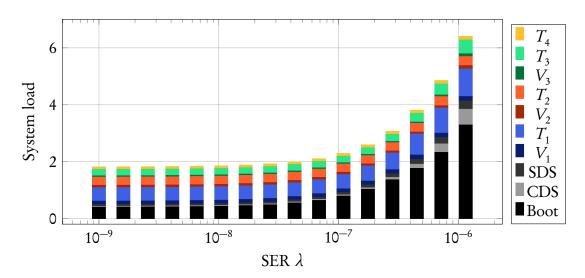

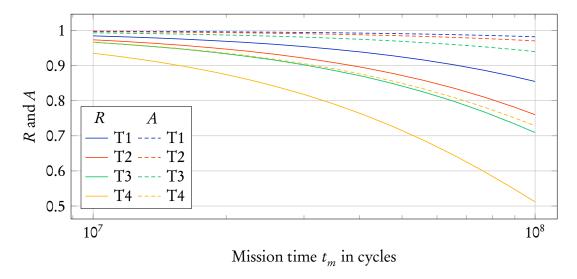

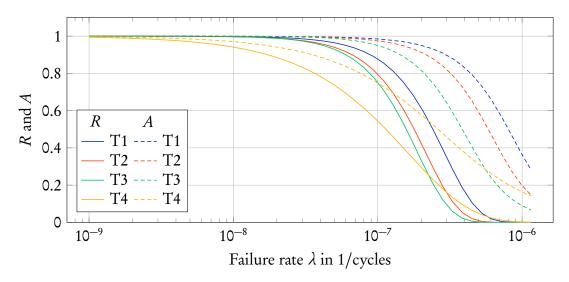

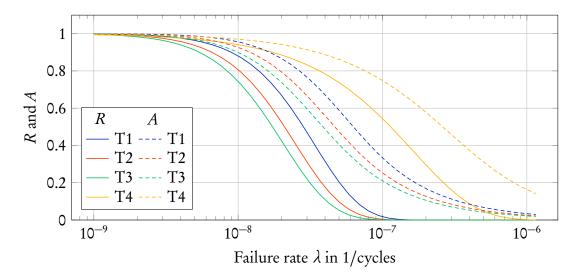

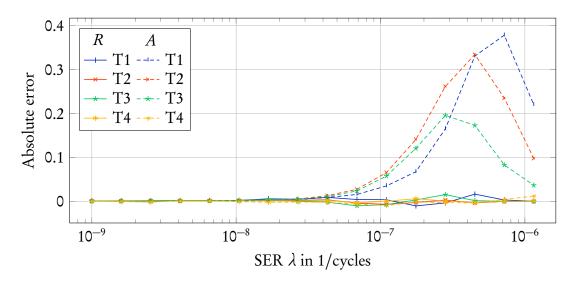

|   | 6.3  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 93               |