## Data Processing on Heterogeneous Hardware

vorgelegt von

### Max Heimel, M.Sc.

geboren in Heidelberg, Deutschland

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

### Doktor der Naturwissenschaften

— Dr. rer. nat. —

genehmigte Dissertation

### Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. Stefan Tai Gutachter: Prof. Dr. Volker Markl

> Prof. Dr. Jens Teubner Prof. Sam Madden, PhD

Tag der wissenschaftlichen Aussprache: 8. Januar 2018

Bullshit ... is everywhere.

— Jon Stewart, in his final Daily Show

### Zusammenfassung

Der Bereich der Datenbankforschung auf moderner Hardware beschäftigt sich mit der Frage, wie wir neuartige Hardware effizient zur Datenverarbeitung einsetzen können. Forscher und Entwickler haben hierzu in den letzten Jahren wichtige Beiträge geleistet und Ansätze sowie Systeme zur Datenverarbeitung auf verschiedensten Kategorien von Prozessoren vorgestellt. Ein wichtiger Aspekt wurde dabei jedoch häufig übergangen: Obwohl wir heute sehr gut mit einzelnen (oder mehreren) Prozessoren der selben Art umgehen können, ist es noch relativ unklar, wie ein Datenbanksystem entworfen werden sollte, das auch verschiedene Prozessoren effizient verwenden kann. Dieses Problem der Hardwareheterogenität wird zunehmend relevant: Bereits heute verfügen Computer häufig über eine Vielzahl von verschiedenen Prozessoren, wie zum Beispiel CPUs, Grafikkarten, FPGAs oder Vektorprozessoren. Experten sind sich einig, dass diese Vielfalt weiter anwachsen wird, und dass wir auf dem Weg in ein neues Zeitalter der Heterogenität sind. Um mit den wachsenden Anforderungen der modernen Informationsgesellschaft Schritt zu halten, wird es daher zunehmend wichtig werden, dass wir neuartige Verfahren entwickeln um Hardwareheterogenität in Datenbanksystemen ausnutzen und verwalten zu können.

In dieser Arbeit stellen wir unsere Forschungsbeiträge zu diesem Bereich vor. Dies umfasst insbesondere die folgenden zwei Themen:

- 1. Im ersten Teil dieser Arbeit besprechen wir Ansätze zur Verwaltung von Hardwareheterogenität in Datenbanksystemen. Insbesondere führen wir das Konzept von hardwareunabhängigen Datenbankoperatoren ein. Dies zielt darauf ab, den Entwicklungsaufwand zu reduzieren, der normalerweise bei der Portierung eines Datenbanksystems auf eine neue Hardwarearchitektur anfällt: Anstelle von speziell angepassten Algorithmen werden hierbei abstrakte Operatordefinitionen verwendet, welche vom System erst zur Laufzeit automatisch auf die vorhandene Hardware abgebildet werden. Zudem stellen wir mit Ocelot ein protoypisches System vor um die Machbarkeit des Konzepts hardwareunabhängiger Datenbanken zu belegen.

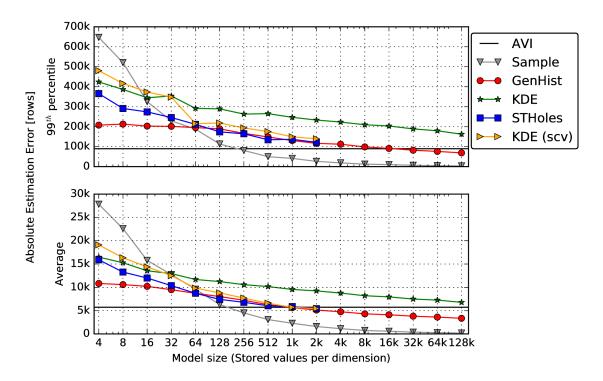

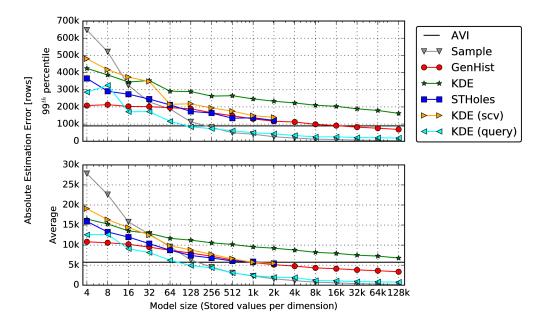

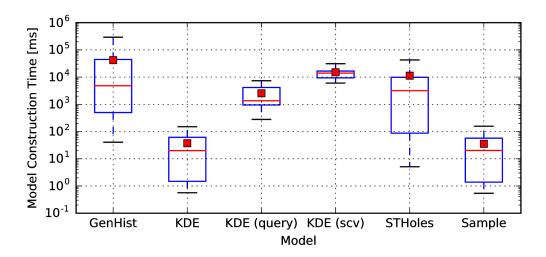

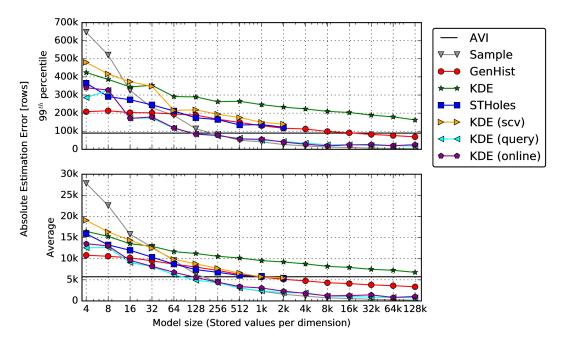

- 2. Im zweiten Teil der Arbeit führen wir mit GPU-unterstützter Anfrageoptimierung einen neuen Ansatz zur Verwendung von heterogener Hardware in Datenbanksystemen ein. Hierauf aufbauend stellen wir anschließend einen sich selbst optimierenden, multivariaten Selektivitätsschätzer vor, welcher von uns speziell an die Eigenschaften moderner Grafikkarten und CPUs angepasst wurde. Der Schätzer ist hochskalierbar, passt sich selbstständig an Änderungen der Datenbank und Anfragen an und erzielt eine Genauigkeit, die in der Regel deutlich über dem aktuellen Stand der Technik liegt.

Für beide Themen leiten wir eine ausführliche Motivation her, präsentieren und diskutieren die Ergebnisse unserer experimentellen Auswertung, stellen unsere Quelltexte und Skripte zur Verfügung um es anderen Autoren zu ermöglichen, unsere Ergebnisse nachzuvollziehen, und skizzieren mögliche Themen und Richtungen für anschließende Forschungsarbeiten.

### Abstract

The primary objective of data processing research on modern hardware is to understand how to utilize emerging technology to process data efficiently. Over the last decades, Software Engineers and Computer Scientists have made significant progress towards this goal, providing highly-tuned algorithms, systems & mechanisms for a wide variety of different device types. However, while we mostly understand how to exploit multiple identical devices, the question of how to build database engines that can deal with a diverse number of them remains open. Already today, with multi-core CPUs, graphics cards, FPGAs, and vector processors, we have access to a staggering variety of different architectures, and experts agree that hardware diversity will continue to grow. As we enter this era of heterogeneity, developing new approaches to deal with a multitude of different hardware architectures is becoming increasingly important. Tomorrow's database systems will need to exploit and embrace this trend towards increased hardware heterogeneity to meet the performance requirements of the modern information society.

In this thesis, we present our contributions to the area of data processing on heterogeneous hardware. In particular, we discuss the following two major topics:

- 1. In the first part of this thesis, we discuss how to manage hardware heterogeneity by reducing the development overhead to implement a database engine that can run on different hardware architectures. For this, we propose an alternative system design, based on a single set of hardware-oblivious operators which are compiled down to the actual hardware at runtime. Relying on hardware abstraction, learning mechanisms and self-tuning algorithms, this approach can drastically reduce the enormous development overhead that typically comes with supporting a variety of architectures, while still achieving competitive performance to hand-tuned code. We also present Ocelot, a prototypical hardware-oblivious database engine to demonstrate the feasibility of this concept.

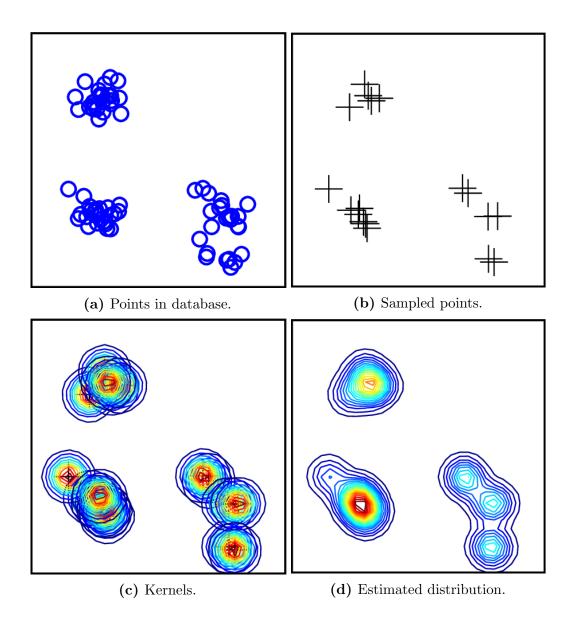

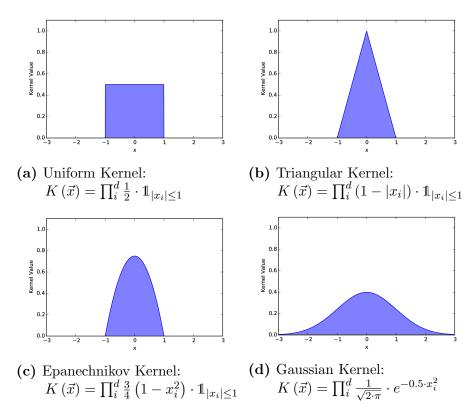

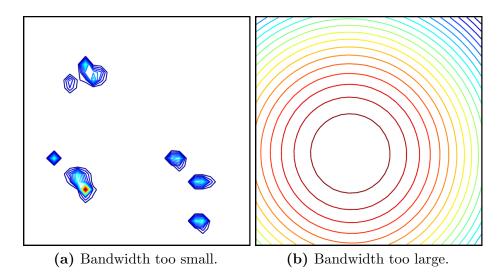

- 2. In the second part of this thesis, we introduce a novel approach to exploit hardware heterogeneity in a relational database engine by utilizing graphics processing units to assist the query optimizer. Based on this idea of *GPU-Assisted Query Optimization*, we then introduce a self-tuning, multivariate selectivity estimator based on *Kernel Density Estimation* that is specifically designed to exploit the properties of modern graphics cards and multi-core CPUs. This approach enables us to develop a novel estimator that is highly scalable, that can adapt itself to changes in both the database and the query workload, and that can typically outperform the accuracy of established state-of-the-art methods.

For both topics, we motivate our decisions, present and discuss experimental evaluations, provide both the source code and scripts to allow other authors to reproduce our results, and outline potential directions for future work.

## Contents

| 1 | A Short History of Integrated Circuits                                                                                                                                                                                                                                                           |                      |  |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| 2 | Tackling Heterogeneity: The Whys, The Whats, and The Hows                                                                                                                                                                                                                                        |                      |  |  |  |

| 3 | Managing Heterogeneity: Hardware-Oblivious Database Engines 3.1 Introduction: The Development Bottleneck of Heterogeneous Hardware 3.2 Background: OpenCL & The Kernel Programming Model 3.3 Ocelot — A Hardware-Oblivious Database Engine 3.4 Closing the Performance Gap 3.5 Summary & Outlook | . 20<br>. 25<br>. 35 |  |  |  |

| 4 | Exploiting Heterogeneity: GPU-Assisted Selectivity Estimation 4.1 Introduction: GPU-Assisted Query Optimization                                                                                                                                                                                  | . 58<br>. 73<br>. 84 |  |  |  |

| 5 | The Road Ahead: Conclusion & Future Work                                                                                                                                                                                                                                                         | 99                   |  |  |  |

## Chapter 1

# A Short History of Integrated Circuits

On April 19<sup>th</sup>, 1965 *Gordon Moore*, the director of research and development at Fairfield Semiconductors, published an article for the 35<sup>th</sup>-anniversary issue of *Electronics* magazine. In this article, he laid out his predictions for the future of the semiconductor industry, which back then was still in its infancy but started to show signs of rapid growth. The following observation was the centerpiece of this article:

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year. Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years [Moo65].

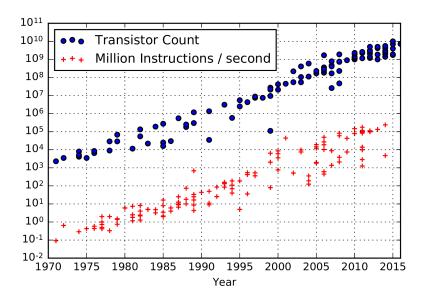

Back in 1965, no one anticipated that this observation would become one of the most influential and well-known technical statements of the modern world. Even Moore himself, who had just wanted to bring attention to an interesting local trend in the semiconductor business, later admitted to being amazed by the correctness and impact of his prediction [M<sup>+</sup>11]. Today, more than fifty years after its original publication, the common interpretation of *Moore's Law* is that it is predicting a doubling of the number of transistors in integrated circuits every eighteen months. And — as we can see in Figure 1.1 —, the industry followed this prediction like clockwork. For the past fifty years, Moore's Law has been one of the primary drivers behind the ongoing digital revolution, and — in a way — it has even become a self-fulfilling prophecy, motivating engineers and scientists to continuously push for innovations, technological advances, and manufacturing improvements.

A typical misconception about Moore's Law is that it also predicts a doubling of the chip performance<sup>1</sup>. Looking back at Figure 1.1, we can see where this belief came from: The compute performance of integrated circuits, measured in instructions per second, has indeed been growing at a similar exponential pace as the number of transistors. Moore himself tried to explain this somewhat non-obvious correlation for a 1975 IEEE bulletin article in which he identified three primary factors that enabled

<sup>&</sup>lt;sup>1</sup>While inspired by Moore's Law, this prediction was actually made by an Intel executive named David House in 1975.

Figure 1.1: Development of the number of transistors and instructions per second in commercially available integrated circuits since the 1970s. Data was taken from en.wikipedia.org/wiki/transistor\_count and en.wikipedia.org/wiki/instructions\_per\_second. Note the logarithmic y-axis.

the ongoing increase in transistor counts [Moo75]: Increased chip sizes, improved chip designs that reduce unused real-estate, and shrinking transistor sizes. Out of these three, he identified the last one as the most important factor to explain the ongoing exponential increases in compute performance.

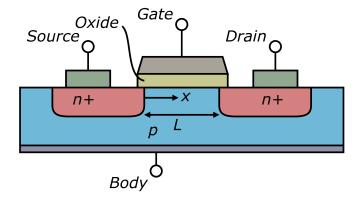

Figure 1.2 shows the schematics of a modern Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET), which is the base technology behind virtually all modern integrated circuits. MOSFET-style transistors exploit the electrical field created by a voltage between the Gate and the Source to control a conducting channel in the underlying semiconductor substrate that allows a current to flow from the Source to the Drain. As shown in Figure 1.2, MOSFET-style transistors have a planar layout, consisting of layers of differently doped semiconductor materials within

**Figure 1.2:** Simplified schematic of a (n-type) MOSFET transistor. Picture Lateral mosfet by Cyril Buttay is licensed under CC BY-SA 3.0.

an underlying substrate. This design allowed manufacturers to produce integrated circuits in an efficient mass process that essentially prints the individual layers of the transistors onto the underlying substrate [Kae08]. Over the last fifty years, manufacturers continuously improved the accuracy of this process, enabling the production of dramatically smaller transistors. In particular, they were able to reduce the gate length — which is the distance between the transistor's Source and Drain — by several orders of magnitude, coming from 10 µm in the early 1970s down to 10 nm as of 2016. Now, interestingly, reducing the gate length of a MOSFET-style transistor has some non-obvious benefits besides just enabling higher transistor densities. In particular — as was described in 1974 by Robert Dennard, an IBM researcher on integrated circuit design —, reducing the gate length by a factor of  $\lambda$  reduces both the voltage required to control the transistor and the time the transistor needs to react to voltage changes by the same factor [DGY<sup>+</sup>74]. In other words, shrinking transistors to half their size allowed manufacturers to build integrated circuits that were twice as complex while staying within the same power and real-estate budgets.

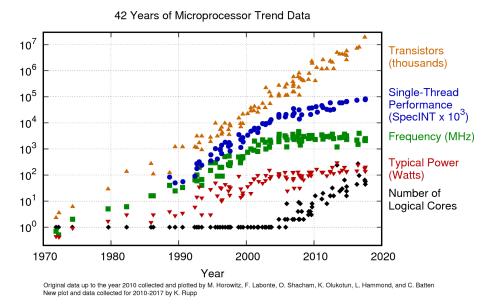

This Dennard Scaling effect was a godsend for the IT industry in general, and the semiconductor industry in particular: With each new generation of transistors, processors almost automatically<sup>2</sup> got faster and more versatile without requiring more power or larger — and thus more expensive — chip sizes. As can be seen in Figure 1.3, this development resulted in an ongoing exponential increase of both single-core performance and clock frequencies. This development was a massive driver behind the growth of the IT industry, given that software developers could rely on new CPU generations continuously bringing extensive improvements to the available compute power and thus enabling applications that had been unthinkable just a few years earlier. But, like Q once said: "All good things must come to an end," and after more than thirty years of driving the digital revolution, the "golden age of scaling" eventually came to an end in the early 2000s, with clock frequencies apparently hitting a wall at around 3 GHz.

So, what happened? Essentially, what we are observing since the early 2000s is the break-down of Dennard Scaling: As transistors continued to shrink, they eventually reached dimensions where fundamental physical limitations took over and prohibited manufacturers from continuing to scale voltages and clock rates. The primary example for this breakdown is the exponential increase in *subthreshold leakage* across the transistor's shrinking gate. A great way to visualize this effect is to imagine a big river that people want to cross, and the only way for them to do so is via a retractable drawbridge. Opening and closing the bridge takes time, so there is an upper bound on how often the bridge can be operated in a day. Now, if the river dries up and becomes thinner, a shorter and lighter bridge could be built as a replacement. This smaller bridge is quicker to open and close, and thus can be operated more frequently. An analogous effect occurs when we shrink a MOSFET-style transistor: As the gate gets smaller, the threshold voltage required to open the conducting channel drops, allowing us to drive the transistor at a higher frequency. However, if the river continues to dry up, we will eventually reach a point where athletic people could

<sup>&</sup>lt;sup>2</sup>This is obviously a simplification: Manufacturers also managed to dramatically improve performance by continuously improving their microarchitectures, for instance through performance-critical features like superscalar instruction pipelining, out-of-order execution, SIMD instruction sets, and increasingly smarter caching and prefetching architectures.

Figure 1.3: Forty-two years of processor trends. Illustration by Karl Rupp [Rup18].

simply jump across it, bypassing the bridge altogether. And the thinner the river becomes, the more people will be physically capable of doing so. This effect also occurs in transistors: Thinner gate lengths and lower threshold potentials make it easier for high-energy electrons to punch through the closed gate, creating a leaking current. This ssubthreshold leakage is inversely exponentially proportional to the threshold voltage, meaning that the smaller a transistor becomes, the more power it evaporates due to leaking currents [KAB+03]. Ultimately, this growing power leakage forced manufacturers to start controlling the threshold voltage of their transistors, relying on design changes, manufacturing improvements, and revised semiconductor materials to stop it from dropping further. And, since voltage and frequency are closely related to each other, this development also meant that the time of growing clock frequencies had come to an end<sup>3</sup> [MF95].

The end of Dennard Scaling marks a significant inflection point in the history of integrated circuit design. With clock frequencies topping out, manufacturers could no longer rely on their most crucial performance driver. Instead, single-thread performance now had to come from architectural improvements like increasing the instructions per cycle through better pipelining, prefetching & branch prediction mechanisms, adding specialized instruction sets to accelerate common operations, or growing and improving the caching infrastructure. And while these measures did indeed help to keep improving performance, they were also much more work- and time-intensive to implement and typically resulted in smaller improvements than frequency scaling did. Figure 1.3 shows the effects of these developments: Starting from the mid-2000s, we can see both the flattening-out of clock frequencies as well as a drop in the growth rate of single-thread performance. At the same time, we can also see an increase in the number of logical cores per processor: With single-thread performance growing much slower than required, manufacturers began to

<sup>&</sup>lt;sup>3</sup>This is, again, somewhat simplified: While subthreshold leakage has indeed played a fundamental role in the end of Dennard Scaling, there were also many other technical reasons at play. For a good overview, the interested reader is referred to the following two excellent articles by Intel Senior Fellow Mark Bohr: [Boh07, BCGM07].

focus on spending the still increasing number of transistors on parallelization to satisfy the ever-growing demand for compute performance. And thus, fueled by the end of Dennard Scaling, began the era of multi-core processors [Gee05].

Increasing the number of instructions that processors can run in parallel, be it through multi-core designs, through simultaneous multi-threading (SMT) technologies like Intel's HyperThreading, or through SIMD instruction sets like SSE or AVX, quickly became the go-to solution for Post-Dennard performance scaling [Gee05, BC11]. For a practical example of this development, let us take a look at IBM's POWER line of server processors. After struggling with their old design to keep power consumption in check with growing frequencies, IBM decided in 2010 to move to a new multi-core design that favored parallelization and power efficiency over single-thread performance. POWER7, the first chip from this new line, was released in 2010 and offered an eight-core processor, with each core supporting four-way SMT, making the chip capable of running 32 hardware threads simultaneously [SKS+11]. Its successor, POWER8, was released in 2014 and featured twelve eight-way SMT cores [SVNE+15]. And POWER9, the next chip generation as of the writing of this thesis, will be released in 2017 and will feature 24 eight-way SMT cores, bringing the number of hardware threads up to 192. While parallelism grew by a factor of six in the seven years between POWER7 and POWER9, single-thread performance only improved by around a factor of two [SVNE+15]. In other words, IBM only managed to meet the expectation of doubling chip performance every 18 to 24 months by exploiting multi-core scaling and other forms of parallelism.

Initially, manufacturers focused on building parallel processors that followed the socalled symmetric multiprocessor (SMP) design pattern, meaning that they combined multiple identical processor cores, typically with a shared infrastructure for memory access and caching. This design has the advantage of being relatively easy to scale through "copy & paste", which enabled the rapid increase in the number of available cores since the mid-2000s. However, there are some fundamental limitations to the scalability of SMP designs. First of all, there is Amdahl's Law, which states that the achievable speedup through parallelization for any given task is bound by its serial portion [Amd67]. In other words, for most real-world applications the usefulness of SMP processors with ultra-high numbers of cores is inherently limited [HM08, WL08, Mar12, YMG14]<sup>4</sup>. Second, as the number of cores grows, so does the portion of the chip that is required for interconnect and synchronization mechanisms. For larger multi-core designs, the size and power requirements for these parts is already significant and poses a clear engineering barrier to scaling SMP designs towards a higher number of cores [KZT05]. And finally, last but certainly not least, there is the so-called *Power Wall*.

The term "Power Wall" refers to the increasing amount of power and cooling that large chip designs require. According to Moore's Law, the number of transistors, and thus power consumers, per processor still keeps doubling every 18 to 24 months. Without improving the efficiency of individual transistors at a similar pace, this growing number causes the processor to require more and more power. Historically, Dennard Scaling allowed manufacturers to keep this from happening since the power consumption of individual transistors shrank proportional to their area [DGY<sup>+</sup>74].

<sup>&</sup>lt;sup>4</sup>It should be noted that this argument is only strictly true for fixed workloads [SC10].

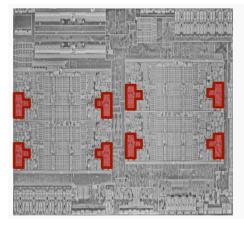

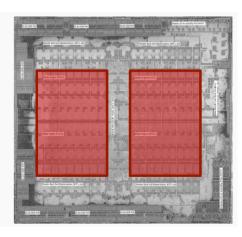

**Figure 1.4:** Comparing the chip layouts of a modern eight-core CPU (left, AMD Ryzen 7) and a modern GPU (right, AMD Radeon RX 480). Areas of the chip that are used to run instructions are highlighted in red.

However, today, this is no longer the case: While the power efficiency is still improving, it does so at a much slower pace than the growth in transistor counts would warrant [HP11]. This trend increasingly forces manufactureres to limit the number of transistors that can be active at the same time to control the overall power consumption of their processors – an effect that is also called *Dark Silicon*. On average, for an integrated circuit that is manufactured using the current 22 nm process, around 20% of its transistors must be powered off at any given time. Moreover, for the upcoming 8 nm process, this fraction is expected to increase to almost 50% [EBA+11], making it imperative to react.

It should be clear that SMP designs are inherently incompatible with Dark Silicon: There is little point in packaging more and more identical cores if we are limited to using only a fraction of them at the same time [Mär14]. Because of this, manufacturers are increasingly turning towards heterogeneity and specialization as design dimensions to improve chip performance [CMHM10, BC11, ZPFH13]. Graphics processing units (GPUs) are probably the best-known example for such specialized cores. They were originally introduced in the early 1990s as fixed integrated circuits to accelerate the rendering of 3D graphics. Over time, fueled by the growing demand for more sophisticated visuals, manufacturers evolved these fixed circuits into fully programmable, massively parallel SIMD-style cores, whose peak computational performance is orders of magnitude higher than that of comparable CPUs. Figure 1.4 illustrates how this is possible: Modern CPUs spend billions of transistors on caches, branch prediction logic, pipelining, prefetching, and further complex support logic that is not directly evaluating instructions. Modern GPUs, on the other hand, use a much larger fraction of their transistors to actually run instructions by stripping down support logic to the bare minimum and packaging as many parallel SIMD units as possible. These architectural differences lead to CPUs and GPUs being optimal for different types of problems: While CPUs are designed to run complex, single-threaded code with various conditional branches, GPUs achieve their peak performance on embarrassingly parallel problems whose individual computations are comparably simple [LKC<sup>+</sup>10]. By packaging both types of cores, the processor can selectively choose the one that best fits the current workload [Tay13]. Various

authors have demonstrated that such heterogeneous designs that exploit specialized cores can be both faster and more energy-efficient than homogeneous SMP multi-core chips, in particular when considering the constraints imposed by Dark Silicon [HM08, WL08, Mar12, VT14].

Today, virtually all major hardware manufacturers are either working on or are already offering heterogeneous processor architectures: AMD is aggressively pushing coupled CPU-GPU designs through its *Heterogeneous System Architecture* [Kyr12]. Intel is moving to integrate FPGA technology into their Xeon line of server processors to allow customers to configure highly specialized circuitry at runtime [SH16]. Samsung and Qualcomm are building heterogeneous *systems-on-a-chip* based on ARM's *big.LITTLE* architecture that incorporates cores of different sizes and shapes to offer flexible and power-efficient performance scaling on mobile and embedded devices [MWK<sup>+</sup>06, Gre11]. IBM is introducing its *coherent accelerator processor interface (CAPI)*, which allows external accelerators to seamlessly integrate with the latest Power8 server processor [SBJS15]. Moreover, besides the trend towards increasingly heterogeneous processors, there is also a growing number of specialized external accelerator cards like Nvidia's GPU-derived *Tesla* series [LNOM08] or Intel's massively parallel *Xeon Phi* co-processors [Chr14].

So, how will the future of microprocessor designs look like, and how will their evolution affect us as Software Engineers and Computer Scientists? Experts agree that we are just witnessing the beginning of a whole era of heterogeneity, and that future processor architectures will become increasingly diverse [Boh11, BC11, ZPFH13, Mär14]. And similar to how the emergence of multi-core architectures forced us to revisit established design patterns and to begin relying on threads & parallelization, this development will have a profound effect on the way we think about developing software. With hardware becoming increasingly diverse, it will become vital for software not merely to tolerate heterogeneity but to be actively able to exploit the advantages and disadvantages of a wide variety of different processors [BRUL05]. Just like Nobel laureate Bob Dylan once said: "The times they are a-changin'," and finding the novel programming paradigms, design strategies, and best practices to build heterogeneity-aware software efficiently will soon be one of the primary challenges for Software Engineers and Computer Scientists. If we want to stay ahead of the curve and be ready to meet the ever-growing demand for efficient and ubiquitous computing that the modern information society requires, we will have to react to the changes caused by increasing hardware heterogeneity.

7

## Chapter 2

# Tackling Heterogeneity: The Whys, The Whats, and The Hows

In this thesis, we will cover a small aspect of the overall problem of how to design heterogeneity-aware software. In particular, we will discuss the question of how the trend towards increased hardware heterogeneity affects the field of relational database systems, and present our research into how we as database researchers and practitioners could react to this development. Originally introduced by E.F. Codd in the early 1970s as a sound mathematical way to express and query data based on the relational algebra [Cod70], the relational model has become one of the most influential technological developments of the 20<sup>th</sup> century. Today, relational database systems like Oracle, SQL Server, Postgres, MySQL or DB2 are a fundamental cornerstone of the modern information society. Virtually all fields — including Medicine, Finance, Manufacturing, Logistics, Telecommunication, Science, and Military — rely on relational databases to store, organize, query, process & analyze the massive amounts of data that the modern information society produces and requires to operate.

Because of their interdisciplinary importance, improving the performance of relational database systems has always been a topic of great interest. From early on, the research literature on database systems has presented specific algorithms, adaptations, and design considerations to avoid resource bottlenecks. Traditionally, this work has focused primarily on reducing the impact of disk operations, with CPU efficiency being considered more of an afterthought: Constrained by main memory sizes that were far too small to store any significant amounts of data, ancestral relational database systems like System R [ABC<sup>+</sup>76] or Ingres [HSW75] and their successors were naturally designed based on the assumption of disk-IOs being the dominant performance factor. This led to the development of several sophisticated technologies to efficiently utilize the disk and to effectively mask IO latencies, including the B-Tree index structure [BM72, Com79], the Hybrid Hash Join algorithm [DKO<sup>+</sup>84], the Volcano tuple-at-a-time query execution model [Gra94], and the ARIES transaction management method [MHL<sup>+</sup>92]. For an excellent overview of some of these fundamental database technologies, many of which are still used by modern systems today, we refer the interested reader to the 1993 survey paper by Graefe [Gra93].

Things started to change around the turn of the millennium when growing main memory sizes and increasing customer demand for compute-intensive analytical workloads brought the CPU-efficiency of databases into the limelight. As it turned out, the disk-optimized system architectures, query execution models, and data processing algorithms of the 1980s and 1990s often caused severe performance problems when they were used to process memory-resident data on newer processors [SKN94, BMK<sup>+</sup>99, ADHW99. Spurred by this discovery, researchers began to rethink key design aspects of traditional database architectures with a primary focus on improving CPU efficiency and reducing memory latencies. This led to several important developments, including the increased reliance on cache-efficient columnar (or semi-columnar) data storage layouts [CK85, BMK<sup>+</sup>99, ADHS01, SAB<sup>+</sup>05, AMH08, ABH09], the move towards CPU-efficient query execution models like column-at-a-time [BMK<sup>+</sup>99], vectorat-a-time [BZN05], or query compilation [KVC10, Neu11, Vig14a], as well as the development of novel lightweight transaction and isolation mechanisms [LBD<sup>+</sup>11, KN11]. For further information on the topic of in-memory data processing, we refer to Zhang et al., who prepared a great survey paper that provides an overview of some of these developments [ $ZCO^{+}15$ ].

Today, database performance research that does not take computational efficiency into account would be unthinkable. Accordingly, it should come as no surprise that there is a close relationship between the worlds of integrated circuit design and database performance research. A great example for this relationship is the impact that the end of Dennard Scaling had on the database research community: Before the mid-2000s, research papers that discussed CPU-efficient query processing were primarily focused on improving single-thread performance by optimizing data & instruction cache efficiency [SKN94, ADHW99, RR00, MBK02]. With the end of Dennard Scaling this began to change, as researchers were forced to branch out into novel topics like exploiting SIMD vectorization [ZR02, JRSS08, WPB+09, KCS+10], relying on lock-free data processing algorithms and data structures [Mic02, LBD+11, Hor13, TZK+13], or using multi-core parallelization [CNL+08, KKL+09, KKG+11, BLP11, AKN12, BATÖ13]. Obviously, this close relationship also meant that the database community did not ignore the move towards increasingly heterogeneous hardware. In fact, looking through the last decade of literature on query processing on specialized hardware<sup>1</sup>, we can find articles that discuss how to write efficient data processing algorithms for virtually any available processor architecture. This includes graphics cards [GLW+04, GGKM06, HYF+08, HLY+09, BS10, HY11, DWLW12, KLMV12, SR13, BAM13, Bre14, HZH14, PMK14, WDS+14, WZY+14, KML15, runtime-configurable circuits like FPGAs [MTA09, KT11, MT10, MTA10, MTA12, TW13, WCP<sup>+</sup>16], vector processors [HNZB07, BF10, JHL<sup>+</sup>15, PMS15], heterogeneous CPUs [CR07, HLH13, KHSL13, MRS+14], and even network processing equipment [GAHF05, BBHHHO15].

<sup>&</sup>lt;sup>1</sup>Interestingly, this can hardly be called a new research direction: The idea to exploit specialized hardware to accelerate databases has been floating around since almost forty years, often subsumed under the umbrella term of *database machines* [DeW79, Nec83, DGS<sup>+</sup>90]. However, despite impressive technical achievements, the idea of database machines never really took off: Back when Dennard Scaling still reliably delivered exponentially growing compute performance every two years, it simply made much more economic sense to wait for the next generation of general-purpose CPUs than to invest in expensive specialized hardware [BD83].

Now, if we already know how to process data on most modern processor architectures efficiently, then why do we feel that the topic of databases on heterogeneous hardware still warrants further discussion? Essentially, this boils down to one major point: While we do know how to accelerate individual operators on selected processors, we do not yet fully understand how the increasing hardware heterogeneity should affect database architectures themselves. In a way, the situation is similar to when growing memory sizes forced us to redesign the traditional disk-based architectures of the 1980s and 90s: With hardware becoming increasingly heterogeneous, we are facing the question of how to adapt existing database technology to a world where the assumption of having a single processor type does not hold anymore. And this goes far beyond "simply" porting database operators to multiple different processors. In fact, this is a fascinating research problem that spans several areas and includes topics such as improved data and operator placement mechanisms, adapted query execution models, novel co-processing strategies, query optimizers that take hardware heterogeneity into account, as well as operator programming models to reduce development overheads. Also, we are not the only ones who think this way: Heterogeneity-aware databases are currently under heavy investigation, and several of our colleagues, including — in no particular order and without any claim to completeness — Sebastian Breß, David Broneske, Bingshen He, Tomas Karnagel, Holger Pirk, Hannes Rauhe, Kaibo Wang, Haicheng Wu, Yuan Yuan, Steffen Zeuch, and Shuhao Zhang have all made significant contributions to this field.

This is the basic context of this thesis. In the following chapters, we will discuss the following two selected problems that derive from the fundamental question of how to design a heterogeneity-aware database system:

## 1. How can we manage the development overhead incurred by increased hardware heterogeneity in a relational database system?

One of the primary challenges of building heterogeneity-aware database systems is how to deal with the development and maintenance overhead that is caused by hardware-specific code paths: Since most processor architectures require, at the very least, specific code adjustments or — in the worst case — even a complete redesign of several core components, supporting highly heterogeneous hardware typically causes a severe explosion of code volume and complexity. From an economic point of view, this means that adding support for a new processor architecture comes with a hefty price tag. Accordingly, vendors are usually slow to embrace modern hardware, as can be seen from the lagging commercial adoption of GPU-accelerated databases. This makes managing code complexity and reducing development costs one of the primary research goals on the way to enabling databases that can genuinely exploit heterogeneous hardware.

In Chapter 3, we discuss this problem in the context of relational database systems. The general idea behind our presented approach is to rely on a hardware-oblivious programming model that allows developers to specify relational operators on an abstract level without having to fine-tune them to the underlying hardware manually. At runtime, a hardware-conscious runtime component then maps this abstract operator code to the underlying hardware. By offloading as much of the hardware-specific adaptations as possible to an automated system, this approach can dramatically reduce the development and maintenance over-

11

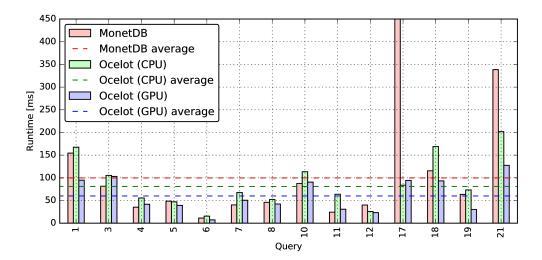

head for building a heterogeneity-aware database system. We demonstrate the general feasibility of this approach via a prototypical execution engine called *Ocelot* that uses *OpenCL* as its hardware-oblivious programming model and vendor-provided drivers as its runtime component. Despite only having a single implementation of the relational operators at its disposal, Ocelot still manages to achieve competitive performance compared to state-of-the-art systems on both CPUs and GPUs.

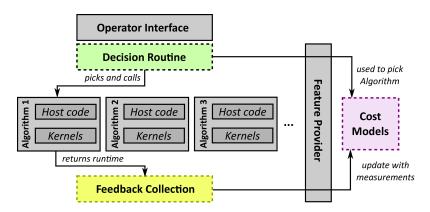

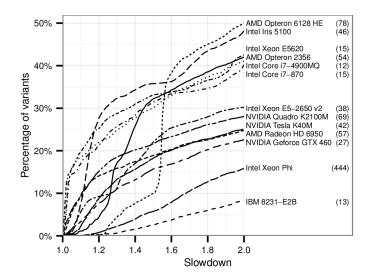

Now, sadly, abstraction seldom comes without regret, and there will always be a performance gap between hardware-oblivious and hand-tuned operator implementations. The question of feasibility is just how significant this gap is in relation to the achieved reduction in development overhead. To further close this gap, we then present two methods to adapt the operator implementations automatically at runtime. The first method relies on self-learning cost models to select the optimal algorithm to implement a given operator on the current hardware architecture. The second method, *variant tuning*, uses probabilistic methods to fine-tune the operator implementations based on collected performance feedback.

## 2. Besides query processing, what are useful ways to exploit heterogeneous processing hardware in a relational database system?

As we have seen, the database literature is filled with publications that discuss highly optimized data processing algorithms for almost any available processor architecture. One of the most active research areas from this field is GPU-accelerated data processing, which has been under investigation for more than a decade [GLW+04, BHS+14b]. However, despite this ongoing research interest, and despite several publications demonstrating clear benefits of using GPU acceleration, there has been surprisingly little commercial adoption. As it turns out, it is relatively challenging to achieve consistent performance improvements from using GPUs for SQL workloads: Small device memory sizes, expensive data transfers, high operational latencies, and limited applicability to transactional workloads, make it challenging to exploit their potential.

Because of these limitations, it is not necessarily clear that general-purpose query processing is the optimal way to exploit graphics cards in a database system. Several authors have suggested alternative applications for graphics cards that are not directly related to query processing and do not suffer from these problems, including data visualization [GKV05], data exploration [HH15], or approximate query answering [GRM05]. One example of such an alternative application that also benefits general-purpose query processing is the bitwise decomposition method introduced by Pirk et al. [PMK14]. In a nutshell, this method stores a low-resolution copy of the data on a graphics card and uses it to support the main query execution engine on the CPU, for instance by quickly filtering out rows that are irrelevant for the query result.

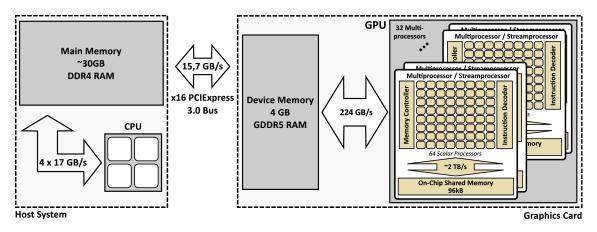

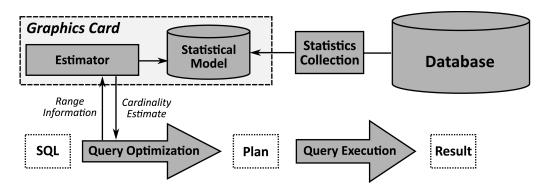

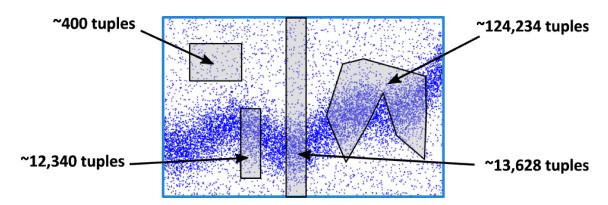

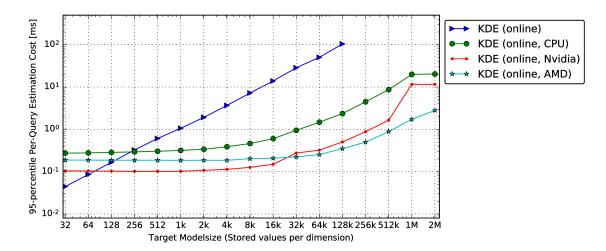

In Chapter 4, we present a method that similarly applies graphics cards in a supporting role by using them as statistical co-processors to assist the query optimizer. Relational query optimizers require accurate estimates of intermediate result cardinalities to construct optimal plans. By exploiting the massive raw computational power of graphics cards for this estimation process, we can use more

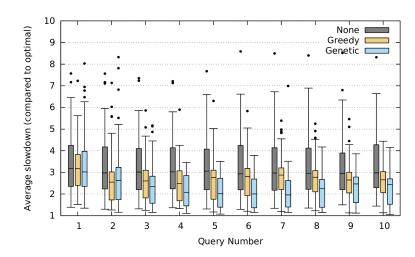

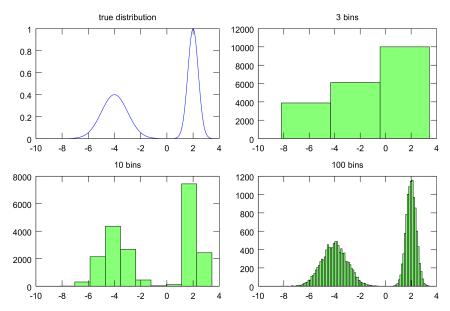

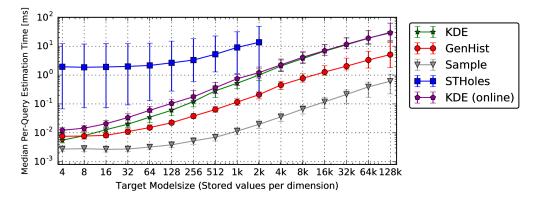

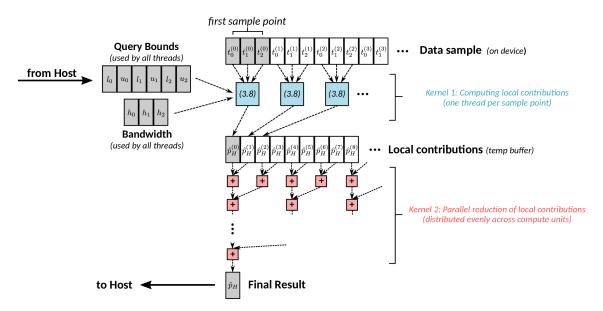

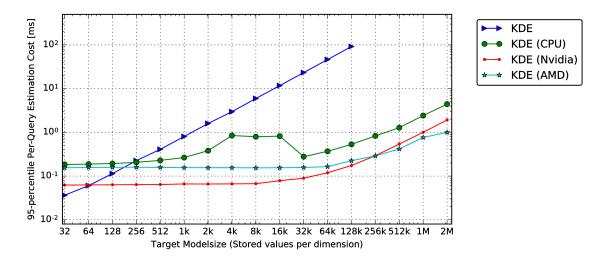

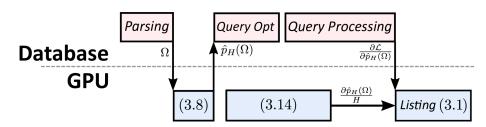

complex methods that produce more accurate results. Since better estimates often lead to improved — and thus faster — plans [Chr84, IC91, RH05, LGM+15], this approach can indirectly accelerate most SQL workloads while avoiding the typical pitfalls of GPU-accelerated query processing. Based on this general idea, we then introduce a novel selectivity estimator based on *Kernel Density Estimation* that is specifically designed to exploit the massive parallelism found on modern GPUs and multi-core CPUs. By doing so, we arrive at an estimator that is highly scalable, that can adapt itself to changes in both the database and the query workload, and that typically outperforms the accuracy of state-of-the-art methods by up to a few orders of magnitude.

Finally, it should be noted that we do not claim to fully answer these two questions, or for that matter, that we even come close to doing so. Solving the problem of building a genuinely heterogeneity-aware database system is a challenging task that will undoubtedly require the ongoing collaboration of many smart people over the next several years to come. Furthermore, it should be noted that there are several interesting aspects of the overall topic that we did not cover in this thesis. For instance, the question of what impact the diversification of the memory hierarchy, the ongoing maturation of flash storage, and the introduction of various classes of non-volatile memory will have on database architectures [KV08, LMP+08, AAC+10, PWGB13, PGH15, Vig15, ZCD+15], the question of how to optimally choose which processing device should run which operation [HLY+09, BS13, KHH+14, WZY+14, BFT16, KHL17], or the question of how to exploit specialized hardware to improve the energy-efficiency of databases [HSMR09, BBZT14, CHL15, UHK+15]. However, at the very least, we hope that our work has introduced a few novel ideas into the field and that it may spark new research directions and interesting developments.

13

## Chapter 3

## Managing Heterogeneity: Hardware-Oblivious Database Engines

Developing a database engine is an expensive undertaking that requires a significant investment of expertise, workforce, and resources. Accordingly, besides the traditional restrictions due to memory, CPU cycles, IO bandwidth, and power consumption, database designs are also restricted by development and maintenance costs. This restriction is particularly valid for data processing on heterogeneous hardware: Porting an existing engine to a new hardware architecture is a tedious, resource-intensive, and error-prone task that requires a deep understanding of the targeted hardware as well as the fundamentals of data processing. This development overhead can quickly become the primary bottleneck for how many processing architectures a database engine can reasonably support. Tackling the challenge of increased hardware heterogeneity therefore also requires us to simplify and automate the process of porting database operators fundamentally, ideally without incurring severe performance penalties. Developing such mechanisms for abstraction without regret is currently one of the hottest topics in modern database research [ZHHL13, HSP+13, KKRC14, Koc14, BBHS14, AKK+15, CGD+15, PMZM16].

In this chapter, we present our work on exploiting hardware abstraction and self-learning mechanisms to reduce the development & tuning overhead incurred by porting a database to a new processing architecture. In particular, we present *Ocelot*, a prototypical *hardware-oblivious* database that we implemented against *OpenCL*. Ocelot's engine is highly portable, yet achieves competitive performance to hand-tuned code. We then discuss further methods to close the performance gap between hardware-oblivious and hand-tuned operators, including learning cost models for algorithm selection, and automatic *variant tuning* for operator implementations.

This chapter is based in parts on material from the following four publications:

Max Heimel, Michael Saecker, Holger Pirk, Stefan Manegold, Volker Markl

Hardware-Oblivious Parallelism for In-Memory Column Stores [HSP<sup>+</sup>13] In: Proceedings of the 2013 VLDB Conference.

2. Max Heimel, Filip Haase, Martin Meinke, Sebastian Breß, Michael Saecker, Volker Markl

Demonstrating Self-Learning Algorithm Adaptivity in a Hardware-Oblivious Database Engine [HHM+14]

In: Proceedings of the 2014 EDBT Conference.

3. Sebastian Breß, Max Heimel, Michael Saecker, Bastian Köcher, Volker Markl, Gunter Saake

Ocelot/HyPE: Optimized Data Processing on Heterogeneous Hardware [BHS<sup>+</sup>14a] In: Proceedings of the 2014 VLDB Conference.

4. Viktor Rosenfeld, Max Heimel, Christoph Viebig, Volker Markl

The Operator Variant Selection Problem on Heterogeneous Hardware [RHVM15]

In: Proceedings of the 2015 ADMS workshop at VLDB.

## 3.1 Introduction: The Development Bottleneck of Heterogeneous Hardware

Modern relational database engines are sophisticated pieces of software that are finely tuned towards the underlying hardware to achieve optimal performance. This high level of code specialization means that it is typically non-trivial or even outright impossible to port existing database code to a new hardware architecture. In particular, when porting engines to "non-traditional" hardware like graphics cards or FPGAs, substantial changes to the code are often a necessity [HNZB07, HLY+09, MTA09, BHS<sup>+</sup>14b]. Implementing these changes requires vendors to spend a lot of money hiring expert engineers who are knowledgeable in both the intricacies of relational data processing and the targeted hardware, causing a sharp increase in development costs. Furthermore, adding support for new architectures also causes the development process itself to become more complex. For instance, while modern database engines are typically written in C or C++, GPUs have to be programmed using frameworks like CUDA or OpenCL, and FPGAs require developers to use a hardware-design language like VHDL. Finally, there is the problem of having to maintain a new branch of the engine's code for each additional hardware architecture. This causes a massive growth in code volume and design complexity, which directly increases the required maintenance overhead [Zha09]. In other words, it is a massive investment — and also a significant risk — for database vendors to support multiple hardware architectures, in particular when some of them are "non-traditional". This inherent development bottleneck for supporting multiple architectures is a primary reason that is preventing database vendors from fully endorsing heterogeneous hardware [HSP+13, ZHHL13].

In practice, this development bottleneck of heterogeneous hardware forces vendors to pick a primary hardware architecture for which they design their engine. Due to their general-purpose nature and their historical relevance, CPUs are naturally the first choice here. Data processing on CPUs is well-understood, and we know how to run all types of different workload scenarios on them. Unsurprisingly, all of the established database vendors focus on CPUs, with alternative hardware architectures being, at best, investigated in the course of internal research projects. However, while they are usually not a good foundation to build upon for a generalpurpose engine, non-traditional hardware architectures can dramatically improve query performance when used to accelerate specific workload scenarios. For instance, graphics cards are well-suited for analytical (OLAP) workloads that can benefit from their massively parallel, throughput-optimized architectures. FPGAs, on the other hand, are highly beneficial for streaming and latency-critical workloads, where their capability to enable hardware-accelerated deep pipeline parallelism for complex, static data processing tasks becomes crucial [MT10, BHS+14b, CWFH13]. And while these advantages are apparently not incentive enough for established vendors to warrant spending development resources, several smaller companies — including Jedox (www.jedox.com), Kinectica (www.kinectica.com), MapD (www.mapd.com), and Sqream (www.sqream.com) — are filling the niche of special-purpose database systems and data applications that exploit non-traditional hardware. However, by doing so, these companies inherently focus their products on a narrow band of selected workload scenarios that can benefit from their choice of target architecture. Obviously, our ultimate goal should preferably be a "best of both worlds" scenario, where the data processing engine is capable of automatically exploiting all available hardware resources across all types of query workloads. Building such a heterogeneity-aware database engine can be considered as the holy grail of data processing on heterogeneous hardware.

So, how could we approach the task of building a heterogeneity-aware database engine? Due to the inherent complexity of manually identifying which device is optimal for which class of problems, the central component of any such system would always have to be some kind of — and the reader may please excuse the usage of this rather hand-wavy term — "learning heterogeneity-aware runtime". Now, while building such a component is already a monumental task by itself [HLY+09, BHS+14a, BBHS14, RHVM15], let's ignore this and assume for the sake of the argument that we had access to it. The next step would then consist of us having to provide this runtime with efficient implementations of relational operators for all targeted hardware architectures, which is a significant amount of work. Take for instance the original list of operators as suggested by Codd and Chamberlin, which comprises set operations, permutation, projection, join, composition, restriction [Cod70], grouping, aggregation, sorting [CB74, CAE+76], and outer operations [Cod79]. While this is already a sizable number of operators to implement, we would need to provide several more if our engine should support anything resembling modern SQL. For instance, MonetDB [BKM08] requires almost 70 different operators to implement the TPC-H benchmark, which can be considered the bare minimum for reasonable (analytical) SQL support [Tra14]. Furthermore, for real-world scenarios that use more recent SQL constructs, or to exploit modern hybrid engine designs that can operate on data in various formats (row-wise/columnar, compressed/uncompressed), the number of operators we have to provide grows even larger [FKN12].

Even just implementing a single relational operator for a new hardware architecture can already require a lot of work, and the amount of research literature published on this topic is a testament to its difficulty: Over the last 40 years, researchers made considerable efforts to figure out how to efficiently process data stored on disks [SAC<sup>+</sup>79, ME92, Gra93, GLS94], stored in memory [DKO<sup>+</sup>84, GMS92, MBK02, BKM08, LP13, kept in distributed systems [DGS+90, Kos00, ÖV11], on multicore CPUs [ZR02, KKL+09, SKC+10, BLP11, BATÖ13, BTAO13], in heterogeneous (NUMA) memory architectures [AKN12, LPM+13, LBKN14, LLA+15], on graphics cards [HLY<sup>+</sup>09, BS10, DWLW12, KLMV12, BHS<sup>+</sup>14b, KML15], on FP-GAs [MTA09, TM11, MTA12], and on other more exotic architectures [GAHF05, HNZB07, KHSL13, JHL<sup>+</sup>15, PMS15]. Implementing and tuning each of these algorithms for a new hardware architecture is a massively laborious task even for expert database engineers that are familiar with the intricacies of the targeted hardware. Furthermore, since each device comes with its specific quirks and twists, this whole manual tuning and evaluation process has to be largely repeated anytime we want to port an operator to a new architecture. Therefore, even if we had access to a smart runtime component to choose the optimal device for each operation automatically, we would still have to significantly reduce the development overhead for providing this runtime with device-specific operator implementations before we could even think about building a heterogeneity-aware database system.

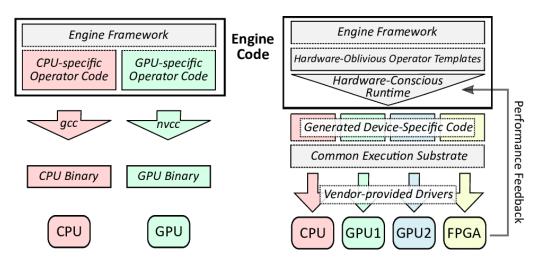

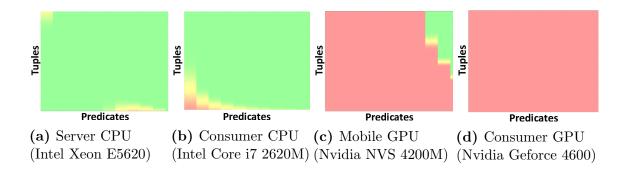

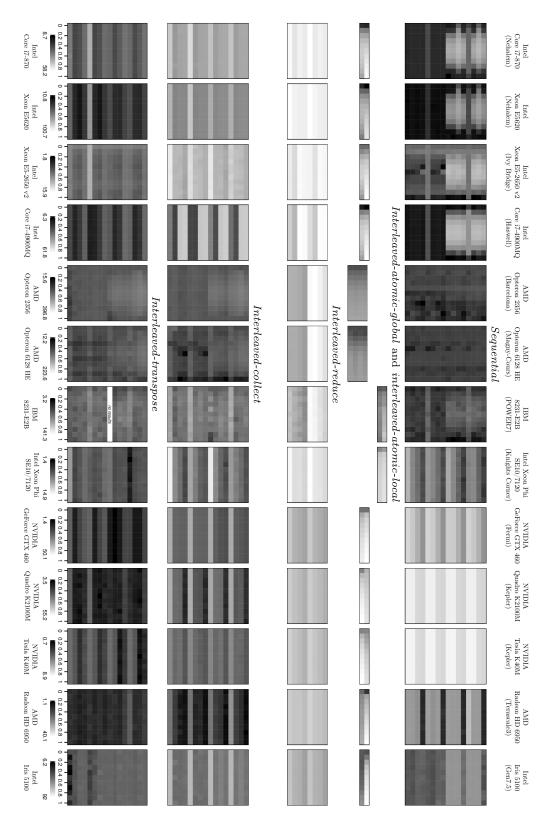

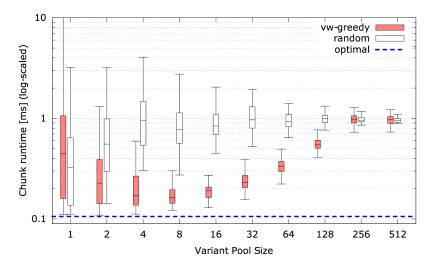

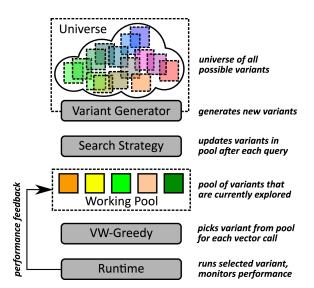

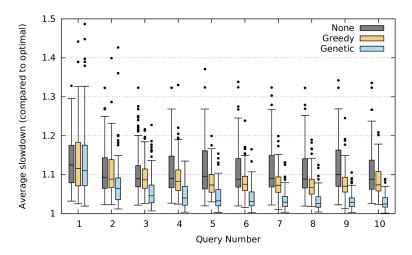

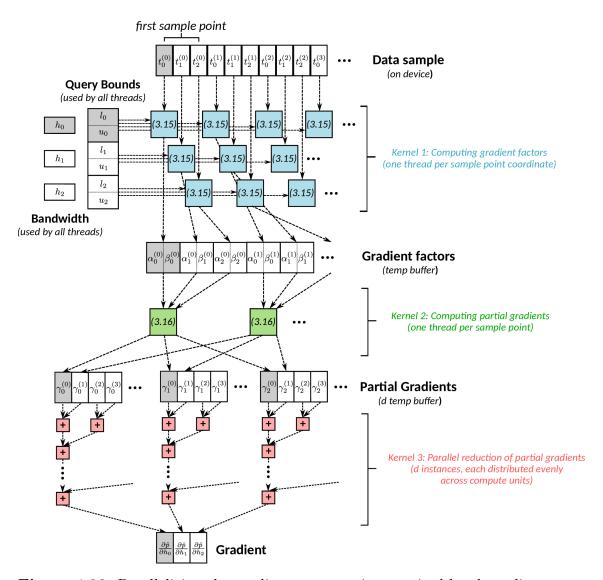

In this chapter, we are discussing our work on hardware-oblivious database engines, which are specifically designed to reduce the development overhead when implementing relational operators for heterogeneous hardware [HSP+13]. Generally speaking, there are two significant sources of development overhead when adding support for a new hardware architecture: Code portability, and performance portability. Code portability overhead refers to the effort required to make the engine run on the new architecture. For example, extending a database engine to support GPUs would at the very least require us to set up the GPGPU development environment, map out and implement GPU-accelerated data processing algorithms, provide the database engine with the capability to schedule said algorithms, and develop infrastructure components to manage data transfers, result transfers, and device caching [HLY<sup>+</sup>09, HSP<sup>+</sup>13, BHS<sup>+</sup>14b]. In a hardware-oblivious database engine, we approach code portability from a different angle: Instead of writing hand-written code for each targeted device, engineers provide a single abstract implementation that does not contain any device-specific code and is implemented against a common execution substrate. At runtime, these abstract algorithms are then translated by vendor-provided drivers to run on the actual hardware. In our work, we use OpenCL as this common execution substrate, and we will discuss in the next section why we think that this is a reasonable choice. Performance portability overhead is related to achieving peak performance and fully exploiting the given hardware resources. Multiple authors have repeatedly demonstrated that it is a necessity to fine-tune the implementation of data processing algorithms to the specific characteristics of a device to achieve optimal performance [RVDDB10, BBHS14, RHVM15, PMZM16]. In a hardware-oblivious database engine, we achieve portable performance by relying on a learning hardware-conscious runtime that iteratively refines the hardware-oblivious operator code individually for each device, based on the knowledge gained from runtime performance feedback. Figure 3.1 illustrates these basic concepts to visualize the core components of a hardware-oblivious database engine.

**Figure 3.1:** The fundamental idea behind a hardware-oblivious database engine is to move all hardware-specific code out of the core engine. Instead of having to develop and fine-tune device-specific operators (left), our goal is to rely on a hardware-conscious runtime to generate and iteratively refine device-specific operator code at runtime, based on a common execution substrate like OpenCL that is supported across multiple vendors (right). Figure adapted from [HSP+13].

Now, this overview is obviously just meant to provide a high-level idea of how we could design a hardware-oblivious database engine. In reality, things are never as clear-cut, and there will always be cases where device-specific fixes and optimizations have to be part of the core engine. Still, the general idea of relying on hardware abstraction and high-level programming patterns to improve developer efficiency is sound and has been successfully demonstrated by several authors before [Koc14]. Legobase is probably the most prominent project that follows a similar strategy: Klonatos et al. demonstrated that generating engine code at runtime from abstract operators written in a high-level language allowed them to achieve performance that was similar to hand-tuned engines, while only requiring a fraction of the development overhead [KKRC14]. Many other projects employ similar strategies to improve developer efficiency. Tupleware relies on code generation to efficiently process distributed, UDF-heavy data analytics tasks written in a high-level language [CGD<sup>+</sup>15]. Emma exploits algebraic comprehensions to simplify the development of distributed algorithms over collections [AKK<sup>+</sup>15]. OmniDB, which also aims at reducing the development overhead for data processing on heterogeneous hardware, follows a conceptually similar design approach to hardware-oblivious databases by moving common functionality into an abstract query processing kernel against which developers then have to implement device-specific adapters [ZHHL13]. Voodoo provides an abstract execution algebra for query processing tasks to hide details of the underlying hardware from the developers [PMZM16]. Finally, the programming language research community has repeatedly demonstrated how so-called *iterative* compilers can employ self-tuning mechanisms to learn device-specific compilation heuristics and adapt to the underlying hardware, allowing them to compile highlevel languages down to device-specific code that is close to hand-optimized performance [TCC+09, FKM+11, GGXS+12, PARKA13].

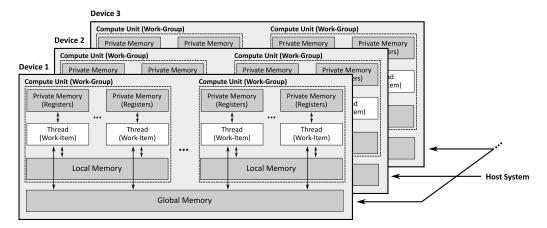

Figure 3.2: An overview of the OpenCL system model.

## 3.2 Background: OpenCL & The Kernel Programming Model

According to the official specification, OpenCL — which was initially developed by Apple and later donated to the non-profit industry consortium Khronos Group —, is an "open royalty-free standard for general purpose parallel programming across CPUs, GPUs and other processors, giving software developers portable and efficient access to the power of these heterogeneous processing platforms" [The15a]. This focus on heterogeneous hardware, as well as its extensive support across various platforms and vendors, distinguishes OpenCL from similar frameworks like Nvidia's CUDA, AMD's Mantle or Microsoft's DirectCompute. It is also what makes OpenCL a highly interesting candidate for the common execution substrate of a hardware-oblivious database engine.

OpenCL was designed from the ground up to allow writing programs that are portable between different computer architectures, covering multiple devices from various vendors. As illustrated in Figure 3.2, OpenCL utilizes a generic system model, expressing computers as a collection of one or more *compute devices*, which are attached to a central host system<sup>1</sup> that controls them. Compute devices themselves consist of one or more compute units — think cores that can each run multiple hardware threads — and come with some on-device *qlobal memory* that is shared among the compute units. Furthermore, devices are assumed to only be capable of operating on data that is stored in their global memory. Accordingly, devices have to rely on explicit data transfers, or memory mapping to access data from other devices or the host. However, this limitation can be relaxed in cases where the global memory of a device is physically identical with the memory of either a different device (like for multi-GPU graphics cards, or integrated GPUs) or the host (like when using the primary CPU as a compute device). Finally, each compute unit itself can contain a small amount of fast, on-chip local memory that is only accessible by the threads running on this unit, and that can be used as an explicit cache or a scratchpad.

Since OpenCL is designed around a strict distinction between the host and the compute devices, programs written against it have to be split into two components:

<sup>&</sup>lt;sup>1</sup>Note that a CPU can act as both the host and as a compute device.

Listing 3.1: Computing a vector sum in OpenCL.

```

__kernel void vector_add(

___global const float* a,

__global const float* b,

__global float* c) {

unsigned int gi = get_global_id(0);

c[gi] = a[gi] + b[gi];

}

```

The host code coordinates the devices, schedules data transfers, and manages computations. For this, the OpenCL standard defines an extensive host API, comprising well over 100 different methods [The 15a]. The second part, which encodes the actual computation, are the so-called kernels, small routines written in a C-derived programming language that express computations from the point-of-view of a single thread. A good way to conceptualize this kernel programming model is to think of kernels as the body of a loop over the input data, while the host code corresponds to the loop header and the code setting up the required variables. Listing 3.1 provides a simple example to illustrate this model, showing a kernel that implements vector addition  $\vec{c} = \vec{a} + \vec{b}$ . Each invocation of the kernel function vec\_add computes a single element of the result vector, with the framework using the return value of the call to get\_global\_id() in line 5 to indicate which element a particular invocation should produce. The OpenCL runtime automatically splits the computational domain into multiple work items to compute the overall result, scheduling a kernel invocation for each item in a data-parallel, lock-free fashion. The total number of work-items is also called the *qlobal size* of the computation. The items themselves are partitioned into equally-sized work-groups, whose size is also called the local size of the computation. The items within a work-group can be synchronized via barriers and memory fences, and share access to the compute unit's local memory. Each work item is uniquely identified by a *qlobal id*, which identifies its global position within the computational domain, as well as a local id, which identifies its local position within the work-group. Note that, since OpenCL allows kernels to be scheduled in domains of up to three dimensions, the global and local ids are actually three-dimensional vectors. However, in the context of this thesis, we will (almost) exclusively work with one-dimensional kernels.

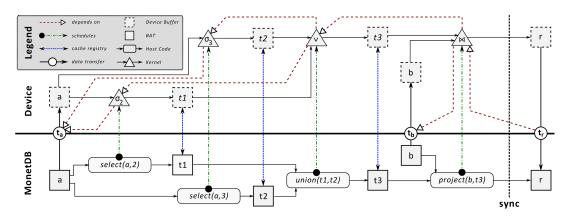

OpenCL provides the so-called event mechanism to enable synchronization between individual operations. Each operation is associated with a unique event marker, representing the operation's current execution status. These markers can be used to profile and query the status of all operations. Furthermore, they allow developers to provide the OpenCL runtime with information about dependency relationships by providing a wait list of events that have to finish before the newly scheduled operation is allowed to start. This enables programmers to schedule highly complex networks of data transfers and computations without having to manage the synchronization between them explicitly. Furthermore, since the OpenCL standard explicitly allows device vendors to exploit this dependency information, it allows the runtime to optimize execution, for instance by reordering non-dependent operations to improve device utilization or caching behavior.

This abstract kernel programming model enables device vendors to map OpenCL programs to a wide variety of hardware architectures. For instance, on a single-

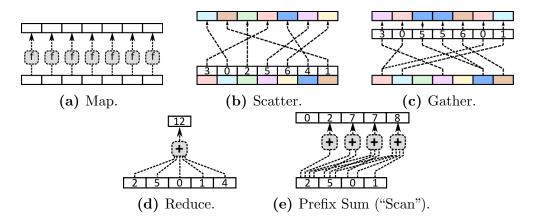

Figure 3.3: Five basic data-parallel programming primitives.

core CPU, work-items can be processed sequentially within a compiler-generated loop, potentially using auto-vectorization to merge neighboring items and to exploit SIMD functionality. On a multi-core CPU, each core can be mapped to an OpenCL compute unit, with the local memory being mapped to the core's L2 memory (if supported). On a GPU, work-groups can be mapped to multi-processors, which each can run a few hundred invocations in parallel and have access to a small amount of fast on-chip memory. Interestingly, OpenCL can also be used to control more exotic hardware such as mobile processors [LNS09, CW11, WXYC13], massively-parallel vector processors [LKS+10, BF10] like the Cell processor or Intel's Xeon Phi [Rei12], or runtime-configurable circuits like FPGAs [SE11, CAD+12, BRS13, WHZ15, WCP+16]. Finally, there are also frameworks that allow OpenCL programs to run in distributed environments, by modeling each server as a distinct compute device [AONM11, KSL+12, DGAJ13].

Let us now demonstrate the flexibility of the kernel programming model by discussing how to implement a basic relational operator. To simplify this process, we will first introduce a set of commonly used data-parallel programming primitives as building blocks that can be efficiently expressed within the model's confines [SHZO07, HGLS07]. By combining these primitives, we can then construct efficient OpenCL representations of most relational operators [HYF<sup>+</sup>08].

Map is the most basic primitive in the kernel programming model. Given an input array I and a function f, it applies the function to each input value independently, storing the generated result to the same position in an output array. This process is illustrated in Figure 3.3a. Assuming that the input and output types are built-in data types, implementing a Map is straightforward in OpenCL since it can be directly mapped to a single kernel that evaluates f. Note that in the context of OpenCL, all invocations of the same Map primitive have to produce the same number of output values.

Scatter & Gather allow us to shuffle data between the in- and output arrays. Both primitives expect an input array I filled with values of type  $T_I$ , and an index array Idx containing n integer values. The Scatter primitive, which is illustrated in Figure 3.3b, reads the input value I[i] at position i and writes it to the output array at the position Idx[i] that is indicated by the index array. Note that every index must be unique to avoid threads overwriting the results

Figure 3.4: Implementing a filter operation in OpenCL.

of each other. The *Gather* primitive, which is illustrated in Figure 3.3c is just the opposite: It reads the input value I[Idx[i]] from the position indicated by the index array and writes it to the output array at position i.

Reduce<sup>2</sup> aggregates all values from a given input array into a single result using a bisymmetric<sup>3</sup> function like addition, multiplication, minimum or maximum. Figure 3.3d illustrates this for the case of a summation. Efficiently implementing the Reduce primitive within the confines of the kernel programming model is typically done via a parallel binary aggregation tree strategy [H<sup>+</sup>07]. Starting with version 2.0, OpenCL provides a built-in work-group reduce function for summation, minimum & maximum, allowing the hardware vendor to insert a device-optimized version at runtime. For older versions of OpenCL, a manual implementation based on barriers and thread-synchronization mechanisms must be used [H<sup>+</sup>07].

Prefix Sum ("Scan") can be seen as a generalized version of the Reduce primitive. Given a (bisymmetric) function g, this primitive transforms an input array I with n values into an output array O, such that  $\forall i \in [1, n] : O_i = g(I_{:i})$ , where  $I_{:i}$  denotes the set of the first i input values. In other words: The output array at position i contains the result of aggregating the first i input values. Figure 3.3d illustrates this for the case of a summation. The  $Prefix\ Sum$  is typically implemented based on a two-pass sweep through a parallel binary aggregation tree over the input array [BRE82, HKL+08]. However, recently, there has also been work on designing single-pass parallel algorithms to improve the operation's IO-behavior [MG16]. Similar to reduce, OpenCL offers a built-in work-group function for the Prefix Sum primitive starting with version 2.0.

Now that we have something to build upon let us discuss how to implement a simple parallel relational operator in the kernel programming model. In particular, let

<sup>&</sup>lt;sup>2</sup>Not to be confused with the *Reduce* operator from MapReduce [DG08]

<sup>&</sup>lt;sup>3</sup>Meaning the function is both associative and commutative.

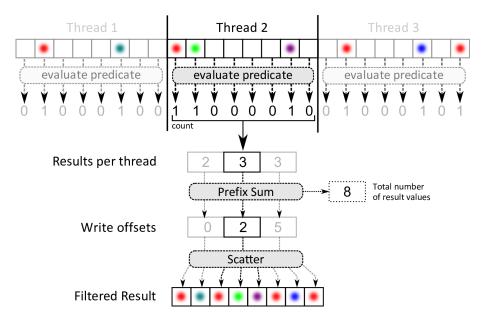

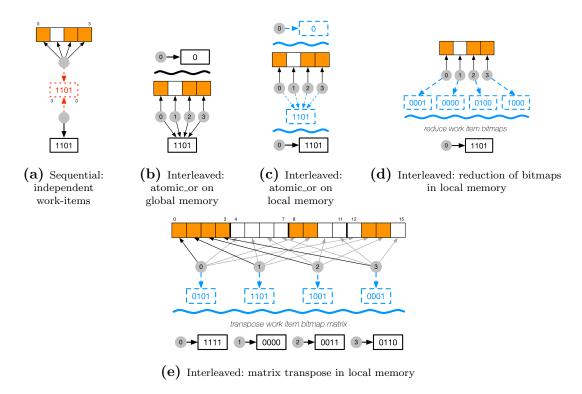

us implement the *Filter* operation, which takes an input column and a predicate, and produces an output column containing only those values that qualify the given predicate. The first step of implementing this is to have each thread evaluate the predicate on its share of input values, which is a straightforward Map primitive. However, things get a little bit more complicated when we want to store back the filtered result: Since the filter removes non-qualifying values from the input, the position where a particular qualifying input value appears in the result depends on how many non-qualifying values came before it. In other words: Since the number of produced values per thread is not known when starting the operation, we generally cannot precompute unique write offsets into the contiguous result array. The straightforward option to solve this problem is to use a single atomic offset counter that gets incremented to produce unique write offsets whenever a thread is writing a result. However, this will cause severe contention when the total number of results is big, given that each produced value requires concurrent access to the atomic result counter, which leads to serialization by the hardware. We can achieve a lock-free solution that avoids this problem by relying on a combination of the Map, Prefix Sum, and Scatter primitives. This strategy, which is illustrated in Figure 3.4, involves three passes: First, each thread counts its number of produced values, writing this number into a temporary buffer. In the second pass, the Prefix Sum primitive is used on the result counts to compute unique write offsets into the result buffer for each thread. These offsets are then used in the final pass of the computation as index values for the Scatter primitive to write the filtered values into the correct positions of the result buffer [WDCY12]. The research literature on GPU-accelerated database operators contains similar strategies to provide efficient OpenCL implementations for virtually all relational operators. This includes sorting [GGKM06, SA08, SHG09a, MG11], hashing [ASA+09, GLHL11, AVS+11, KBGB15], joins [HYF+08, KLMV12, HLH13], group-by & aggregations [Hor05, HFL<sup>+</sup>08, KML15] and string operations [CRRS10, DN13, SR16. This wide variety of supported operators demonstrates the applicability of OpenCL as a target platform for relational query processing.

In summary, OpenCL offers a highly flexible, yet expressive programming standard that enjoys broad support from the hardware industry, with virtually all major vendors providing compatible drivers. This enables programs written against OpenCL to run unchanged on a wide variety of different hardware configurations, making it — and derived frameworks like SyCL [The15b], VexCL [DARG13, Dem14], and Boost.Compute [Lut15] — one of the most promising current platforms for programming heterogeneous hardware. Furthermore, it has repeatedly been demonstrated that OpenCL can indeed act as an efficient and powerful execution target platform for relational databases, in particular when focusing on heterogeneous hardware [HSP+13, ZHHL13, PMZM16, KHL17].

## 3.3 Ocelot — A Hardware-Oblivious Database Engine

In [HSP<sup>+</sup>13], we introduced *Ocelot* as a proof of concept to demonstrate the general feasibility of a hardware-oblivious database engine design. In particular, we wanted to show that implementing our engine against a common execution substrate like OpenCL allowed us to overcome the architectural aspects of the development bottleneck of heterogeneous hardware and achieve code portability across different architectures. Ocelot is integrated into the in-memory column store MonetDB [BKM08] and uses OpenCL as its common execution substrate against which it provides a basic set of hardware-oblivious operators. The name Ocelot was chosen because it reminds of OpenCL, and because Ocelots — a type of wild cat from Southern America — are fast animals, reaching stunning speeds exceeding 60 kph<sup>4</sup>. Ocelot is open-source, and the complete source code can be downloaded from bitbucket.org/msaecker/monetdb-opencl.

**Figure 3.5:** The majestic Ocelot staring mysteriously into the distance. Picture "Nice profile of Nelson" by "Tambako The Jaguar" is licensed under CC ND 2.0.

### 3.3.1 System Overview

Since Ocelot was primarily meant as a demonstrator to showcase a hardware-oblivious database design, we limited our development efforts to the subset of operators that was necessary to allow a reasonable evaluation based on the TPC-H benchmark [Tra14]. Furthermore, to quickly arrive at a working prototype, we decided to design Ocelot as a drop-in replacement of an existing database engine. The choice for using Mon-etDB as our host system was made for two primary reasons: First, MonetDB is an in-memory column store, which is a vital prerequisite to achieve performance improvements obtained from modern hardware in general, and from graphics cards in particular [GAHF05, Bre14]. Second, MonetDB's source code is publicly available

<sup>&</sup>lt;sup>4</sup>http://a-z-animals.com/animals/ocelot

Figure 3.6: The architecture of Ocelot. Figure taken from [HSP<sup>+</sup>13].

under an open-source license, which made it easy for us to make the required modifications and also enabled us to publish our system under the same open-source license. Building Ocelot on top of MonetDB allowed us to reuse several major components, including the data layout, storage management, debugging facilities, and plan scheduler. It also allowed us to recycle MonetDB's query plans, which greatly simplified development, testing, and benchmarking. Furthermore, it allows both systems to complement each other, with Ocelot being able to fall back to MonetDB for operators that it does not support, and with MonetDB gaining support for hardware-accelerated operations from Ocelot.

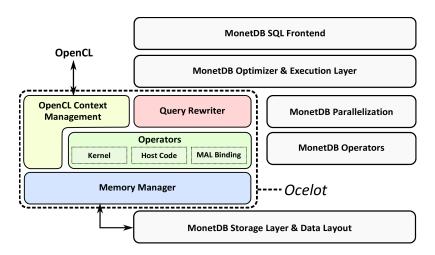

Figure 3.6 shows a high-level overview of Ocelot's architecture, highlighting its four major components: The *Operators* are the central part and the workhorse of Ocelot, each one implementing a hardware-oblivious drop-in replacement of a particular MonetDB database operator against OpenCL. The *Memory Manager* is used to abstract away details of the memory architectures from the operators by transparently handling device memory management and required data transfer operations. The *Query Rewriter* adjusts MonetDB's query plans by replacing operator calls by the corresponding ones from Ocelot. Finally, the *OpenCL Context Management* initializes the OpenCL runtime environment, detects all available OpenCL devices, triggers the compilation of kernels for each device, handles the scheduling of operations and data transfers, and provides API calls and internal data structures for each device to the operators. With the overview out of the way, let us now discuss the individual components in greater depth.

### 3.3.2 Hardware-Oblivious Operators

Ocelot's operators are advertised to MonetDB via a *MonetDB Assembly Language* (MAL) binding, describing the interface and entry function. The entry function contains the host code to schedule all required OpenCL operations for the current operator. This includes checking input parameters, setting up the required resources on the device via the Memory Manager, initializing the required kernels, and scheduling them for execution via the Context Management. Most operators also contain code to handle errors, ensuring that all held resources are released upon encountering an unrecoverable error. The actual computations are implemented as standard OpenCL

kernels, which are compiled in bulk by the Context Management for all detected devices when Ocelot is initialized. Naturally, neither the operator host code nor the kernels contain any device-specific code. Instead, the operators rely on the abstraction mechanisms provided by OpenCL and by Ocelot's common infrastructure to arrive at a fully portable, hardware-oblivious implementation that allows them to run without changes on any available OpenCL device. In fact, setting the device on which a given operator should run on is done by simply passing the id of the intended device as an optional argument to the operator. Setting this argument only changes which OpenCL context is handed to the operator by the Ocelot runtime: From the operator's point of view there is no difference between running on the CPU, on a graphics card, or even on an FPGA. The context transparently handles all device-specific operations like required memory transfers, specific scheduling decisions, or compilation choices. Let us now take a quick look at how we implemented some of these operators. With OpenCL being derived from a GPU-centric programming model, we based most of our implementations on existing work from the area of GPU-accelerated databases [GLW+04, HGLS07, HYF+08, HLY+09, BS10, WDCY12, KLMV12, HLH13].

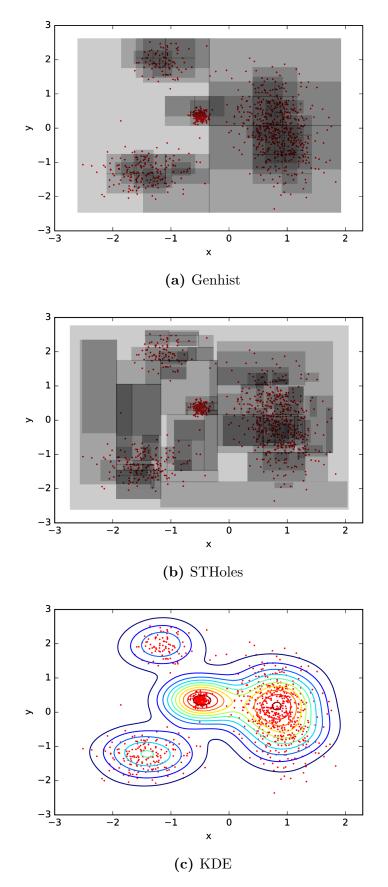

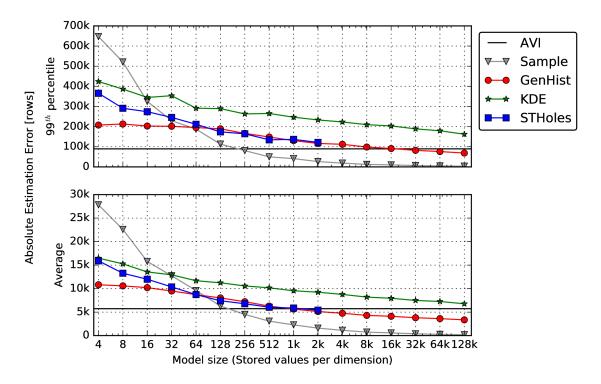

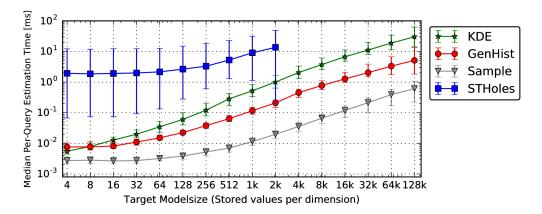

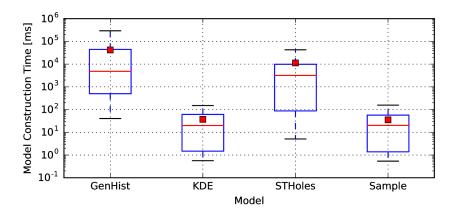

### Filter