# Fully Integrated, Multichannel IC for Brain Machine Interfaces

## DISSERTATION

to obtain the academic degree

## **DOKTOR-INGENIEUR**

(Dr.-Ing.)

at the faculty of Engineering, Computer Science and Psychology of the University of Ulm

by

## Michael Haas

### from Ochsenhausen

(Place of birth)

| Supervisor:      | Prof. DrIng. Maurits Ortmanns |

|------------------|-------------------------------|

| Second Examiner: | Prof. Qiang Li                |

Officiating Dean: Prof. Dr.-Ing. Maurits Ortmanns

Ulm, 20.09.2019

## **Declaration of Authorship**

I, Michael Haas, declare that this thesis titled, 'Fully Integrated, Multichannel IC for Brain Machine Interfaces' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

#### Signed:

#### Date:

| Officiating Dean:  | Prof. DrIng. Maurits Ortmanns |

|--------------------|-------------------------------|

| Committee Members: | Prof. DrIng. Maurits Ortmanns |

|                    | Prof. Qiang Li                |

|                    | Prof. DrIng. Robert Fischer   |

|                    | Prof. DrIng. Christian Damm   |

"One, remember to look up at the stars and not down at your feet. Two, never give up work. Work gives you meaning and purpose and life is empty without it. Three, if you are lucky enough to find love, remember it is there and don't throw it away."

Stephen Hawking (1942-2018)

To my wife Julia

### Abstract

The rapid progress of technology in the semiconductor industry over the last decades allowed the development of a whole new generation of fully integrated neuromodulators. By an increase in the level of integration, new systems on chip (SoCs) that allow the simultaneous recording and stimulation of nervous signals were developed. These chips enable implantable, medical devices, capable of providing so far unreachable spatiotemporal resolution, while eliminating inflammation prone through-skin wires. The ongoing demand for higher spatial resolution, together with the tight power and size requirements imposed by implantation needs, result in growing challenges for the integrated circuit design.

Besides the fundamental requirements for power, area and noise, the unknown, biological system itself imposes the biggest challenge. Since the observable signals and the required stimulation patterns heavily depend on the physiology of each individual, all systems require high flexibility and maximum adaptability to the patient. The presented work deals with that challenge and presents new circuit architectures, that allow the reconfiguration of the recording system as well as the stimulation system to the current neurological state, while being implanted.

In the recording subsystem, a new tuning mechanism for the low noise amplifier is presented. It provides a flexible trade-off between noise performance and amplifier bandwidth, to adapt the recorder to the currently observed, neural signal. Further, electrode impedance estimation was introduced with a new low-gain recording mode. Thereby, the recorder is reused to acquire the impulse response of the electrode, which allows to detect broken wires or electrode degradation due to electrochemical processes.

In order to provide maximum flexibility for the stimulation, a novel, high voltage (HV) stimulator was developed, which is capable of providing current and voltage controlled, arbitrary stimulation waveforms. This was achieved by a new, semi-digital feedback loop, which controls the output current of the current stimulator in order to achieve the desired electrode voltage. Thereby, power efficient class-B operation is achieved, while requiring only little area overhead, as the full HV output stage is reused.

Both subsystems were combined, together with two high resolution analog to digital converters (ADCs), in a 32 channel SoC, which provides significant advantages for future implants by minimizing the required amount of off-chip components. Furthermore, integrated electrode monitoring improves patient safety and the increased flexibility in recording and stimulation improves the freedom in the design of experiments and therapies.

## Acknowledgements

First and foremost, I would like to thank my supervisor Prof. Dr.-Ing Maurits Ortmanns for his consistent guidance, financial support of my research, great discussions, encouragement and invaluable advice. It was a great honor and privilege for me to work with him over the years under his supervision and mentorship.

Additionally, I would like to thank Prof. Qiang Li for being my second examiner. Thank you for giving me valuable feedback and for making the long journey from Chengdu to Ulm.

Furthermore, I want to thank Dr. Joachim Becker for giving me many helpful suggestions and assistance with the digital design and for a perfect digital design flow, making digital synthesis really just the press of a button.

Additionally, I would like to thank all my former colleagues. Jiazuo Chi has been an excellent office mate and friend over almost my entire time at the institute. We had great discussions on IC design and much, much more. I would like to thank my colleagues, co-authors and good friends, Patrick Vogelmann and Prof. Dr.-Ing. Jens Anders for all their help in design, implementation and measurement. Last but not least, I would also like to thank everyone taking part in our early morning coffee round, sharing numerous great on- and off-topic discussions.

Finally, I would like to thank my wife, Julia Haas and my whole family for their support and encouragement during all times of my Ph.D. studies. If it wasn't for them, this work would have not been possible.

# Contents

| Declaration of Authorship |      |

|---------------------------|------|

| Abstract                  | ix   |

| Acknowledgements          | xi   |

| Contents                  | xiii |

| List of Figures           | XV   |

| List of Tables            | xix  |

| Abbreviations             | xxi  |

| 1        | Intr | oducti  | ion                                                            | 1  |

|----------|------|---------|----------------------------------------------------------------|----|

|          | 1.1  | Motiva  | ation                                                          | 3  |

|          | 1.2  | Achiev  | vements and innovations of the research work                   | 6  |

|          | 1.3  | Outlin  | e of the thesis                                                | 7  |

| <b>2</b> | Bac  | kgrou   | nd and State of the Art                                        | 9  |

|          | 2.1  | Centra  | al nervous system                                              | 9  |

|          |      | 2.1.1   | Anatomy and function of the neuron                             | 9  |

|          |      | 2.1.2   | Observable neural signals                                      | 12 |

|          | 2.2  | Interfa | acing of nervous tissue                                        | 14 |

|          |      | 2.2.1   | Electrode-electrolyte interface                                | 14 |

|          |      | 2.2.2   | Implantable electrodes                                         | 15 |

|          | 2.3  | Integr  | ated recorders for implantable Brain Machine Interfaces (BMIs) | 17 |

|          |      | 2.3.1   | Conventional architecture                                      | 18 |

|          |      | 2.3.2   | Chopper stabilized architecture                                | 20 |

|          | 2.4  | Integr  | ated neural stimulators                                        | 22 |

|          |      | 2.4.1   | Constant current stimulators                                   | 24 |

|          | 2.5  | Multi   | channel bidirectional neural front-ends                        | 25 |

|          |      | 2.5.1   | Bidirectional neural front-ends                                | 25 |

|          |      | 2.5.2   | State of the Art                                               | 26 |

|          |      | 2.5.3   | Challenges and requirements                                    |    |

| 3        | Net   | ıral recorder design 33                                                                                                                                          | ;      |

|----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|          | 3.1   | Previous design                                                                                                                                                  | ;      |

|          | 3.2   | Noise improvement                                                                                                                                                | )      |

|          | 3.3   | Tunable neural recorder                                                                                                                                          | )      |

|          | 3.4   | Electrode impedance estimation                                                                                                                                   | ;      |

|          | 3.5   | Area and power breakdown                                                                                                                                         | ,      |

| <b>4</b> | Hig   | h voltage neural stimulator 49                                                                                                                                   | )      |

|          | 4.1   | Constant current stimulator                                                                                                                                      | )      |

|          |       | 4.1.1 Voltage domains                                                                                                                                            | )      |

|          |       | 4.1.2 Digital level shifters                                                                                                                                     | 2      |

|          |       | 4.1.3 Current steering DAC                                                                                                                                       | )      |

|          |       | 4.1.4 HV output stages                                                                                                                                           | ,      |

|          | 4.2   | High voltage recorder interface                                                                                                                                  | -      |

|          | 4.3   | Constant voltage stimulator                                                                                                                                      | ,<br>) |

|          |       | 4.3.1 System architecture                                                                                                                                        | ;      |

|          |       | 4.3.2 Stability analysis                                                                                                                                         | )      |

|          |       | 4.3.3 Measurement results                                                                                                                                        | 2      |

|          | 4.4   | Area and power breakdown                                                                                                                                         | ;      |

| 5        | 32 (  | Channel Bidirectional Neural Interface 79                                                                                                                        | )      |

|          | 5.1   | Neural front-end channels                                                                                                                                        |        |

|          | 5.2   | Digital stimulation control                                                                                                                                      |        |

|          |       | 5.2.1 Global control unit (GCU)                                                                                                                                  |        |

|          |       | 5.2.2 Data Package Types                                                                                                                                         |        |

|          |       | 5.2.3 Waveform synthesis                                                                                                                                         |        |

|          |       | 5.2.4 Global Error Handling                                                                                                                                      |        |

|          |       | 5.2.5 Local Control Unit (LCU)                                                                                                                                   |        |

|          | 5.3   | On-Chip Analog to Digital Converters (ADCs)                                                                                                                      |        |

|          | 5.4   | Supporting analog circuitry                                                                                                                                      |        |

|          |       | $5.4.1$ Linear regulators $\ldots \ldots \ldots$ |        |

|          |       | 5.4.2 Reference circuits                                                                                                                                         |        |

|          | 5.5   | Summary                                                                                                                                                          |        |

| 6        | Con   | clusion and outlook 107                                                                                                                                          | ,      |

|          | 6.1   | Conclusion                                                                                                                                                       |        |

|          | 6.2   | Outlook                                                                                                                                                          |        |

|          | 0.2   | Callon                                                                                                                                                           |        |

| Bi       | blio  | graphy 111                                                                                                                                                       | _      |

|          |       |                                                                                                                                                                  |        |

| ப        | st of | Author Publications 125                                                                                                                                          | )      |

Resume

127

# List of Figures

| 1.1        | Different implementations of Functional Electrical Stimulation (FES) and their key parameters.                                                                  | 3        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2        | Conceptual neural modulator to stimulate and record the neural network of the human brain.                                                                      | 4        |

| 2.1        | Anatomy of a multipolar neuron                                                                                                                                  | 10       |

| 2.2        | Propagation of an Action Potential (AP) along a myelinated axon and<br>the resulting membrane sultage even time, based on [1]                                   | 11       |

| 2.3        | the resulting membrane voltage over time, based on [1]                                                                                                          | 11       |

| 2.0<br>2.4 | Comparison of different recording approaches regarding spatial and tem-                                                                                         | 11       |

|            | poral resolution, derived from [3]                                                                                                                              | 12       |

| 2.5        | Recorded, extracellular potential of a sleeping rat, showing Local Field                                                                                        |          |

|            | Potential (LFP) and AP signal parts; Signals from [4, 5]                                                                                                        | 13       |

| 2.6        | Neural signal filtered with 6th order Butterworth filter; Signal from: [5].                                                                                     | 13       |

| 2.7        | Non-Faradic reactions at the electrode-electrolyte interface, based on [6].                                                                                     | 14       |

| 2.8        | The 10 x 10 Utah electrode array (UEA) [7]. $\dots \dots \dots$ | 15       |

| 2.9        | Commercially available 8x8 ECoG electrode array (CorTEC - AirRay) [8].                                                                                          | 16       |

| 2.10       | System level diagram of a multi channel neural recorder                                                                                                         | 17       |

| 2.11       |                                                                                                                                                                 | 18       |

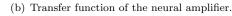

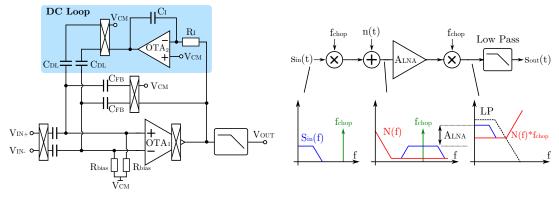

| 2.12       | Chopped neural amplifier                                                                                                                                        | 20       |

| 2.10       | impedance boosting, based on [10]                                                                                                                               | 21       |

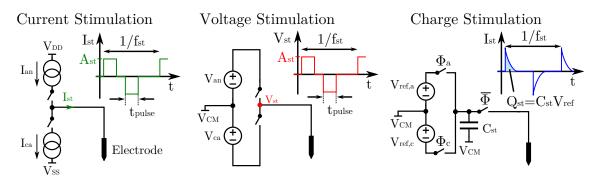

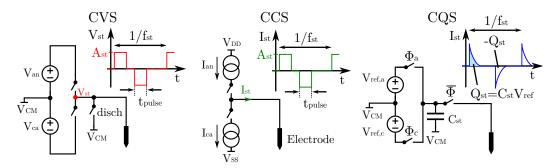

| 2.14       | Block diagram of a constant voltage (CVS), constant current (CCS) and                                                                                           | 21       |

|            | constant charge (CQS) stimulation.                                                                                                                              | 22       |

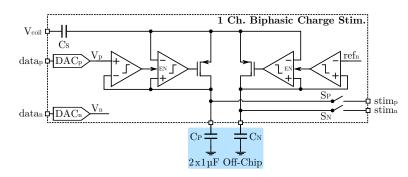

| 2.15       | Single channel of the inductively powered CQS presented in [11]                                                                                                 | 23       |

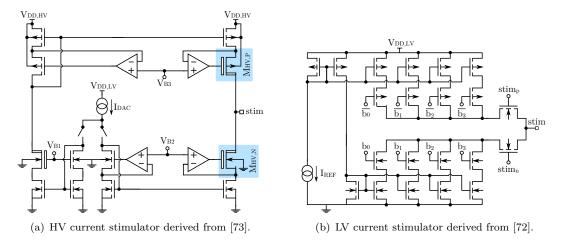

| 2.16       | HV/LV CCS with current steering DACs.                                                                                                                           | 24       |

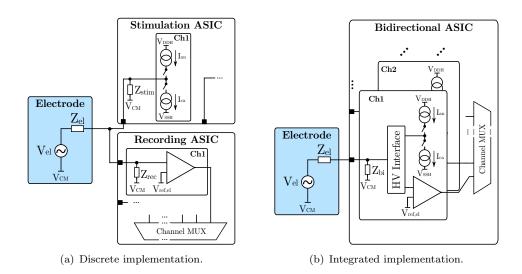

| 2.17       | Bidirectional neural interface architectures.                                                                                                                   | 26       |

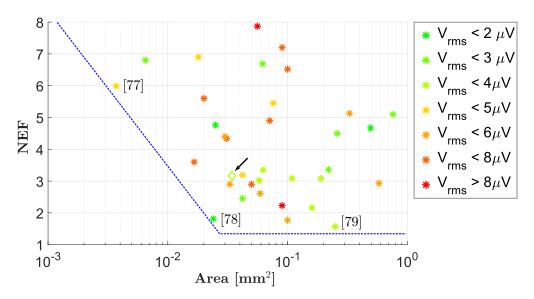

| 2.18       | Illustration of the power-area-noise trade-off of various neural recorders                                                                                      |          |

|            | from JSSC & TBioCAS 2010-2018                                                                                                                                   | 27       |

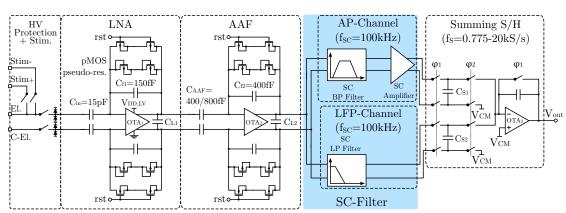

| 3.1        | Neural recorder with spectral separation from [12]                                                                                                              | 33       |

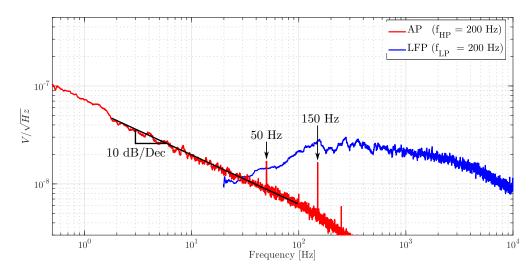

| 3.2        | Measured output referred noise, divided by midband channel gain of the                                                                                          |          |

|            | original recorder for LFP and AP band, with maximum gain settings in                                                                                            |          |

|            | both bands.                                                                                                                                                     | 36       |

| 3.3        | Schematic of the original neural recorder. Highlighted are the main noise                                                                                       | 96       |

| 9 A        | contributers in the LFP band                                                                                                                                    | 36       |

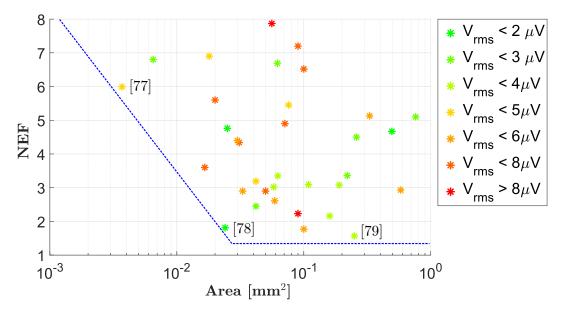

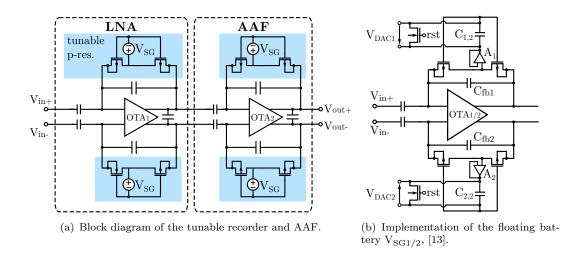

| 3.4<br>2.5 | Comparison of the revised recorders NEF to the SoA                                                                                                              | 38<br>40 |

| 3.5        | methan recorder mont-end with tunable figh-pass frequency                                                                                                       | 40       |

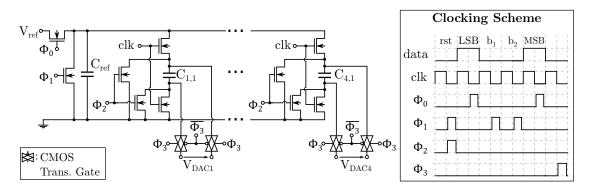

| 3.6  | SC serial DAC used for pseudo resistor tuning, modified from [13], with                     |            |

|------|---------------------------------------------------------------------------------------------|------------|

|      | permission from $\textcircled{C}2016$ IEEE                                                  | 40         |

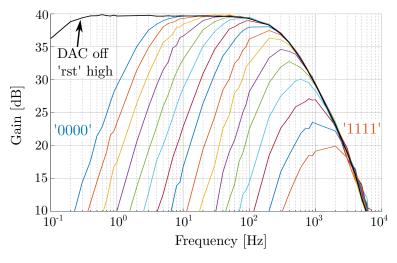

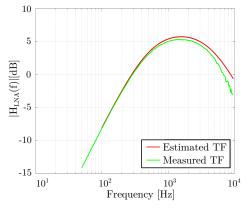

| 3.7  | Measured LFP transfer function of the tuned recorder                                        | 42         |

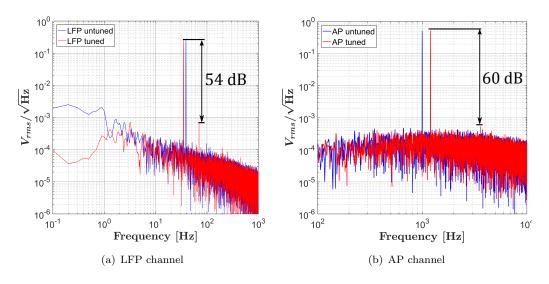

| 3.8  | Measured output spectra of the tuned (red) and untuned (blue) recorder [14].                | 42         |

| 3.9  | LNA with low gain mode and impulse source for bio-impedance estimation                      | 12         |

| 0.5  | modified from $[13]$ , with permission from $\textcircled{C}$ 2016 IEEE                     | 43         |

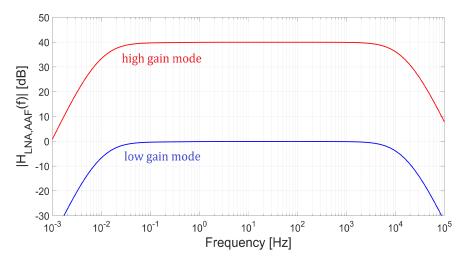

| 3 10 | TF of the LNA and AAF in low gain and high gain mode                                        | 44         |

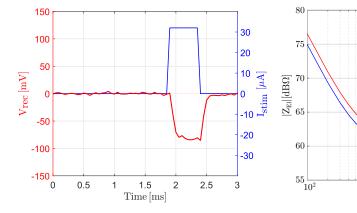

|      | Measured electrode impedance estimation for a lumped elements electrode                     | 11         |

| 0.11 | model ( $R_S = 1 k\Omega$ , $C_{DL} = 290 nF$ )                                             | 46         |

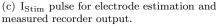

| 3.12 | Electrode impedance estimation of planar Pt electrodes                                      | 46         |

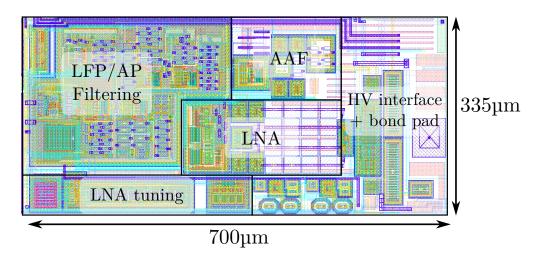

| 3.13 | Layout of the neural recorder                                                               | 47         |

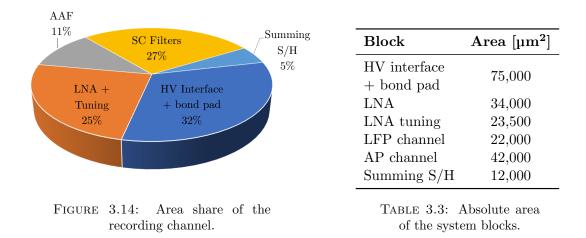

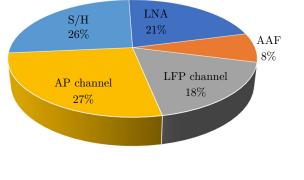

|      | Area share of the recording channel                                                         | 47         |

| 3.15 | Power share of the recording channel (Tuning: ON)                                           | 48         |

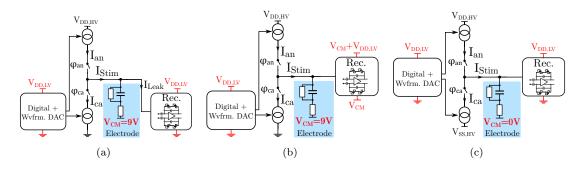

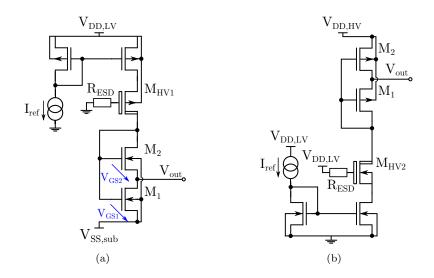

| 4.1  | Evaluated approaches for the LV supply domains                                              | 50         |

| 4.2  | Block diagram of the bidirectional neural front-end using floating voltage                  |            |

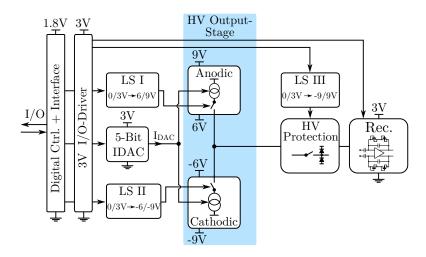

|      | domains                                                                                     | 51         |

| 4.3  | Evaluated approaches for the LV supply domains                                              | 52         |

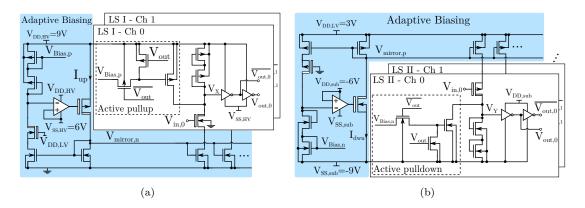

| 4.4  | Static Level Shifter (LS) with adaptive bias generation, derived from [15].                 | 53         |

| 4.5  | Monte Carlo simulation with 200 runs of the LS to evaluate device mismatch.                 | 54         |

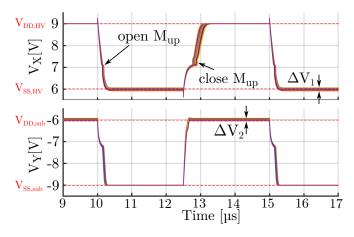

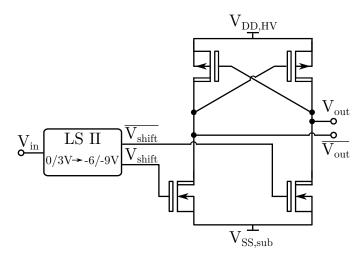

| 4.6  | Digital LS from $0/3$ V to $-9/+9$ V (LS III)                                               | 55         |

| 4.7  | N bit current steering DAC with binary weighted current sources                             | 55         |

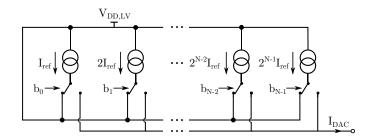

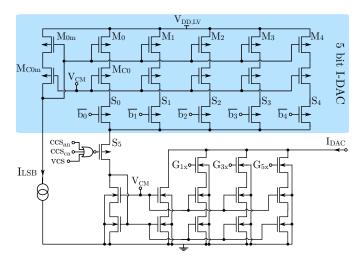

| 4.8  | 5 bit current steering DAC with variable gain current mirror                                | 56         |

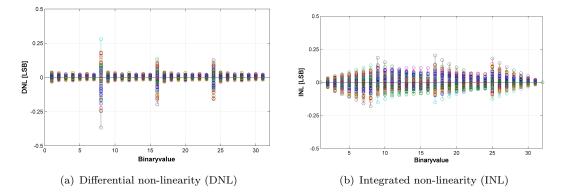

| 4.9  | Simulated DNL and INL of the 5 bit I-DAC (200 Monte Carlo runs)                             | 56         |

| 4.10 | Biphasic, HV output stage of the current stimulator, derived from [16]                      | 57         |

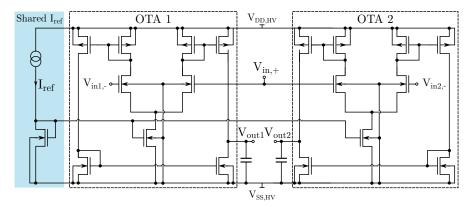

|      | Dual differential amplifier of the anodic output stage                                      | 58         |

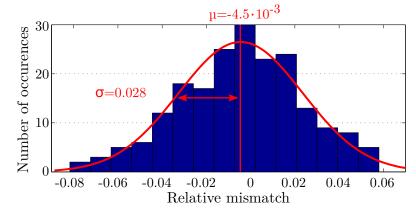

|      | Relative mismatch of anodic/cathodic stimulation current for $I_{\rm Stim}=\pm10.2{\rm m}$  |            |

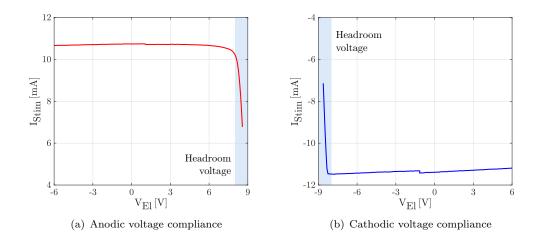

|      | Measured anodic/cathodic voltage compliance.                                                | 60         |

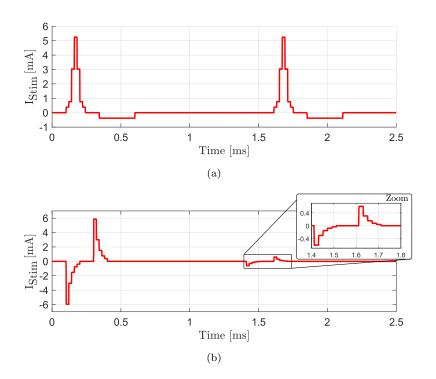

|      | Measured stimulation waveforms using a $100 \Omega$ dummy load                              | 60         |

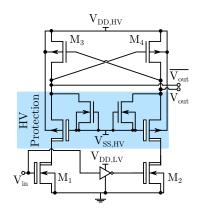

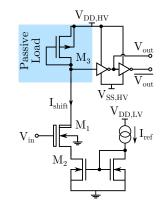

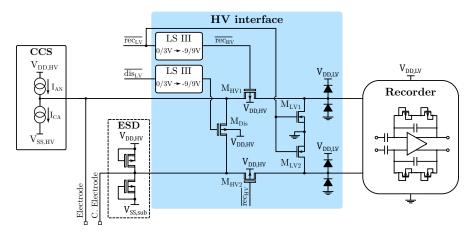

|      | HV compliant recorder interface                                                             |            |

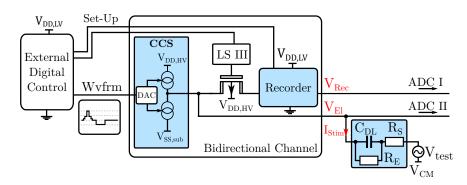

|      | Measurement set-up to evaluate combined recording/stimulation                               | 63         |

| 4.17 | Measured stimulation with intentional charge mismatch, passive charge                       |            |

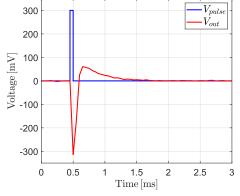

|      | balancing and subsequent recording.                                                         | 64         |

| 4.18 | Neuromodulator with semi-digital feedback to realize CVS, derived from                      | 0 <b>F</b> |

| 4.10 | [14].                                                                                       | 65         |

|      | Block diagram of the voltage/current mode stimulator, derived from [17].                    | 66         |

|      | Linearized model of the CVS control loop, derived from [17].                                | 67         |

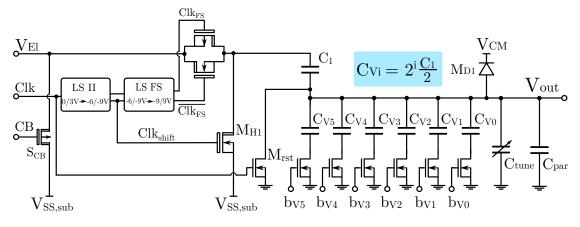

|      | Variable gain LS with binary scaled C-array, derived from [17].                             | 68         |

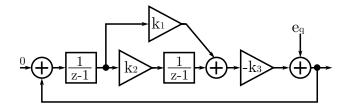

|      | DT model of the CVS control loop                                                            | 69         |

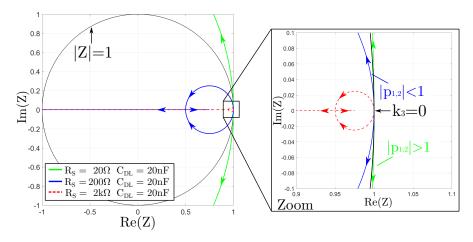

| 4.23 | Root Locus Plot (RLP) over $k_3 = A_Q \cdot A_{LS}$ and parametrized electrode values [17]. | 70         |

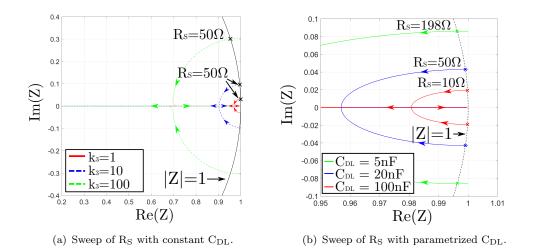

| 4.24 | RLP for varying electrode parameters.                                                       | 71         |

|      | Simulated CVS waveforms on two different electrode models.                                  | 72         |

|      | Measured CVS waveforms on two different, lumped elements electrode                          |            |

|      | models.                                                                                     | 73         |

| 4.27 | Measured CVS waveforms with varying full scale current $I_{\rm FS}.$                        | 74         |

| 4.28 | Measured electrode potentials for CVS/CCS on Pt electrodes in Phosphate<br>Buffered Saline (PBS)                     |

|------|----------------------------------------------------------------------------------------------------------------------|

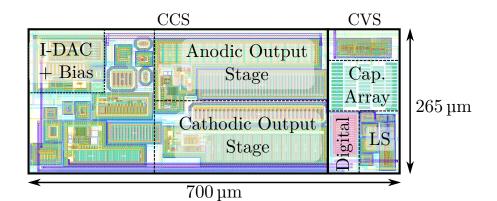

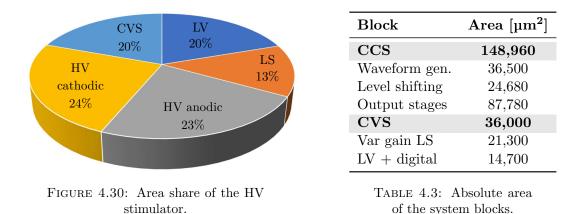

| 4.29 | Layout of the HV current/voltage stimulator                                                                          |

|      | Area share of the HV stimulator                                                                                      |

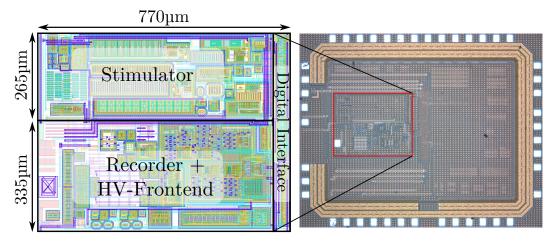

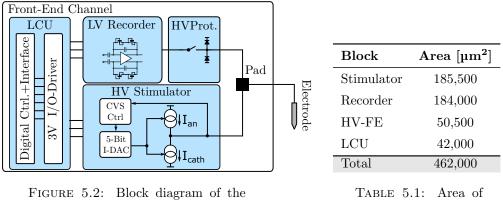

| 5.1  | Layout and prototype of a single front-end channel                                                                   |

| 5.2  | Block diagram of the neural front-end channel                                                                        |

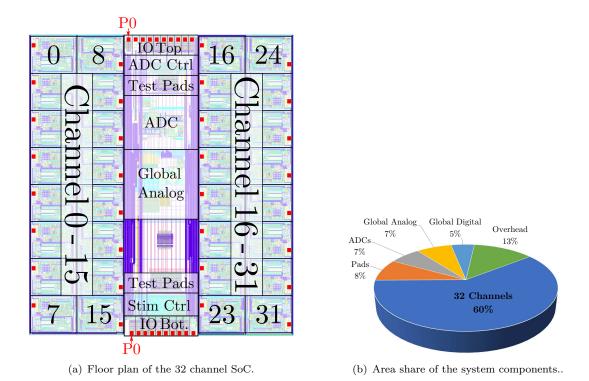

| 5.3  | Multichannel, bidirectional neural interface                                                                         |

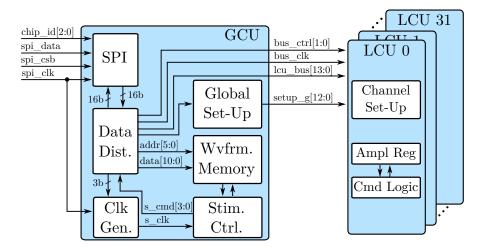

| 5.4  | Block diagram of the digital stimulation control                                                                     |

| 5.5  | Stimulation process with global timing and local amplitude control 84                                                |

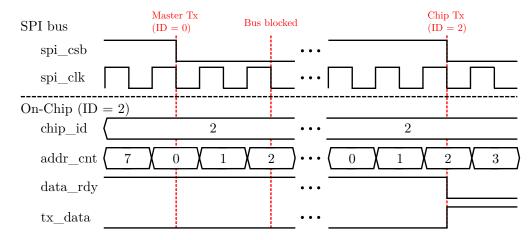

| 5.6  | Exemplary SPI bus management based on chip id                                                                        |

| 5.7  | Timing of the SPI data transmission                                                                                  |

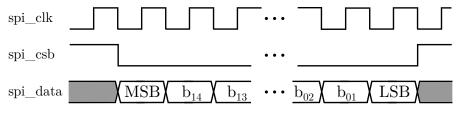

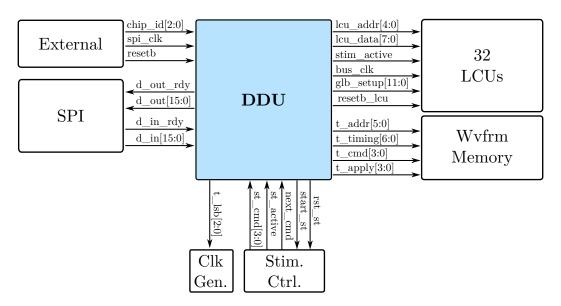

| 5.8  | Data IOs of the Data Distribution Unit (DDU)                                                                         |

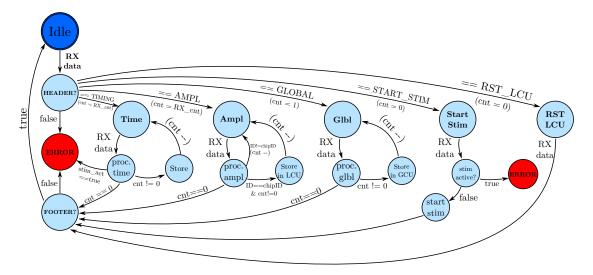

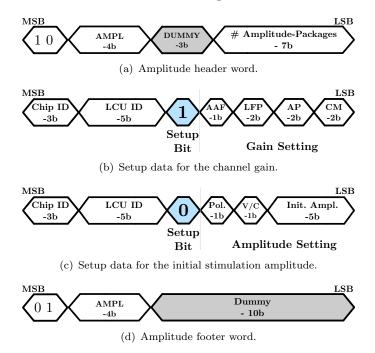

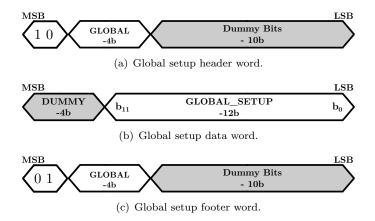

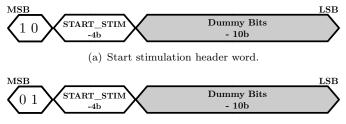

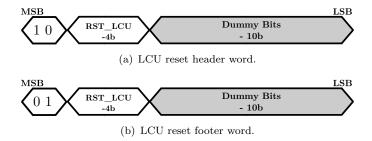

| 5.9  | Structure of the 16 bit SPI control words                                                                            |

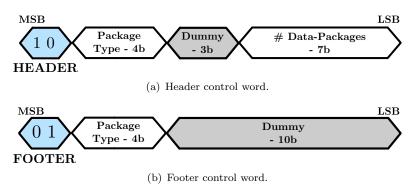

| 5.10 | Finite State Machine (FSM) of the DDU                                                                                |

| 5.11 | Bit level structure of a global timing transmission                                                                  |

| 5.12 | Bit level structure of LCU setup data transmission                                                                   |

| 5.13 | Bit level structure of a global setup transmission                                                                   |

| 5.14 | Bit level structure of the stimulation start command                                                                 |

| 5.15 | Bit level structure of the LCU reset command                                                                         |

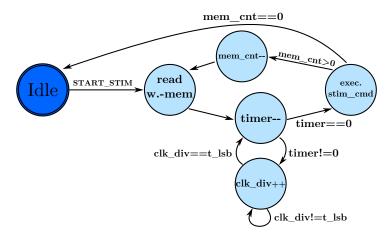

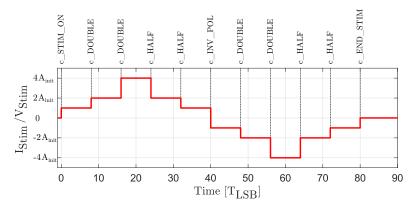

| 5.16 | FSM of the stimulation waveform synthesis                                                                            |

| 5.17 | Default stimulation waveform                                                                                         |

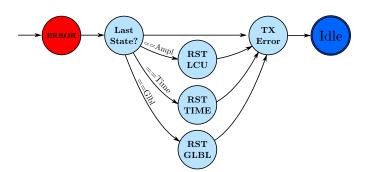

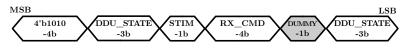

| 5.18 | Global error handling in the DDU                                                                                     |

| 5.19 | Generated error message                                                                                              |

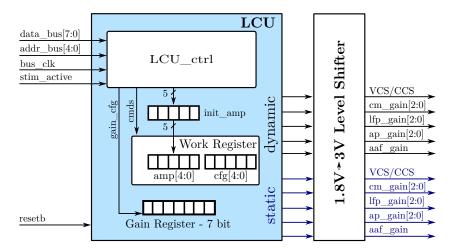

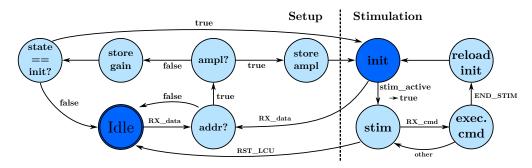

|      | Block diagram of the Local Control Unit (LCU)                                                                        |

| 5.21 | FSM of the Local Control Unit (LCU)                                                                                  |

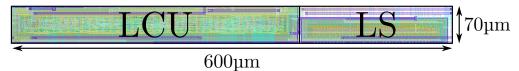

| 5.22 | Layout of the Local Control Unit (LCU)                                                                               |

| 5.23 | Multiplexed, 16 channel sample-and-hold for the on-chip ADC 98                                                       |

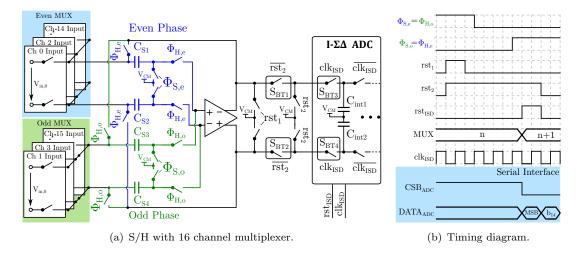

| 5.24 | Simulated performance of the Analog-to-Digital Converter (ADC), in-<br>cluding the multiplexed Sample-and-Hold (S/H) |

| 5.25 | ADC and S/H power share                                                                                              |

| 5.26 | Low Dropout Regulators (LDOs) for the $\pm 6$ V supply levels                                                        |

|      | Layout of the two LDOs                                                                                               |

| 5.28 | Reference voltage generation for the regulated, triode current mirror 103                                            |

| 5.29 | Beta multiplier for reference current generation                                                                     |

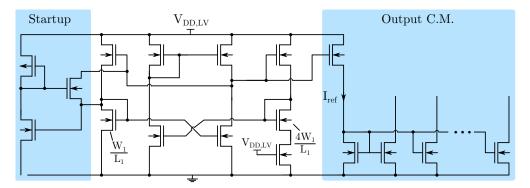

| 6.1  | Miniaturized IR-UWB transmitter [18]                                                                                 |

# List of Tables

| 2.1 | Performance compared to the state of the art               | 29  |

|-----|------------------------------------------------------------|-----|

| 3.1 | Performance of the original recorder design.               | 35  |

| 3.2 | Performance of original and revised recorder design.       | 38  |

| 3.3 | Absolute area of the system blocks                         | 47  |

| 3.4 | Power consumption of the system blocks.                    | 48  |

| 4.1 | Design parameters of the dual differential amplifiers      | 59  |

| 4.2 | Parameters of the presented CCS                            | 61  |

| 4.3 | Absolute area of the system blocks                         | 76  |

| 4.4 | Quiescent current $I_0$ of the different stimulator blocks | 77  |

| 5.1 | Area of the channel blocks.                                | 80  |

| 5.2 | IO pin description of the 32 channel SoC                   | 82  |

| 5.3 | Global channel setup configuration                         | 91  |

| 5.4 | Stimulation commands for waveform synthesis                | 94  |

| 5.5 | ADC and S/H power consumption                              | 100 |

| 5.6 | Performance compared to the state of the art               | 105 |

|     |                                                            |     |

# Abbreviations

| AAF            | Anti-Aliasing Filter                    |

|----------------|-----------------------------------------|

| ADC            | Analog-to-Digital Converter             |

| AP             | Action Potential                        |

| ASIC           | Application Specific Integrated Circuit |

| BMI            | Brain Machine Interface                 |

| CB             | Charge Balancing                        |

| CCS            | Constant Current Stimulaton             |

| CMFB           | Common Mode Feedback                    |

| CMOS           | Complementary Metal-Oxide-Semiconductor |

| CNS            | Central Nervous System                  |

| $\mathbf{CQS}$ | Constant Charge Stimulation             |

| CSB            | Chip Select Bit                         |

| $\mathbf{CT}$  | Continuous Time                         |

| CVS            | Constant Voltage Stimulation            |

| DAC            | Digital-to-Analog Converter             |

| DDU            | Data Distribution Unit                  |

| DR             | Dynamic Range                           |

| DT             | Discrete Time                           |

| ECoG                 | Electrocorticography                  |

|----------------------|---------------------------------------|

| EEG                  | Electroencephalography                |

| ENoB                 | Effective Number of Bits              |

| ESD                  | Electrostatic Discharge               |

| FES                  | Functional Electrical Stimulation     |

| fMRI                 | Functional Magnetic Resonance Imaging |

| fNIRS                | Functional Near-Infrared Spectroscopy |

| FSM                  | Finite State Machine                  |

| GCU                  | Global Control Unit                   |

| HV                   | High Voltage                          |

| HV CMOS              | High Voltage CMOS                     |

| IC                   | Integrated Circuit                    |

| $I\Delta\Sigma$ -ADC | incrementel $\Delta\Sigma$ ADC        |

| IR-UWB               | Impulse Radio Ultra Wide Band         |

| I-SD                 | Incremental $\Sigma\Delta$            |

| LCU                  | Local Control Unit                    |

| LDO                  | Low Dropout Regulator                 |

| LFP                  | Local Field Potential                 |

| LNA                  | Low Noise Amplifier                   |

| $\mathbf{LS}$        | Level Shifter                         |

| LSB                  | Least Significant Bit                 |

| LV                   | Low Voltage                           |

| MEA                  | Micro Electrode Array                 |

| NEF                  | Noise Efficiency Factor               |

| OSR            | Oversampling Ratio                     |

|----------------|----------------------------------------|

| ΟΤΑ            | Operational Transconductance Amplifier |

| PBS            | Phosphate Buffered Saline              |

| RLP            | Root Locus Plot                        |

| $\mathbf{SC}$  | Switched Capacitor                     |

| $\mathbf{SDM}$ | $\Sigma\Delta$ Modulator               |

| SEM            | Scanning Electron Microscope           |

| S/H            | Sample-and-Hold                        |

| SNDR           | Signal-to-Noise-and-Distortion-Ratio   |

| SNR            | Signal to Noise Ratio                  |

| SoA            | State-of-the-Art                       |

| SoC            | System on Chip                         |

| SPI            | Serial Peripheral Interface            |

| TF             | Transfer Function                      |

| THD            | Total Harmonic Distortion              |

| TIA            | Transimpedance Amplifier               |

| UEA            | Utah Electrode Array                   |

| UWB            | Ultra Wide Band                        |

### Chapter 1

## Introduction

Biomedical brain implants are of major interest within the research and therapy of neurological disorders, as implantable electrodes, that interface the brain below the dura, can provide much higher signal levels and spatial resolution compared to non-invasive Electroencephalography (EEG) techniques [19, 20]. Additionally, placing the electrodes closer to the interacting neurons does not only yield improved signal quality, but also allows to stimulate a reaction of the surrounding tissue with high spatial resolution, via Functional Electrical Stimulation (FES). This reaction is triggered by injecting charge into the nervous tissue, in order to depolarize a neuron and trigger an action potential. The ongoing trend in brain implants is towards systems that provide a fast growing number of independent, parallel recording and stimulation sites, together with wireless power and data transmission [21–24].

In research, the increasing number of channels allows a higher spatiotemporal resolution of the communication paths within the central nervous system. The combined stimulation/recording capabilities can provide a detailed image of the nervous reaction, which can be used to derive a mapping of the functional brain units [25] and lead to a deeper understanding of the working mechanisms. Even high resolution recording alone can be used to exactly locate the propagation of stimuli through the brain and track the complete path from the processing of a visual stimulation all the way to a reaction in the motor cortex [26]. Furthermore, high-resolution, bidirectional implants are not only applicable in brain research, but also provide a significant improvement in the therapy of neurological disorders, as they allow closed-loop stimulation devices. During closed-loop stimulation, the recorded nervous signals are used to trigger a stimulation, to adapt the stimulation parameters like waveform or intensity to the reaction of the nervous tissue, or a combination of both [23, 27–29]. Several studies have shown, that this improves the stimulation efficacy and allows to adapt the stimulation process to the individual neural state of each patient.

By integrating more and more functionality onto a single System on Chip (SoC) the size, battery lifetime and functionality of neural implants could be improved over the last decades. This led to systems with 100 channels or more [21, 30, 31] and even a system with 1024 channels has been reported [32]. However, publications in the field of neurology show, that a pure increase in the amount of recording/stimulation sites is not the only way to go in order to improve therapeutic results. Besides the location of stimulation, many other parameters like stimulus waveform, stimulation duration and stimulation timing can severely influence the neural reaction [33–35]. The varying results from different experiments make it clear, that an integrated neural stimulator should offer maximum flexibility, in order to be adaptable to the neurological state of each individual patient.

A new obstacle, which arises through the growing channel count, is the increasing amount of data which must be transmitted from the implant to an external unit. With a bandwidth of the neural signals of approximately 10 kHz [3, 20], a sample resolution of 16 Bit and a channel count of 32 or more, a transmitter that is capable of transmitting several 10s of Mbit/s is required. This task becomes especially challenging with regard to the power budget and the limitations in antenna size, due to the small size of the implant.

In conclusion, this briefing shows that a versatile stimulator is needed, as it offers researchers maximum freedom in the design of neurological experiments and allows to adapt stimulation patterns to the individual needs of each patient. Additionally a highly integrated SoC is required in order to use the limited power and space in an implant to its full capacity. Therefore a fully integrated 32 channel, bidirectional neural interface has been developed in this thesis. The interface was implemented in a High Voltage CMOS (HV CMOS) technology, which allows the use of a High Voltage (HV) supply for stimulation, together with a Low Voltage (LV) supply for recording, thus increasing the stimulators voltage compliance, while maintaining a low noise recorder with low power and area consumption. During the design process three prototypes with increasing complexity were manufactured and evaluated and all results were combined into the final SoC. Additionally Ultra Wide Band (UWB) data telemetry was investigated, as it is reported to offer the best power efficiency for the required data rates and its high center frequency allow for small antenna dimensions.

FIGURE 1.1: Different implementations of FES and their key parameters.

### 1.1 Motivation

Neurological disorders like epilepsy, impairments caused by stroke or Parkinson's disease are a common global health-care problem. Motor recovery after a stroke is a large application field, mainly of neural recording, as loss of functional movement after a stroke is the main cause of acquired adult disability in high-income countries [36]. In this case, Brain Machine Interfaces (BMIs) can be used to bypass damaged brain areas and restore lost body functions or control prosthetic devices [19]. The second big research field for FES is the suppression of seizures in epilepsy or tremor in Parkinson's disease [37–40].

Epilepsy is the most common, serious, neurological disease, affecting approximately 50 million people worldwide [38], Parkinson's disease is the most common neurodegenerative disease affecting 1-2% of persons over the age of 60 years [39]. Although the symptoms of the majority of both patient groups can be efficiently treated with pharmacological medications, around one quarter of the epilepsy patients remain with drug-resistant epilepsy [38, 41] and approximately 50% of patients with essential tremor, caused by Parkinson's disease, do not improve with pharmacological medications [39]. In this case, clinical experience over the last decades has clearly shown, that FES can be used to dramatically reduce the symptoms and significantly improve the patients quality of live.

In the open-loop, neural FES approach, voltage, current or charge pulses are applied to one or several electrodes with a constant amplitude, duration and repetition frequency, which must be preliminarily determined, based on empirical values. Figure 1.1 illustrates the three different stimulation types together with their characteristic values. These stimulation parameters must be adjusted by a person with adequate training during a programming session [39], average values, e.g. for voltage stimulation in tremor patients, are reported with amplitudes of 2.4-4.4 V, a frequency of 143-173 Hz and pulse widths around 100 µs [42]. However, studies showed that more complex stimulation waveforms, e.g. an exponential decrease, can provide more energy and charge efficient stimulation

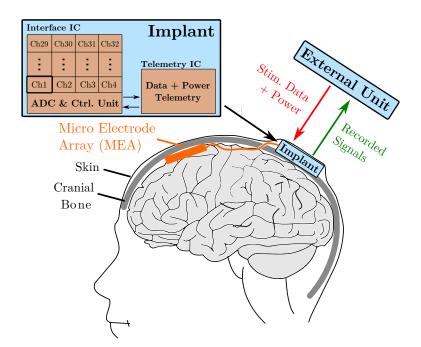

FIGURE 1.2: Conceptual neural modulator to stimulate and record the neural network of the human brain.

[33, 34, 43]. This allows to increase the battery lifetime of an implant and reduce the risk of tissue damage, as the amount of delivered charge can be reduced.

The next step to increase charge and power efficiency is to combine a neural recorder with a stimulation device and deliver on-demand stimulation pulses. This is done in closedloop FES, where not only the timing but also the stimulation amplitude can be changed, based on the recorded signal, leading to a more efficient treatment, while offering less side effects than continuous stimulation [37, 38]. Figure 1.2 shows the concept of a closed-loop BMI. It consists of an implant, which contains the electronics for wireless data and power telemetry, as well as the neural recording/stimulation front-end. The interface between electronics and the nervous tissue is provided by a Micro Electrode Array (MEA) with several tens up to more than a hundred separate electrodes for stimulation and recording [44], [21, 45]. The example shows the system design intended in this thesis, where every channel in the interface Integrated Circuit (IC) contains a combined recorder and stimulator, to allow parallel recording and stimulation and a shared Analog-to-Digital Converter (ADC) is used to digitize the recorded signals. A digital on-chip control unit manages the stimulation timing and the communication to the telemetry unit, which provides a wireless data and power link to an external unit. Thereby no wired connections through the scalp are required, which minimizes the risk of infections and inflammations.

In the shown example, the raw, recorded data is streamed out to the external unit which has two major advantages. First, it allows to store all recorded data on a mass storage device, which is especially important for researchers, as offline signal analysis can be performed. Second, the available computation power in an external unit is much higher compared to the implanted device, since the power budget is strictly limited by the heat flux of the implant. In order to limit its heating to less than 1 °C, the implanted device must not exceed a heat flux of  $65 \,\mathrm{mW/cm^2}$ , which sets, together with the limited space, the overall power budget [46, 47]. Therefore, complex and power hungry signal processing algorithms are put outside the body, were more area is available and more heat can be dissipated without tissue damages.

In order to estimate the required data rate in this scenario, the bandwidth of the expected signals that will be recorded can be analyzed. In extracellular neural recordings the signal can be spectrally separated into low frequency Local Field Potentials (LFPs) and high frequency Action Potentials (APs). LFPs are located between 0.5-200 Hz with amplitudes in the range of  $5 \mu$ V to  $5 \,\text{mV}$ , APs are located between  $0.2-7.5 \,\text{kHz}$  with 5-10 times smaller amplitudes [48, 49]. This results in an overall bandwidth of  $7.5 \,\text{kHz}$  for the neural signal, which requires a sampling rate of at least  $15 \,\text{kS/s}$  to avoid aliasing. In order to ensure that the signal quality is not limited by the quantization error of the ADC a resolution of 16 bit is chosen in commercially available systems [50]. If we increase the sampling rate to  $20 \,\text{kS/s}$  to account for non-ideal filtering of the recorded signal, the required data rate per channel  $R_{ch}$  can be calculated to:

$$R_{ch} = 20 \, kS/s \cdot 16 \, bit/S = 320 \, kbit/s \tag{1.1}$$

Many recent publications about implantable data links use the Impulse Radio Ultra Wide Band (IR-UWB) technique, as it offers high data rates, combined with high power efficiency and a license free use. Modern Complementary Metal-Oxide-Semiconductor (CMOS) technologies allow to design power efficient implementation of transmitters that use the frequency band between 6-8.5 GHz, which can be combined with on-chip data encoding or even be included in a neural recorder SoC [51]. The reported transmitters provide data rates of up to 230 Mbit/s, which is enough to transmit the raw data of more than 100 channels, with a power consumption of less than 4 mW [52–54].

The main motivation of this thesis is to combine a neural recorder, a neural stimulator, the digital control logic required to control the stimulation process and a high resolution ADC on one chip, in order to allow extremely area and power efficient implants. A second goal is to extend the capabilities of the on-chip neural stimulators in order to allow arbitrary stimulation waveforms in current mode, as well as in voltage mode with one device. This would give researchers as well as clinicians a powerful tool with maximum flexibility in the design of experiments and the possibility to adapt therapies to the needs of individual patients.

To achieve this goal, different stimulator and recorder architectures were considered during this research work, which are discussed within this thesis. A newly developed architecture is shown that combines recorder and stimulator, while providing voltage and current mode stimulation with minimal area and power overhead. Additionally an improved recorder architecture that offers on-chip, signal adaptive bandwidth tuning and bioimpedance estimation is presented. All presented solutions were verified with 5 prototypes, manufactured in a 180 nm HV CMOS technology.

### **1.2** Achievements and innovations of the research work

This section highlights the achieved findings of this work for biomedical modulators. Furthermore, the specific innovations for neural recording as well as for the neural stimulator are shortly presented.

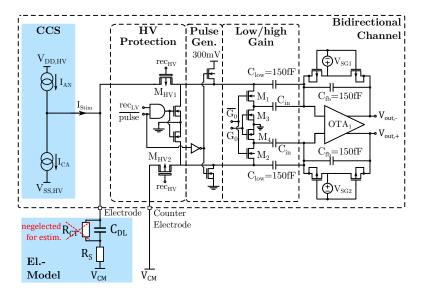

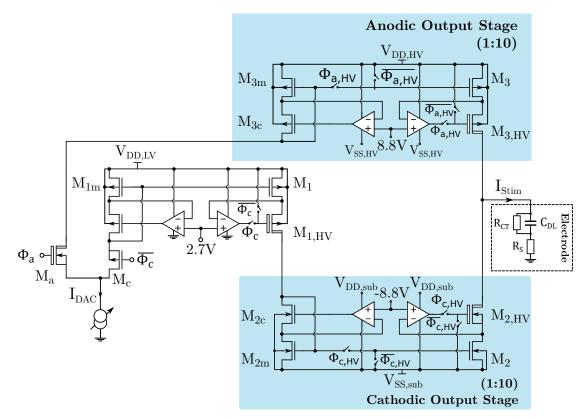

The starting point of this thesis was a 32 channel neuromodulator design presented in [55], which featured 32 low noise recording front-ends. However, there was no onchip stimulator included, but only 32 HV transmission gates were used to direct the stimulation current of an external stimulator to one of the working electrodes. Therefore, the first task in this thesis was to find a stimulator architecture, which allows to be combined on-chip with the existing neural recorder. In the first approach, a HV, biphasic, current mode stimulator was designed, in order to provide a large voltage compliance, which is required for small, high-impedance electrodes. During stimulation phases the recorder is protected from the potentially harmful voltage levels via HV switches. The combined, bidirectional front-end was realized in a 180 nm HV-CMOS technology and provides measured stimulation currents of up to  $\pm 10.2$  mA with an output compliance of  $\pm 8$  V. Arbitrary stimulation waveforms were realized with a 5-bit current steering Digital-to-Analog Converter (DAC), whose Dynamic Range (DR) was increased to more than 50 dB by an additional output range selection. The recorder features a measured, input referred noise of  $3.3 \,\mu V_{\rm rms}$  in the LFP and the AP band [16].

In a second revision of the stimulator, its functionality was extended by a constant voltage stimulation mode. This was achieved by a semi-digital feedback loop, which controls the stimulation current in order to adjust the electrode potential to the desired stimulation voltage. This novel architecture allows for the first time to fully reuse the area consuming HV output stage of a current stimulator in order to achieve voltage mode stimulation. Therefore, a very high area and power efficiency is achieved, with an area overhead of only 11 % for the bidirectional channel and less than 1  $\mu$ W of additional power consumption [14].

The second task in the thesis focused on the recording of neural data and to make it more versatile for a broader variety of applications. Since not the entire bandwidth from 1 Hz to 7.5 kHz is of interest in every experiment, a tunable high-pass cut-off frequency was introduced to the Low Noise Amplifier (LNA). This allows a flexible trade-off between recorder bandwidth and noise performance, which makes the recorder more adaptable to the desired neural signal. Additionally, a 0 dB low gain mode was introduced, which can be used to estimate the bioimpedance of the used electrode in combination with the current mode stimulator. This increases patient safety, as electrode degradation and ripoff can be detected and the stimulation waveforms can be adjusted accordingly [13].

Both results, from the development of the stimulator and the revision of the recorder, resulted in the design of a 32 channel fully-integrated, bidirectional neural interface. It combines a high resolution incrementel  $\Delta\Sigma$  ADC (I $\Delta\Sigma$ -ADC), the digital control logic for stimulation and recording and 32 bidirectional neural front-ends. This allows to reduce the number of components that are required for a neural implant, which tremendously reduces the size and power consumption.

Therefore, the results in this thesis can be used to improve the State-of-the-Art (SoA) in implantable neuromodulators, not only by decreasing their size and power consumption: Additionally the extended functionality allows more patient safety, increases the freedom in the design of experiments in research and makes the implant more adaptable to the individual needs of patients. This can help neurologists in future work to further extend the knowledge about function mechanisms in the central nervous system and even provide new therapeutic measures for neurological disorders.

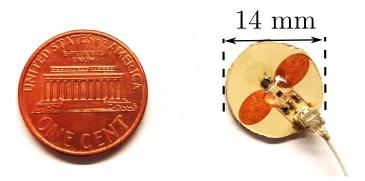

In the last part of this work, the already mentioned wireless data link, which is needed to stream the data to an external unit, was investigated as an outlook for further developments. This led to a first, successful design and testing of a miniaturized UWB transmitter, which is capable of delivering data rates up to 100 Mbit/s. Its small form factor, power consumption and the measured robustness to environmental change make it very promising for implantable, transcutaneous high-speed data transmission [18].

### **1.3** Outline of the thesis

This thesis is organized in 6 chapters. Chapter 1 gives a general introduction into the topic of neuromodulation and highlights the work that was done in this thesis. The second chapter explains the signaling mechanisms in the central nervous system between

the fundamental, functional units, the neurons. This is used to derive the nature of the observable, neural signals, how these can be measured using integrated circuits and finally how brain activity can be electrically modulated. After deriving these fundamentals, Chapter 3 shows the neural recorder design, which was developed during this work, explains novelties that were realized and how they improve patient safety, as well as signal quality. In Chapter 4, the integrated, high voltage, neural stimulator is shown and how the sensitive neural recorder can be protected from potentially harmful stimulation events. A novel, semi-digital feedback architecture is presented, which allows reconfiguration between current and voltage mode stimulation, achieving outstanding area and power efficiency. Thereafter, the implemented 32 channel neuromodulator is presented in Chapter 5, explaining in detail the utilized on-chip, digital waveform synthesis, on-chip analog-to-digital conversion and the supporting analog circuitry. Finally the thesis is concluded in Chapter 6 and an outlook on possible, future work in the field is given.

### Chapter 2

# Background and State of the Art

In this chapter, the principal structure of a neuron and its communication mechanisms are explained. Followed by this, the nature of electrical, neural signals will be explained, which can be derived from the fundamental working principle of a neuron. It is important to understand the working mechanisms that lay behind these signals, in order to successfully interface and record them, as well as to electrically stimulate a desired neurological response. The second section of this chapter describes how nervous tissue can be interfaced with electronics and what the resulting possibilities for signal recording and neural stimulation are. Additionally, an overview of neurological disorders that can be treated with electrical stimulation of the Central Nervous System (CNS) is given. To close the chapter, the SoA in circuits used for neural interfaces is reviewed and a selection of architectures is compared against each other.

### 2.1 Central nervous system

The CNS consists of the spinal chord and the main part of the whole nervous system, the brain. It consists of approximately  $10^{12}$  neurons [56], which communicate amongst each other and thereby allow us to perceive our environment and control our body. Understanding the complex working mechanisms that underly the overall functioning has been a major area of research, on a cellular level as well as on a more macroscopic, anatomical level.

#### 2.1.1 Anatomy and function of the neuron

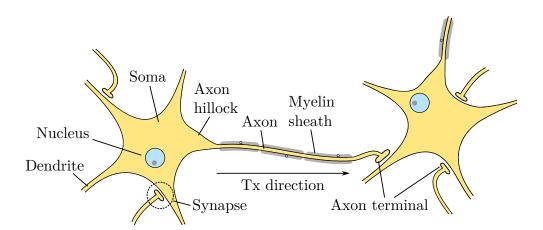

Figure 2.1 shows the anatomy of a neuron, the fundamental functioning unit of the nervous system, and its connection to a second neuron. Starting on the left side, the

FIGURE 2.1: Anatomy of a multipolar neuron.

neuron consists of the cell body (*soma*), to which two different types of extensions are connected:

- *Dendrites* are the receiving part of the neuron, where the synapses of other neurons end. A neuron can have several dendrites, with complex branching.

- The *Axon* is the transmitting part of the neuron and propagates signals to other neurons or other types of cells (e.g. muscles). Every neuron has only one axon, which is usually enclosed by a myelin sheath [57].

The dendrite is the part of the neuron that receives the input from one or several previous neurons via the synapses. If a signal arrives at the axon terminal, a neurotransmitter is released into the synaptic cleft, where it propagates to the dendrite of the next neuron. Depending on the type of neurotransmitter, this excites signal propagation by depolarization or inhibits signal propagation by hyper polarization of the adjacent neurons membrane voltage. All incoming signals are integrated at the axon hillock, where an all-or-nothing decision is made, meaning if the membrane voltage stays below a certain threshold no signal is propagated at all. However, if it reaches the threshold a new action potential (AP) is generated at the axon hillock and propagates along the axon to the next axon terminal.

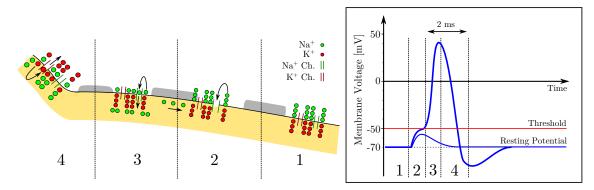

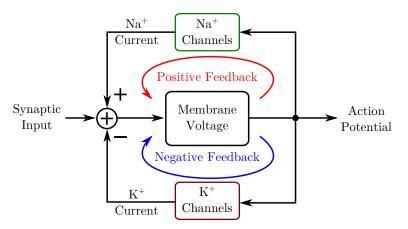

Figure 2.2 illustrates the propagation of an AP along the axon. For simplicity only Na<sup>+</sup> and K<sup>+</sup> ions are shown, as these are the ones responsible for AP propagation. In the absence of an excitation, a voltage difference between the intracellular and the extracellular potential of about -70 mV is observable, the so called resting potential (Figure 2.2 (1)). This is maintained by Na<sup>+</sup>, K<sup>+</sup> and Cl<sup>-</sup> channels as well as Na<sup>+</sup> and K<sup>+</sup> ion-pumps. If the cell is depolarized above the marked threshold value, e.g. by synaptic excitation or by an AP event along the axon, the voltage-gated Na<sup>+</sup> channels open (Figure 2.2 (2)), allowing more Na<sup>+</sup> ions to flow into the neuron along their concentration gradient. This

FIGURE 2.2: Propagation of an AP along a myelinated axon and the resulting membrane voltage over time, based on [1].

FIGURE 2.3: Feedback mechanisms in the propagation of APs, based on [2].

current leads to further depolarization, which opens even more Na<sup>+</sup> channels, until a maximum membrane voltage of approximately 40 mV is reached (Figure 2.2 (3)), where the Na<sup>+</sup> channels close again. The K<sup>+</sup> channels have a delayed reaction, which leads to a dominant K<sup>+</sup> current at the peak of the AP, causing the membrane voltage to drop back to its resting potential, after an observable undershoot, called hyper polarization [2]. After an AP event the initial concentration levels are gradually restored by sodium-potassium-pumps.

The described process can be modeled by two feedback loops as illustrated in Figure 2.3. If a synaptic input depolarizes the membrane voltage above the threshold value, the positive, sodium feedback loop amplifies the received signal to the full AP level. After that, the negative, potassium feedback loop restores the resting potential and brings the neuron back to its initial state. This signal triggering can be used to stimulate nerve cells by electrical depolarization, as it will be explained in section 2.4.

FIGURE 2.4: Comparison of different recording approaches regarding spatial and temporal resolution, derived from [3].

#### 2.1.2 Observable neural signals

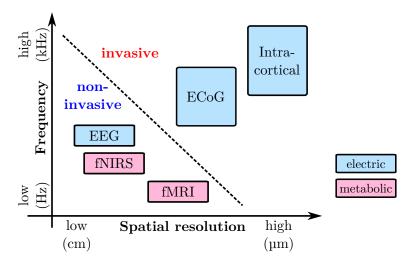

In the previous section the general propagation mechanism of neural signals was described. Many approaches exist to record this communication between neurons, which make use of different measurands that indicate neural activity. In the chemical domain, direct measurement of neurotransmitter concentration is applied, mainly in in-vitro experiments, where it can be used for early drug screening and drug discovery [58]. Another method is Functional Magnetic Resonance Imaging (fMRI) and Functional Near-Infrared Spectroscopy (fNIRS), where haemodynamic changes are measured to locate enhanced neural activity and thereby study sensory processing, control of action or draw conclusions about neural mechanisms [59]. Figure 2.4 compares all recording approaches which can be used for BMIs, regarding invasiveness and spatiotemporal resolution [3].

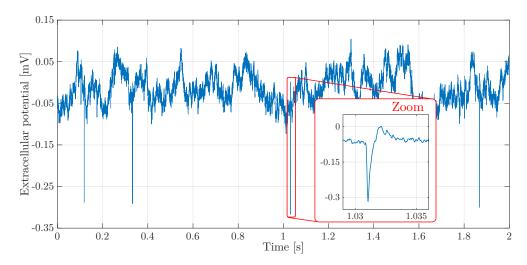

It is clear that a trade-off between spatiotemporal resolution and invasiveness has to be found for BMIs. Most commonly, implantable systems that use Electrocorticography (ECoG) or intracortical electrodes are chosen, since they offer the highest spatiotemporal resolution and can be recorded with highly integrated, area and power efficient devices. Figure 2.5 shows the unfiltered, recorded extracellular potential from the prefrontal cortex of a sleeping rat [4, 5]. The signal can be spectrally divided into two parts, in the lower frequency band located between  $f_{\rm LFP} = 0.5 - 200 \,\text{Hz}$  are the local-field-potentials (LFP) and in the higher frequency band located between  $f_{\rm AP} = 200 \,\text{Hz} - 7.5 \,\text{kHz}$  are the action potentials (AP).

APs or spikes are caused by the rapid change in the extracellular potential when an excitation is propagated along an axon, as described in subsection 2.1.1. Therefore, the same characteristic waveform, which was previously explained with the two feedback loops, can be observed as shown in the zoom in Figure 2.5. However, the maximum

FIGURE 2.5: Recorded, extracellular potential of a sleeping rat, showing LFP and AP signal parts; Signals from [4, 5].

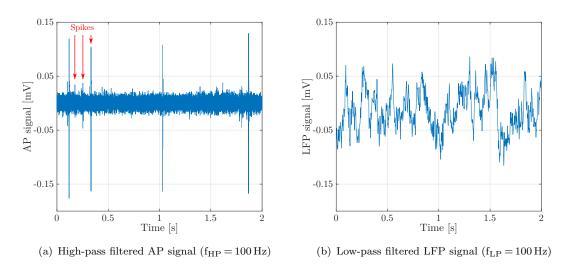

FIGURE 2.6: Neural signal filtered with 6th order Butterworth filter; Signal from: [5].

amplitude is much smaller than the amplitude shown in Figure 2.2, as only the change in extracellular potential is measured and not the actual membrane voltage. Additionally, the signal is damped because of the distance between the recording electrode and the axon, which results in observable signal amplitudes in the order of  $100 \,\mu$ V. The low frequent LFPs are caused by synchronous activity of many neurons in a certain region of the brain. As these neurons are too far away from the recording electrode their individual spikes can't be resolved, however the "crowd noise" of their increased activity produces a large signal which can be easily observed [49].

The waveforms shown in Figure 2.6 have been extracted using a low-pass and a highpass 6th order Butterworth filter, each with a cut-off frequency of 100 Hz to separate the LFP and the AP signal. This high-order filtering accentuates the rapid rising edges of the spikes, which results in filter artifacts that look like additional, positive spikes.

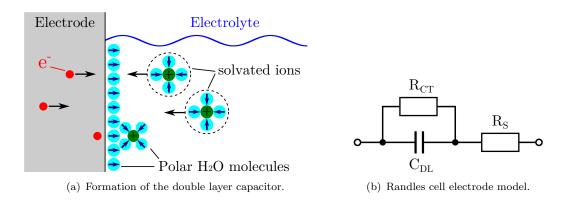

FIGURE 2.7: Non-Faradic reactions at the electrode-electrolyte interface, based on [6].

Furthermore, the filtered signal shows more spikes with different amplitudes and waveforms. This is the case, because usually more than one neuron is close enough to the recording electrode, such that their spikes can be resolved. The filtered AP signal even allows to distinguish between different neurons by applying spike sorting algorithms, as every neuron has its individual spike waveform, based on its physiological condition [60].

# 2.2 Interfacing of nervous tissue

While brief, intracellular recordings are possible using individually guided microelectrodes [49], the majority of interfaces between electronics and nervous tissue is provided by electrodes that record the extracellular potential. These electrodes consist of electrically conductive material, usually some kind of noble metal, which is in direct contact with the brain fluid, but can differ in form, size and the used materials [61]. In the following the signal transporting mechanisms and the resulting electrical model is explained and how the electrode properties influence the parameters of the electrical model.

#### 2.2.1 Electrode-electrolyte interface

If metal electrodes are used, three different mechanisms exist that transfer the electron based signal conduction within the metal into an ion based signal conduction in the electrolyte: capacitive charge transfer, electrochemical reactions and redox reactions. Figure 2.7(a) shows the reversible, capacitive mechanism, which is dominant at small voltages over the phase boundary and not associated with any electrochemical reaction. In principle, a capacitor is formed by the electrons in the metal, a first isolation layer of water molecules that are adsorbed at the metal surface, a second layer of water molecules around the solvated ions and the ions itself as the opposite charge carriers [6]. This process is mainly responsible for generating the recordable neural signal and

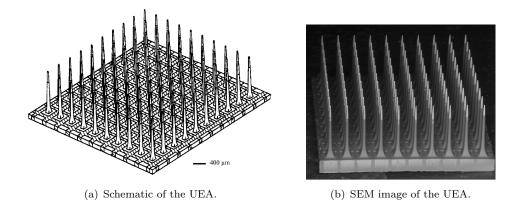

FIGURE 2.8: The 10 x 10 Utah electrode array (UEA) [7].

the desired method for stimulation, as for higher voltages, irreversible, electrochemical reactions start. These reactions occur, when charges cross the phase boundary and lead to changes in the chemical composition of the electrode-tissue interface, which can produce cytotoxic substances. Therefore, electrode voltages must be kept within certain, material dependent limits, to ensure patient safety.

If an electrode is operated within its reversible limits, the electrode-electrolyte interface can be modeled with the Randles cell electrode model shown in Figure 2.7(b). It consists of the double layer capacitor  $C_{DL}$ , which is caused by the aforementioned non-Faradic reactions, the solution resistance  $R_S$  that models the current flow in the solution and the reaction, or charge transfer resistor  $R_{CT}$ , which models the undesired, electro-chemical reactions [62]. In order to provide a good electrode for stimulation and recording, a large  $C_{DL}$  together with a small  $R_S$  is required. This allows on the one hand side to transfer a certain current density, which is required to achieve a stimulation effect, without large electrode voltages and on the other hand side a good Signal to Noise Ratio (SNR) during recording, as the resulting electrode impedance is equivalent to the signals source impedance [63].

#### 2.2.2 Implantable electrodes

Implantable electrodes for neural recording and stimulation come in many different shapes, materials and with varying mechanical properties. One possible characteristic which can be used to group the existing MEAs is between intracortical electrodes, where the electrodes penetrate the brain tissue and ECoG electrodes that record signals from the cortical surface. While intracortical MEAs offer high spatial resolution from high impedance electrodes, ECoG offers larger electrodes with lower electrode impedance and is likely to have greater long-term stability and patient safety [64].

FIGURE 2.9: Commercially available 8x8 ECoG electrode array (CorTEC - AirRay) [8].

The most prominent example of an intracortical MEA is the commercially available Utah Electrode Array (UEA) that is shown in Figure 2.8. It consists of 100 electrodes, with a length of 1.5 mm and a spacing of 400 µm that are fabricated on a silicon substrate. This allows wafer scale fabrication with adapted processes from CMOS manufacturing, which leads to comparably low costs and low variances in the electrode parameters. The well established, silicon based processing allows the manufacturing of the smallest electrodes available, which results in a very high spatial and temporal resolution [7]. Another advantage of penetrating electrodes is that they provide maximum signal amplitudes for AP recording, as the distance between electrode and neuron is minimized. However, this method comes with the disadvantage that the brain tissue is damaged during the insertion of the array into the brain. Although studies showed that useful signals can be acquired even 9 months after implantation, still concerns exist about longterm tissue reactions, e.g. caused by micro movement and encapsulation [65]. Another major drawback lies in the stimulation capabilities of these electrodes, which comes from the unavoidable trade-off between charge capacitance and electrode size. The electrodes double layer capacitance, which determines its charge capacity and thereby the stimulation capability, can be calculated as follows.

$$C_{DL} = \varepsilon_r \cdot \varepsilon_0 \cdot \frac{A}{d_H} \tag{2.1}$$

This is a first order approximation of  $C_{DL}$  as a parallel plate capacitor, where A is the effective area of the electrode and  $d_{\rm H}$  is the thickness of the water layer between the ions and the electrode [6]. Due to their small, physical size, the shown electrodes have only a comparably small  $C_{\rm DL}$ , thus offering only limited stimulation capabilities.

A different approach is the use of planar electrodes on a flexible substrate, e.g. silicone rubber that are either placed directly on the brain tissue or very close to it on the dura. Compared to the previously described intracortical implantation, this method

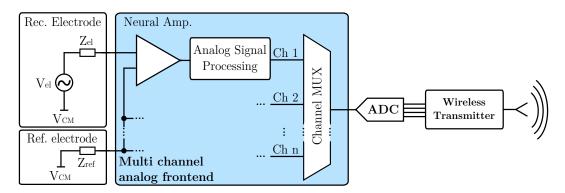

FIGURE 2.10: System level diagram of a multi channel neural recorder.

is less invasive, as it does not mechanically damage the tissue during implantation. Additionally, the increased electrode size provides lower electrode impedance and higher charge capacities, which allows for higher stimulation intensities. However, the drawback of this technique is that spatial resolution is lost because of the increased minimum electrode size, which is manufacturable with this technique. Additionally, the neural signal is spread due to the further distance of the electrodes to the neurons, resulting in a further loss of spatial resolution. A second disadvantage is that the maximum number of electrodes per area is lower [3], due to the increased electrode size.

# 2.3 Integrated recorders for implantable BMIs

As shown in the previous section, many different approaches are used to provide interfaces between neural tissue and electronics. As this thesis is focused on ICs for implantable BMIs, an overview of the SoA in ICs for recording of ECoG and intracortical signals is given in this section, followed by stimulation ICs and bidirectional interfaces in section 2.4.

Extracellular neural signals impose several challenges to an integrated recorder due to the high impedance of the electrode, the small signal amplitudes and DC voltages in the range of tens of mV that occur at the electrode-electrolyte interface. Figure 2.10 shows a typical multi-channel recorder front-end, where each channel has its own neural amplifier, which is the most critical stage in the design due to the following key parameters [49].

- *Input impedance*: Due to the high electrode impedance the first stage needs to provide a large input impedance to avoid excessive loading of the signal source.

- *DC suppression*: DC offsets from the electrode-electrolyte interface must be suppressed to avoid amplifier saturation.

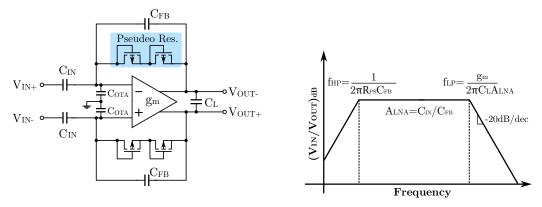

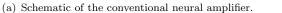

FIGURE 2.11: Capacitive coupled neural amplifier with pseudo-resistor feedback [9].

- Noise: Since the amplifiers input referred noise is directly added to the signal, it must provide an integrated noise in the μV range to resolve AP signals.

- Dynamic range: The dynamic range muist be large enough to resolve spikes and LFPs  $(10 \,\mu V \text{ to } 2 \,\mathrm{mV})$  at the same time.

- *Gain*: Sufficient gain must be provided to alleviate noise requirements on the following stages.

- Recording bandwidth: In order to record LFPs and APs a bandwidth of  $f_{min} \leq 1 \text{ Hz}$  to  $f_{max} \geq 5 \text{ kHz}$  is required.

If the neural amplifier provides a low impedance output and eliminates the DC offset, the input impedance and DC suppression issue is resolved in this stage. Additionally, Friis formula shows that the noise of the following stages will be suppressed by the gain of the neural amplifier. These points make it obvious that the first stage is the most challenging element, but reduces requirements on all following stages.

#### 2.3.1 Conventional architecture

In the conventional architecture, MOS based pseudo resistors are used to overcome the area limited resistance of integrated feedback resistors which was first published in a photo receptor architecture [66]. In Figure 2.11(a) the schematic of the adaption to a fully differential, AC coupled, neural amplifier is shown [67]. It uses AC coupling over the input capacitors  $C_{IN}$  in order to block DC offsets from the electrode and two pMOS diodes which act as pseudo resistors in the feedback, to set the input common mode of the Operational Transconductance Amplifier (OTA) and to generate a high-pass corner frequency in the sub-Hertz range.

Figure 2.11(b) shows the bandpass transfer function of the amplifier. The passband gain  $A_{LNA} = \frac{C_{LN}}{C_{FB}}$  is determined by the ratio of the input and the feedback capacitor which allows a well defined gain in a CMOS application, since capacitor mismatch can be designed to be in the sub-percent range. In the feedback path,  $C_{FB}$  and the pMOS pseudo resistor define the high-pass cutoff frequency  $f_{HP} = \frac{1}{2\pi R_{PS}C_{FB}}$ , where  $R_{PS}$  is the small signal resistance of the pseudo resistor. The innovation in this design was the use of the pseudo resistor which allows an area efficient CMOS implementation, by realizing huge on-chip resistors. If the absolute voltage over the pseudo resistor stays small enough to keep the MOS transistor and the intrinsic bipolar transistor off,  $R_{PS}$ can reach values of several T $\Omega$ s [67]. This allows to choose  $C_{FB}$  in the range of hundreds of fF to achieve a high-pass corner frequency below 1 Hz which can not be realized with conventional integrated RC elements, since the required silicon area would exceed the available area budget.

In the described architecture, the input capacitor  $C_{IN}$  is usually the dominating area consumer. To achieve the desired gain, it must be sized  $A_{LNA}$ -times bigger than  $C_{FB}$ which itself is limited in minimum size by technology constraints and the desired highpass frequency. Additionally,  $C_{IN}$  must not be chosen arbitrary small, as a capacitive voltage divider between the parasitic input capacitor  $C_{OTA}$  of the OTA and  $C_{IN}$  lead to a damping of the neural signal, thus reducing the SNR. According to [67] the input referred noise of the neural amplifier  $\overline{v_{n,LNA}^2}$  can be derived from the OTA input referred noise  $\overline{v_{n,OTA}^2}$  as follows:

$$\overline{v_{n,LNA}^2} = \left(\frac{C_{IN} + C_{FB} + C_{OTA}}{C_{IN}}\right)^2 \cdot \overline{v_{n,OTA}^2}$$

(2.2)

This shows the noise penalty factor which increases with the parasitic input capacitor. However, due to the low frequency band of the LFP signals, the OTA needs to provide a low 1/f-noise corner frequency which can only be achieved by increasing the gate area of the input devices. Therefore, good 1/f-noise performance comes with an increase of the parasitic input capacitor  $C_{OTA}$  in this architecture, requiring again for larger input and feedback capacitors. This results in a fundamental trade-off between integrated noise in the LFP band and circuit area which limits the performance of this architecture.

Another disadvantage of this architecture is that the lower cut-off frequency is only poorly designed during design time, as the absolute value changes with process- and temperature variations. A linearized approximation of the pseudo resistor value around its operating point at  $V_{DS} = 0$ , can be calculated using the EKV model [68]:

$$R_{PS}\Big|_{V_{DS}=0} = \frac{U_T}{I_{D0}}$$

(2.3)

Where  $U_T$  is the thermal voltage and  $I_{D0}$  the transistor dependent, residual channel current.  $I_{D0}$  can be calculated from the subthreshold slope n, the gate oxide capacitance per unit area  $C_{ox}$ , the transistors width W and length L and the pMOS threshold  $V_{T0}$  as followed.

$$I_{D0} = 2n\mu C_{ox} \frac{W}{L} U_T^2 e^{\frac{-V_{T0}}{nU_T}}$$

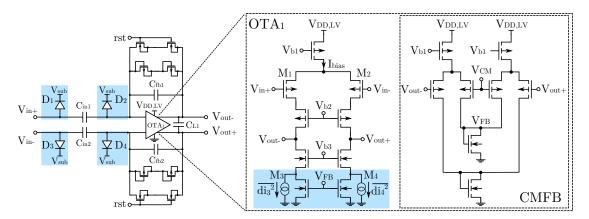

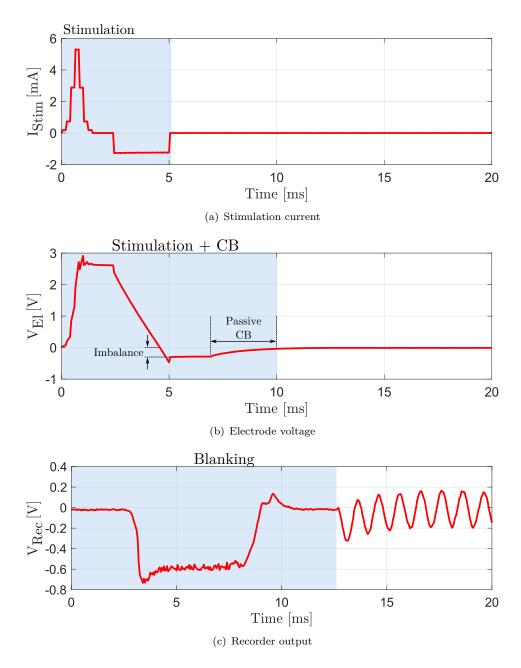

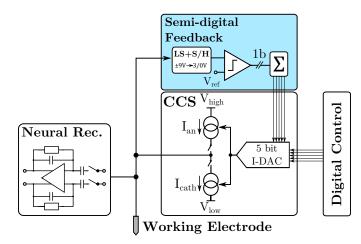

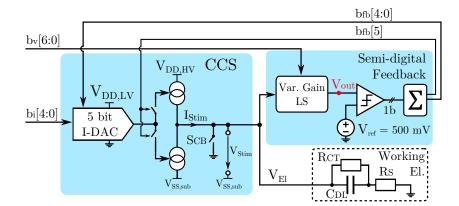

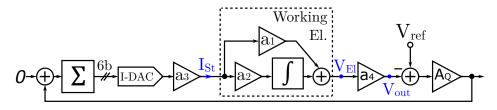

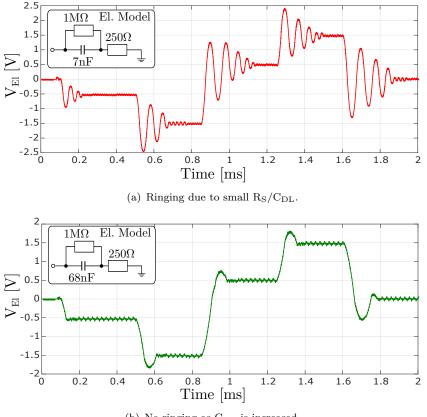

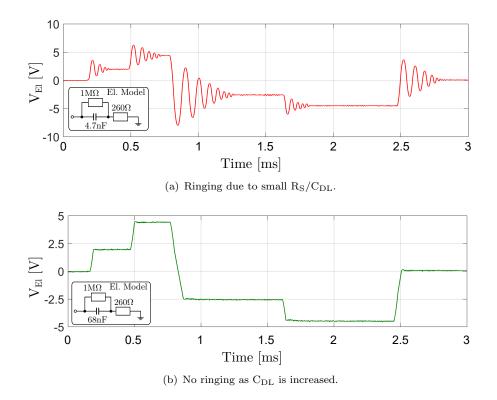

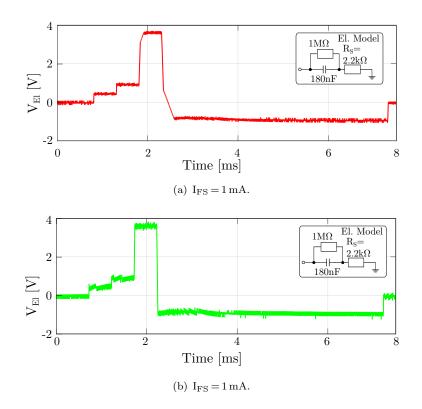

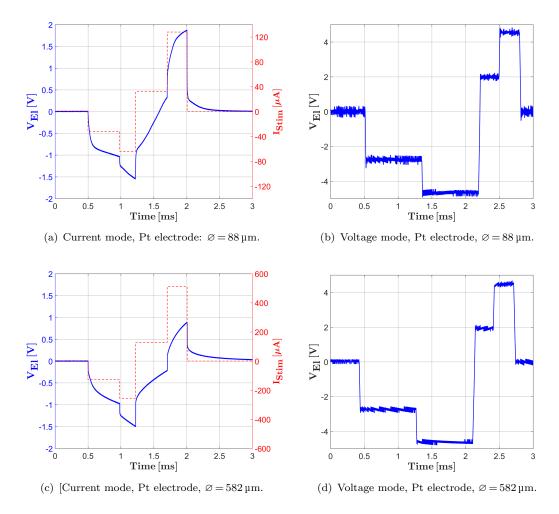

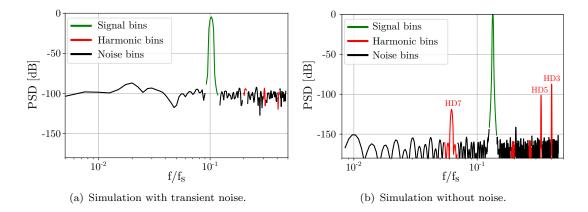

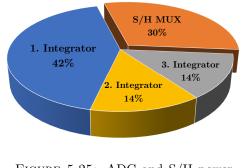

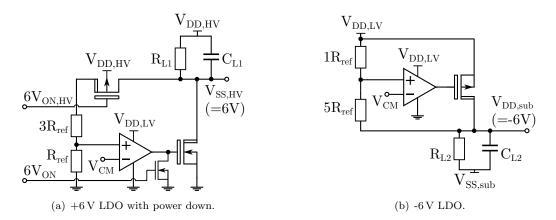

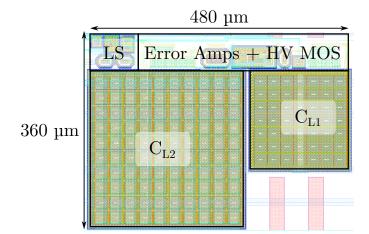

(2.4)