### Pseudomorphic and metamorphic HEMT-technologies for industrial W-band low-noise and power applications

# DISSERTATION

zur Erlangung des akademischen Grades eines

# DOKTOR-INGENIEURS (DR.-ING.)

der Fakultät für Ingenieurwissenschaften und Informatik der Universität Ulm

von

### JAN ERIK GRÜNENPÜTT

### AUS HEIDENHEIM A.D. BRENZ

Gutachter:

Prof. Dr.-Ing. Erhard Kohn Prof. Dr. Christophe Gaquière

Amtierender Dekan: Prof. Dr.-Ing. Michael Weber

Ulm, 14. Dezember 2009

This work has been prepared from January 2001 to March 2009 at United Monolithic Semiconductors GmbH, and the University of Ulm, department of electron devices and circuits.

Parts of this work have already been published:

J. Grünenpütt, C. Gässler, D. Geiger, R. Deufel, C. Woelk, E. Kohn, "Selective double recess technology on metamorphic HEMTs improving the onstate breakdown behavior", Technical Digest CS-MAX, San Jose, CA, Nov 2002

A. Bessemoulin, C. Gaessler, J. Gruenenpuett, B. Reig, "Hot via-interconnects: A Step towards Surface Mount Chipscale Packaged MMICs up to 110GHz", Technical Digest: 26<sup>th</sup> IEEE CSIC Symposium, Monterey, Oct. 2004

J. Gruenenpuett, C. Gaessler, C. Gaquière, E. Kohn, "800mW/mm power density @ 94GHz for a 70nm-pHEMT technology", Technical digest CS-MAX04, Monterey, Oct. 2004

A. Bessemoulin, J. Gruenenpuett, P. Fellon, A. Tessmann, E. Kohn, "Coplanar W-Band Low Noise Amplifier MMIC Using 100-nm Gate-length GaAs PHEMTs", 12<sup>th</sup> GaAs Symposium - Amsterdam, Oct. 2004

A. Bessemoulin, P. Fellon, J. Grünenpütt, A. Tessmann, H. Massler, W. Reinert, E. Kohn, "High gain 110GHz Low Noise Amplifier MMICs using 120nm Metamorphic HEMTs and Coplanar Waveguides", 13<sup>th</sup> GaAs European Microwave Week, 2005

C. Gaquière, J. Grünenpütt, D. Jambon, E. Delos, D. Duccatteau, M. Werquin, D. Théron, P. Fellon, "A High Power W-Band Pseudomorphic InGaAs Channel PHEMT", IEEE Electron Device Letters, vol. 26, Aug. 2005, pp. 533–534

# **Pseudomorphic and metamorphic HEMT-technologies for industrial W-band low-noise and power applications**

**Abstract:** The W-band ranging from 75 to 110 GHz marks a frequency window of low atmospheric absorption which is suited for high bandwidth data transmission but also for radar applications. Especially the 94 GHz absorption minimum is used for cloud profiling radars to detect rain from satellites. Active radar systems are found for traffic control on runways but also to identify debris as a severe danger to the safety and integrity of aircrafts. Multi channel passive radar imaging allow the detection of concealed weapons at security gates. With an increased demand for such security systems there is a growing market for W-band low noise and power amplifiers to be addressed by industry.

Up to 77 GHz integrated circuits are realized by commercial 150 nm gate length pseudomorphic high electron mobility transistors (pHEMT). To address higher frequency levels, the active devices have to provide more gain. The development and fabrication of such devices are part of this work, where fabrication processes have to be compatible with the 4"-fabrication environment of United Monolithic Semiconductors including the industry requirements regarding fabrication yield and device reliability. Besides the progression of the pHEMT technology by down scaling of the gate length to 80 nm, two single recess and one double recess metamorphic HEMT technology on GaAs substrate have been developed to improve the RF-gain by the superior transport properties of the low bandgap  $In_xGa_{1-x}As$  channel. A channel indium concentration of 60 % and 43 % has been investigated for device optimization depending on the application such as low-noise and power.

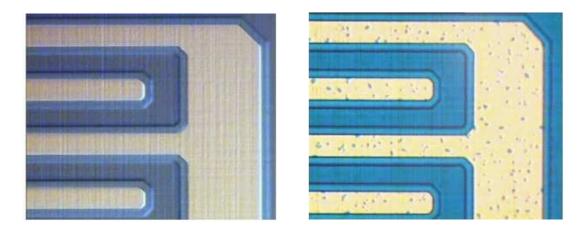

After a general discussion of the pseudomorphic and metamorphic HEMT structures including the gate recess configuration and device breakdown, the fabrication modules and optimizations referring to the particular technology are presented with respect to reproducibility and fabrication yield. An acceptable wafer fabrication yield of 73 % with good prospectives for further improvement has been realized for the pHEMT technology. The fabrication yield of 26 % for the metamorphic low-noise technology is low and does not comply with the production requirement of 60 %. MESA-isolation in combination with device passivation at temperatures above 250°C has been identified to be responsible for the low yield and requires further optimization.

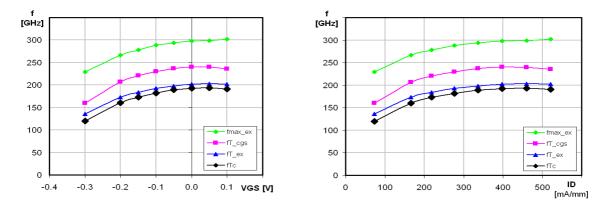

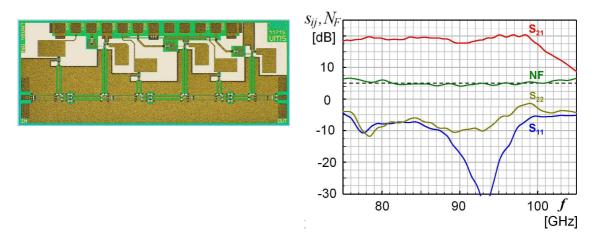

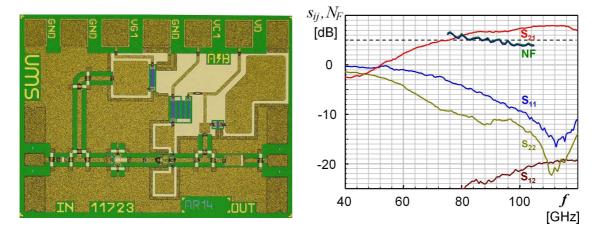

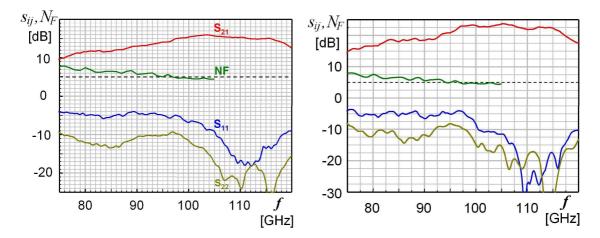

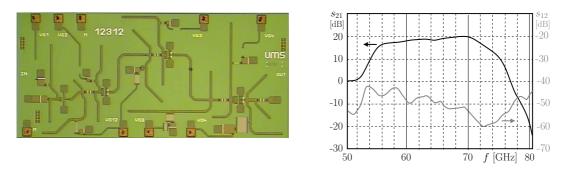

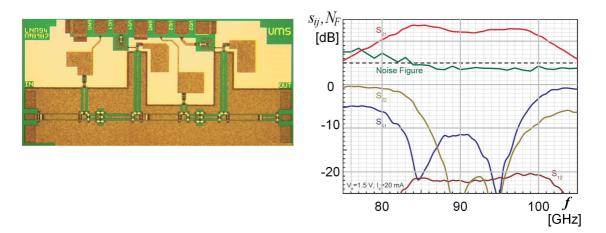

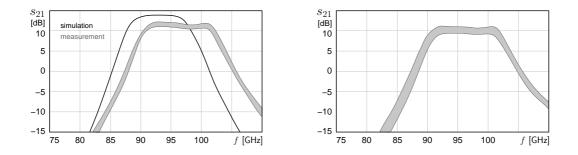

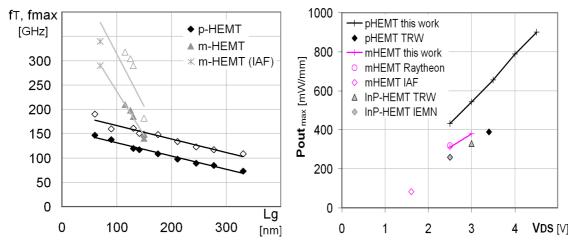

The 120 nm low-noise metamorphic HEMTs show a transit frequency of 200 GHz and a maximum oscillation frequency around 300 GHz. The associated gain of 5.4 dB at 94 GHz with a noise figure of 3 dB is in line with institute results for well passivated devices. Several low-noise demonstrator amplifiers are presented providing a gain of 6 dB per stage at 94 GHz with noise figures around 4.5 dB. Similar performances have been demonstrated by a two-stage common source low noise amplifier fabricated with the pseudomorphic HEMT technology. Although not optimized for low-noise the pHEMT demonstrator had even the lower noise figure of 3.7 dB.

The metamorphic power technology provides state-of-the-art performance with a power density of 380 mW/mm at 94 GHz and a linear gain of 8.5 dB for 3 V operation. Despite a high off-state breakdown voltage above 10 V, the devices cannot be operated at

higher voltage levels due to impact ionization related device burn-out. The pseudomorphic HEMT technology is less sensitive towards impact ionization because of the higher bandgap in the channel. Although the off-state breakdown voltage of the pseudomorphic HEMT of 6.5 V is considerably low, the devices can be operated up to 4.5 V and demonstrate state-of-the-art output power densities up to 900 mW/mm at 94 GHz. Together with a linear gain of 10 dB, the pseudomorphic HEMT technology provides the better RF-power performance compared to the metamorphic power HEMTs and was selected for non-linear modeling and demonstrator design. Three-stage power amplifiers have been fabricated providing a maximum output power of 180 mW at 94 GHz with a linear gain of 11 dB for 3.5 V operation.

Due to the limitation of the gate length to 120 nm for the 3-layer resist gate technology, the metamorphic HEMT technology could not demonstrate its whole potential regarding RF-gain and noise figure. As a consequence of the high yield fabrication, superior power performance at 94 GHz, and similar or even better low-noise properties the industrialization of the 80 nm pseudomorphic HEMT technology started at United Monolithic Semiconductors to provide low noise and power amplifiers for the next generation of W-band applications. However, to target for even higher frequencies, further investigations have to be performed on the metamorphic devices for reduced gate length and improved fabrication yield.

# Contents

| 1 | Introduction 1            |                      |                                                                  |    |  |  |  |

|---|---------------------------|----------------------|------------------------------------------------------------------|----|--|--|--|

|   | 1.1                       | Motiva               | ation                                                            | 3  |  |  |  |

| 2 | Field Effect Transistor 5 |                      |                                                                  |    |  |  |  |

|   | 2.1                       | Idea of              | f the HEMT structure                                             | 5  |  |  |  |

|   |                           | 2.1.1                | Charge control model                                             | 6  |  |  |  |

|   |                           | 2.1.2                | Channel electron transport                                       | 10 |  |  |  |

|   | 2.2                       | DC-ch                | naracteristics and parameters                                    | 15 |  |  |  |

|   | 2.3                       | RF-ch                | aracteristics and parameters                                     | 18 |  |  |  |

|   |                           | 2.3.1                | Small signal model and equivalent circuit                        | 18 |  |  |  |

|   |                           | 2.3.2                | Noise considerations                                             | 22 |  |  |  |

|   |                           | 2.3.3                | Noise model                                                      | 24 |  |  |  |

|   |                           | 2.3.4                | FETs in amplifiers                                               | 27 |  |  |  |

|   | 2.4                       | Recess               | s configuration                                                  | 29 |  |  |  |

|   | 2.5                       | Epitax               | xy structures                                                    | 34 |  |  |  |

|   |                           | 2.5.1                | Pseudomorphic HEMT structures on GaAs substrate                  | 35 |  |  |  |

|   |                           | 2.5.2                | Pseudomorphic HEMT epitaxy                                       | 37 |  |  |  |

|   |                           | 2.5.3                | Metamorphic HEMT-structures on GaAs substrate                    | 38 |  |  |  |

|   |                           | 2.5.4                | Metamorphic epitaxy for low-noise devices                        | 40 |  |  |  |

|   |                           | 2.5.5                | Metamorphic epitaxy for power devices                            | 42 |  |  |  |

| 3 | Devi                      | Device fabrication 4 |                                                                  |    |  |  |  |

|   | 3.1                       |                      | ing control of epitaxy                                           | 47 |  |  |  |

|   | 3.2                       | Device               | e isolation                                                      | 49 |  |  |  |

|   |                           | 3.2.1                | Implantation isolation                                           | 49 |  |  |  |

|   |                           | 3.2.2                | Mesa isolation                                                   | 49 |  |  |  |

|   | 3.3                       | Ohmic                | c contact formation                                              | 51 |  |  |  |

|   |                           | 3.3.1                | Alloyed ohmic contacts                                           | 51 |  |  |  |

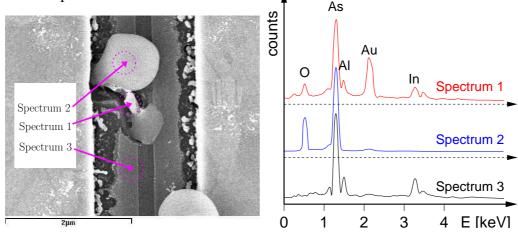

|   |                           | 3.3.2                | Refractory ohmic contact for low-noise metamorphic HEMT          | 58 |  |  |  |

|   | 3.4                       | Gate d               | lefinition                                                       | 62 |  |  |  |

|   |                           | 3.4.1                | Dielectric assisted gate technology                              | 62 |  |  |  |

|   |                           | 3.4.2                | 3-layer resist gate technology                                   | 68 |  |  |  |

|   |                           | 3.4.3                | Gate yield: dielectric assisted versus 3-layer resist technology | 72 |  |  |  |

|   | 3.5                       | Gate r               | ecess                                                            | 73 |  |  |  |

|   |                           | 3.5.1                | Recess on metamorphic wafers                                     | 74 |  |  |  |

|   |                           | 3.5.2                | Recess on pseudomorphic wafers                                   | 79 |  |  |  |

|   | 3.6                       | Gate n               | netallization, lift off and device passivation                   | 80 |  |  |  |

| 4 | Low                       | -noise j             | properties                                                       | 83 |  |  |  |

|   | 4.1                       | Metan                | norphic low-noise HEMT                                           | 83 |  |  |  |

|   |                           | 4.1.1                | DC-performance                                                   | 83 |  |  |  |

|   |                           | 4.1.2                | Small signal RF-performance and model                            | 85 |  |  |  |

|   |             | 4.1.3 RF-noise performance                             | • |   | • |       |   | 88  |

|---|-------------|--------------------------------------------------------|---|---|---|-------|---|-----|

|   |             | 4.1.4 Low frequency noise performance                  | • | • | • | <br>• | • | 91  |

| 5 | Pow         | er properties                                          |   |   |   |       |   | 95  |

|   | 5.1         | Metamorphic power HEMT                                 | • |   | • |       |   | 95  |

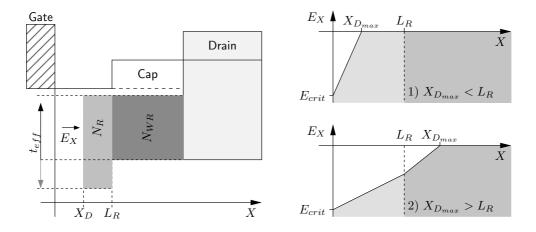

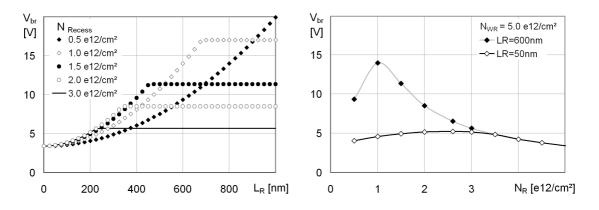

|   |             | 5.1.1 Double recess configuration mHEMT                | • | • | • |       |   | 95  |

|   |             | 5.1.2 Single recess configuration mHEMT                | • | • | • |       | • | 98  |

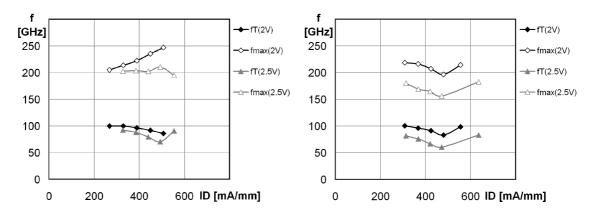

|   |             | 5.1.3 Small signal performance                         |   |   |   |       |   | 101 |

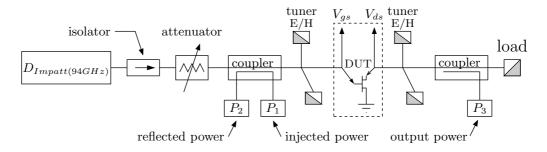

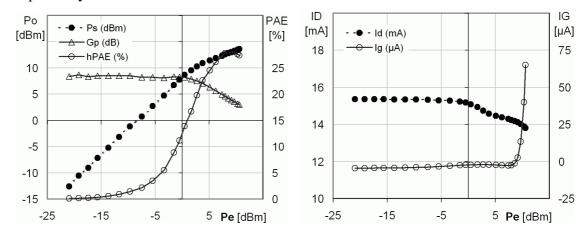

|   |             | 5.1.4 Power performance at 94 GHz                      |   |   |   |       |   |     |

|   | 5.2         | Pseudomorphic power HEMT                               |   |   |   |       |   |     |

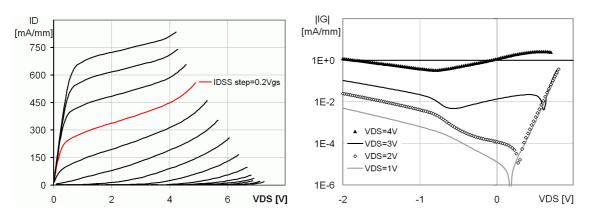

|   |             | 5.2.1 DC-performance                                   |   |   |   |       |   |     |

|   |             | 5.2.2 Small signal performance                         |   |   |   |       |   |     |

|   |             | 5.2.3 Power performance at 94 GHz                      |   |   |   |       |   |     |

|   | 5.3         | Base-cell optimization                                 |   |   |   |       |   |     |

|   |             | 5.3.1 Thermal aspects                                  | • | • | • | <br>• | • | 112 |

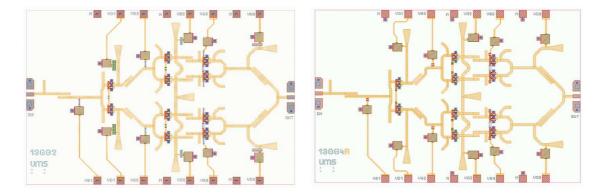

| 6 | W-b         | and demonstration amplifiers                           |   |   |   |       |   | 123 |

|   | 6.1         | Demonstrator fabrication                               | • | • | • |       |   | 123 |

|   | 6.2         | Metamorphic HEMT low noise amplifiers                  | • | • | • |       |   | 124 |

|   |             | 6.2.1 Common source design                             |   |   |   |       |   |     |

|   |             | 6.2.2 Cascode design                                   |   |   |   |       |   |     |

|   |             | 6.2.3 Yield of the metamorphic LNAs                    |   |   |   |       |   |     |

|   | 6.3         | Pseudomorphic HEMT low noise amplifier                 |   |   |   |       |   |     |

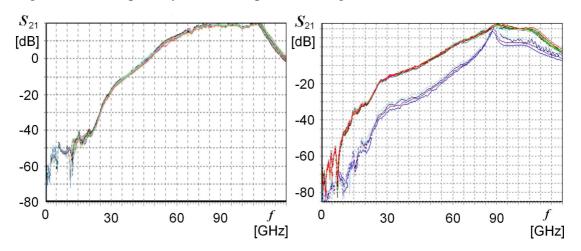

|   | 6.4         | Power amplifiers                                       |   |   |   |       |   |     |

|   |             | 6.4.1 Large signal model                               |   |   |   |       |   |     |

|   |             | 6.4.2 Pseudomorphic power pHEMT amplifiers             | • | • | • | <br>• | • | 131 |

| 7 | Con         | clusion                                                |   |   |   |       |   | 135 |

| A | Epit        | axy                                                    |   |   |   |       |   | 139 |

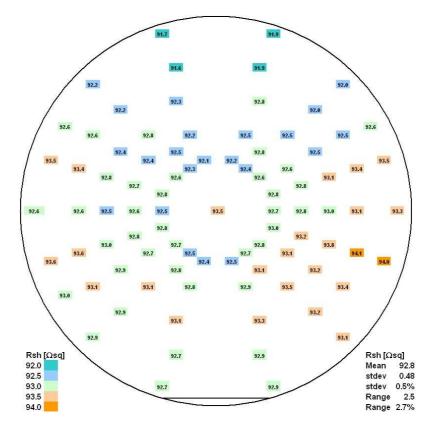

|   |             | Sheet resistance: Metamorphic low-noise epitaxy        |   |   |   |       |   |     |

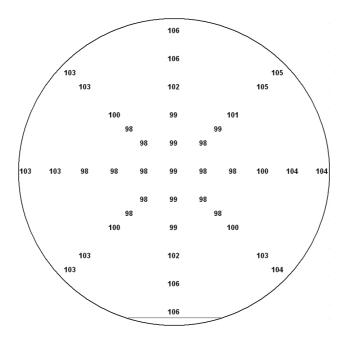

|   |             | Sheet resistance: Metamorphic epitaxy for power        |   |   |   |       |   |     |

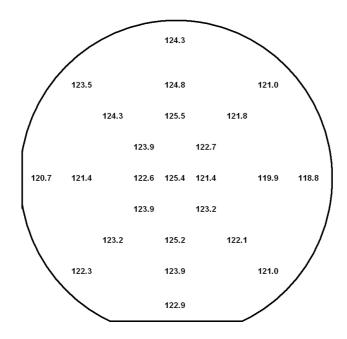

|   | A.3         | Sheet resistance: Pseudomorphic HEMT epitaxy           | • | • | • | <br>• | • | 141 |

| B | Map         | pings & further investigations                         |   |   |   |       |   | 143 |

|   | <b>B</b> .1 | Ohmic contact resistance                               |   |   |   |       |   | 143 |

|   | B.2         | Parameter mappings: low-noise mHEMT                    | • | • | • |       |   | 144 |

|   | <b>B.3</b>  | Parameter mappings: single recess power mHEMT          |   |   |   |       |   |     |

|   | B.4         | Parameter mappings: power pHEMT                        |   |   |   |       |   |     |

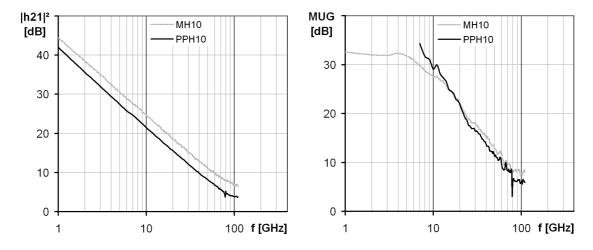

|   | B.5         | S-parameter characterization up to 110 GHz             |   |   |   |       |   |     |

|   |             | B.5.1 Gain of the metamorphic single recess power HEMT |   |   |   |       |   |     |

|   |             | B.5.2 Gain of the pseudomorphic power HEMT             |   |   |   |       |   |     |

|   |             | B.5.3 Gain of different pHEMT base cells               |   |   |   |       |   |     |

|   | B.6         | Passive components                                     |   |   |   |       |   |     |

|   | B.7         | Backside fabrication                                   |   |   |   |       |   |     |

|   | B.8         | Nano-indentation on $In_{53}Ga_{47}As$                 |   |   |   |       |   |     |

|   | B.9         | Two step RIE-free gate technology                      | • | • | • |       |   | 159 |

| С  | Mod      | els & circuit principles             | 161 |  |  |  |  |

|----|----------|--------------------------------------|-----|--|--|--|--|

|    | C.1      | Simplified small signal model        | 161 |  |  |  |  |

|    | C.2      | ADS-model elements: low-noise mHEMT  | 162 |  |  |  |  |

|    | C.3      | Non-linear model: Power pHEMT        | 163 |  |  |  |  |

|    | C.4      | Common source and cascode amplifiers | 164 |  |  |  |  |

| Gl | Glossary |                                      |     |  |  |  |  |

| Ac | know     | ledgment                             | 187 |  |  |  |  |

| Cu | rricu    | lum vitae                            | 189 |  |  |  |  |

## **1** Introduction

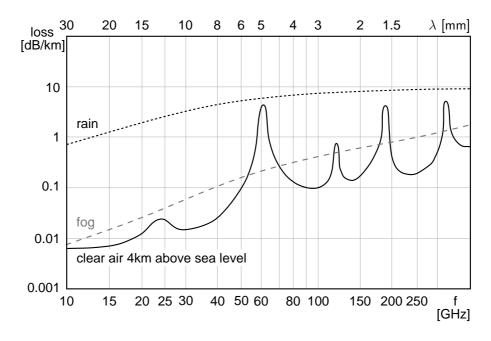

Over decades, the progress in millimeter wave semiconductor technologies has been strongly driven by military requests [1]. However, also an increasing number of wireless civil applications such as telecommunication-, sensor- and navigation-systems require more and more low-noise and power devices at high frequencies up to 100 GHz. Considering the atmospheric attenuation spectrum in figure 1.1, there is higher damping of millimeter waves for increasing frequencies. Absorption peaks at 24 GHz, 180 GHz and 330 GHz are related to the vapor content in air; at 60 GHz and 120 GHz absorption is caused by interaction with O<sub>2</sub> molecules. Atmospheric properties provide windows for long-range transmission (e.g. at 35, 94, 140 and 220 GHz) and narrow highly damped frequency bands that are suited to short-range use (e.g. at 24 GHz or 60 GHz) [2, 3]. The impact of the weather situation on the absorption characteristics can be used for meteorological investigations. At frequencies of low attenuation, below 20 GHz, there are Xand Ku-band satellite communication as well as far reaching radar systems. Generally, the strong impact of climate conditions has to be regarded as a limitation of the bandwidth for data transmission; the range of a radar gets reduced. Rain fade on the other hand can be used for radar assisted weather monitoring. The absorption peaks, especially at 24 GHz are helpful to realize short range radar systems as used for automotive parking assistants or pre crash detection. Higher frequencies allow more band-width for data transmission and increased radar accuracy. At W-band (75 GHz to 110 GHz), there is an atmospheric window of low attenuation allowing multi gigabit short distance communication, radar assisted automotive cruise control (77 GHz) and high resolution millimeter wave radar systems.

Figure 1.1: Attenuation (absorption) spectrum between 10 and 300 GHz (resp. 30 to 1 mm wavelength) in air [1] including attenuation by fog and rain [4].

At the 94 GHz absorption minimum, cloud profiling radars [3] allow the detection of rain from satellites. Active radar imaging is used at airports for traffic control on runways but also to identify debris, a severe danger to the safety and integrity of aircrafts [5]. Since most wall materials are transparent for millimeter waves, active radar imaging systems are suited for observation but also for rescue activities to search for people hidden in concealed rooms of collapsed buildings. Passive radar imaging systems [6] demonstrate non-intrusive people screening at security portals e.g. of an airport. Based on a high millimeter wave absorption of the human skin, concealed weapons that typically strongly reflect can be identified even through several layers of clothing. Such passive systems need no active microwave source - reflected radiation is thermally emitted by the surroundings.

While passive millimeter wave imaging systems only need a high quality low noise amplifier, also a power amplifier is needed for the active version. Low-cost silicon technologies significantly improved high frequency properties during recent years. At high frequency level, however, either market volumes are too small for cost effective mass production or RF-performance such as noise figure and output power do not meet the requirements. These niche markets are addressed by III-V semiconductor technologies based on GaAs, InP and GaN, providing superior low-noise and RF-power performance. Up to 77 GHz, low noise amplifiers are realized by commercial 150 nm gate length pseudomorphic HEMTs (High-Electron-Mobility-Transistor) on GaAs substrate [7]. To address higher frequency levels such as 94 GHz, the active device has to provide more gain. This is the target of this work. Furthermore, the new HEMT technologies (low-noise & power) have to comply with following conditions:

- compatibility to the 4" wafer area production facility

- modular device fabrication for high yield production

- minimum device breakdown of 4 V for the low-noise technology

- minimum device breakdown of 6 V for the power technology

- minimum device breakdown of 3 V for the turned-on power device

HEMT structures on InP substrate have demonstrated excellent RF-performance [8, 9, 10, 11] due to superior transport properties of the InGaAs quantum well. However, the InP-approach has been no option due the non-availability of 4"-wafers at the beginning of this work. Moreover, the high brittleness of the InP substrates is critical for automatic wafer handling which is frequently used in the pHEMT production line.

Alternatively, there is down scaling of the existing HEMT technology to a shorter gate length [12, 13] to improve the RF-gain. This option is highly compatible to existing UMS pHEMT technologies and has been considered in this work.

Metamorphic HEMT structures promise a combination of the benefits of a low bandgap  $In_xGa_{1-x}As$  channel known from InP with less brittle 4" GaAs substrates [14, 15, 16]. Thanks to the metamorphic buffer, the indium concentration x for the channel gives some degree of freedom between 20 and 80 % [17]. This has been used to optimize the metamorphic devices regarding low-noise and power requirements.

#### 1.1 Motivation

### **1.1 Motivation**

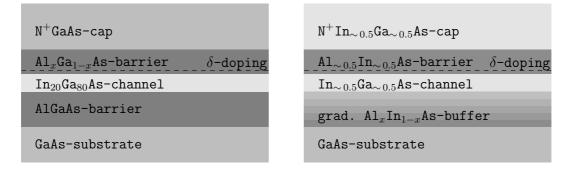

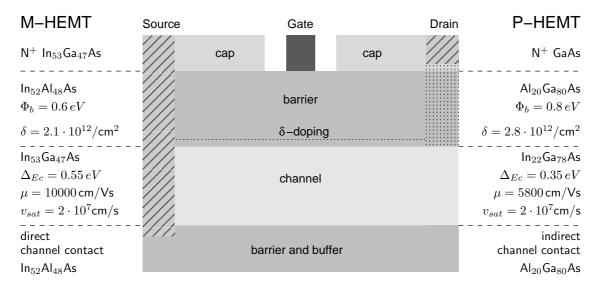

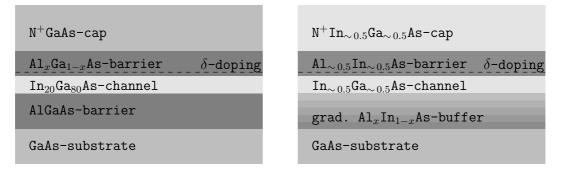

High-Electron-Mobility-Transistors are used in low-noise and power radio frequency applications due to their high electron mobilities and saturation velocities. In this work, band-gap engineering has been performed to optimize metamorphic and pseudomorphic HEMT-structures as roughly sketched in figure 1.2 for low-noise and power operation.

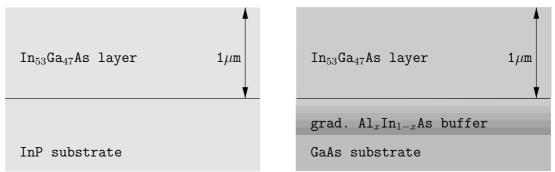

Figure 1.2: Sketch of pseudomorphic (1) and metamorphic (r) HEMT epitaxy structures.

The aim of this work is not to target for world record device performances linked to ultrashort gate length [18] but to develop production worthy pseudomorphic and metamorphic HEMT technologies for W-band low-noise and power applications providing state-onthe-art performance. Metamorphic HEMT technologies based on 100 nm and 70 nm gate length and an indium concentration of 65 and 80 % have demonstrated transit frequencies of 200 and 290 GHz with maximum oscillation frequencies of 280 and 340 GHz, respectively [19, 20, 21]. With this, cascode single stage LNA reached a linear gain of 10.5 dB at 94 GHz with a noise figure around 3 dB. By reduction of the indium content, a higher operation voltage and device breakdown has been realized for metamorphic power devices; a concentration of 43 % is found as a good compromise between output power and RF-gain [16]. For a gate length of 0.15  $\mu$ m, a power density of 320 mW/mm with a power added efficiency of 28 % and a linear power gain of 6 dB have been reported at 95 GHz for a 150  $\mu$ m device [22].

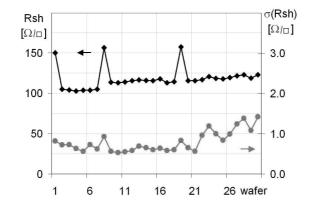

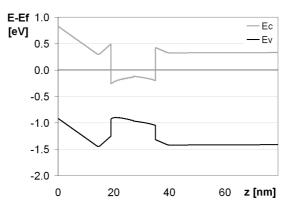

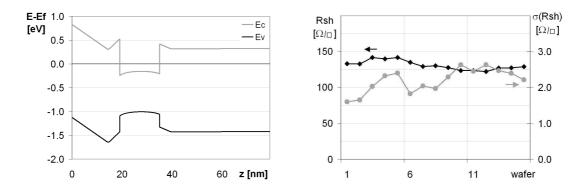

Table 1.1 gives a summary of all types of heterostructures used in this work including a rough rating with respect to the epitaxy quality. Indices indicate the location within the epitaxy sequence such as  $\Delta E_{c_u}$  is linked to the conduction band discontinuity towards the upper barrier and similar for  $\Delta E_{c_l}$  referring to the lower barrier. The growth of the epitaxial material was performed in solid source MBE-tools on semi-isolating GaAs substrates. The diameters of the wafers are 3" for material grown at the Daimler-Research Laboratory and 4" for wafers purchased from a commercial epitaxy supplier.

To target for low-noise applications, a 120 nm metamorphic HEMT technology has been developed in this work based on an indium concentration of 53 to 70 %; the grading allows to increase the conduction band discontinuity  $\Delta E_{c_u}$  towards the barrier compared to a pure lattice matched structure for high charge density and RF-gain. Low-noise properties have been characterized in V- and W-band on device and MMIC level showing state-of-the art performance in chapter 6.

Regarding power applications, a double recess configuration on a metamorphic HEMT with a high indium content up to 60% has been investigated in comparison to a single recess metamorphic HEMT based on 43% channel indium content. Alternatively, a single recess pseudomorphic power HEMT technology with a down scaled gate length of 80 nm has been developed in this work. Power properties of the different technologies are compared at 94 GHz on device level. State-on-the art power amplifiers based on the pseudomorphic HEMT technology are presented in chapter 6.

| application               | low-noise                            |                           | power                                     |                                      |

|---------------------------|--------------------------------------|---------------------------|-------------------------------------------|--------------------------------------|

| type                      | metamorphic single recess            | metamorphic double recess | metamorphic single recess                 | pseudomorphic<br>single recess       |

| supplier                  | 4" commercial                        | 3" Daimler-Research       | 4" commercial                             | 4" commercial                        |

| $E_{g_u}(barrier)$        | 1.49 eV (47%Al)                      | 1.74 eV (60%Al)           | 1.95 eV (65%Al)                           | 1.74 eV (25%Al)                      |

| $\Delta E_{c_u}$          | 0.64 eV                              | 0.75 eV                   | 0.77 eV                                   | 0.42 eV                              |

| $\Delta E_{v_u}$          | 0.28 eV                              | 0.32 eV                   | 0.34 eV                                   | 0.2 eV                               |

| $E_{g_u}(channel)$        | 0.57 eV (70%In)                      | 0.67 eV (60%In)           | 0.85 eV (43%In)                           | 1.11 eV (25%In)                      |

| $\overline{E_g}(channel)$ | 0.66 eV (60%In)                      | 0.76 eV (50%In)           | 0.85 eV (43%In)                           | 1.11 eV (25%In)                      |

| $E_{g_l}(channel)$        | 0.74 eV (53%In)                      | 0.85 eV (43%In)           | 0.85 eV (43%In)                           | 1.11 eV (25%In)                      |

| $\Delta E_{c_l}$          | 0.52 eV                              | 0.63 eV                   | 0.63 eV                                   | 0.42 eV                              |

| $\Delta E_{v_l}$          | 0.23 eV                              | 0.27 eV                   | 0.27 eV                                   | 0.20 eV                              |

| $E_{g_l}(barrier)$        | 1.49 eV (47%Al)                      | 1.74 eV (60%Al)           | 1.75 eV (57%Al)                           | 1.74 eV (25%Al)                      |

| $n_s$                     | $4.1 \cdot 10^{12} \mathrm{cm}^{-2}$ | na                        | $\sim 2.2 \cdot 10^{12} \mathrm{cm}^{-2}$ | $2.2 \cdot 10^{12} \mathrm{cm}^{-2}$ |

| μ                         | $10000  {\rm cm}^2 / {\rm Vs}$       | na                        | $\sim 6000 \mathrm{cm}^2/\mathrm{Vs}$     | $6000\mathrm{cm}^2/\mathrm{Vs}$      |

| R <sub>sh</sub>           | 100-120 Ω <sub>□</sub>               | (101 Ω_)                  | 100-120 Ω <sub>□</sub>                    | 100 Ω□                               |

| homogeneity               | good                                 | poor                      | medium                                    | excellent                            |

| roughness                 | $\sim 2\mathrm{nm}$                  | $\sim 4\mathrm{nm}$       | $\sim 2\mathrm{nm}$                       | smooth                               |

| reproducibility           | $R_{sh}$ -drift                      | na                        | $R_{sh}$ -drift                           | good                                 |

Table 1.1: Properties of the epitaxy-structures used in this work.

# 2 Field Effect Transistor

The principles of unipolar active semiconductor devices, such as field effect transistors (FETs), are known since many years. Although patented first in 1925 by Julius Edgar Lilienfeld [23], research articles and devices were ignored by industry because of difficult control of electronic surface states. Further patents and descriptions of field effect transistors including the description of the first JFET based on pn-junction current control followed until 1945 [24, 25] before the official birth of the (bipolar)-transistor at Bell Labs on  $23^{rd}$  December 1947 [26]. Five years later, first field effect transistors recognized by industry have been realized in 1953 by G.C. Dacey and I.M. Ross [27] gaining remarkable importance in semiconductor technology evolution. Today, digital signal processing found in CPUs and random access memory are dominated by silicon based MOSFET technologies. For analog radio frequency applications, however, compound semiconductor tor devices like High-Electron-Mobility-Transistors on GaAs substrates are found due to their superior microwave low-noise and power performance compared to Si-RFMOS.

### 2.1 Idea of the HEMT structure

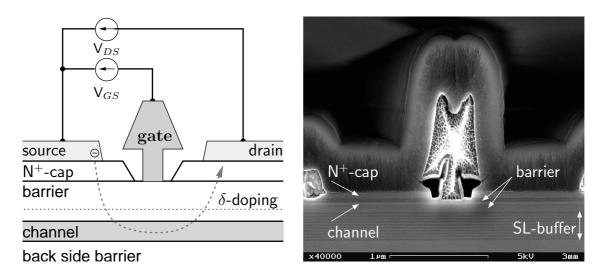

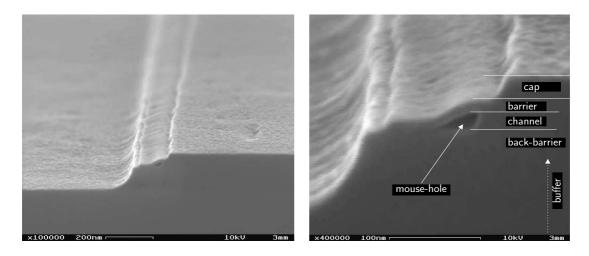

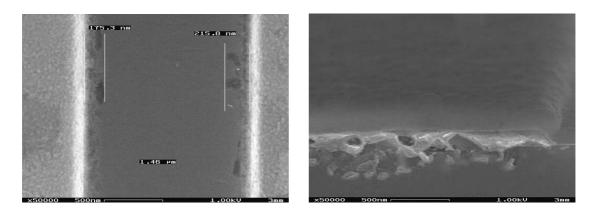

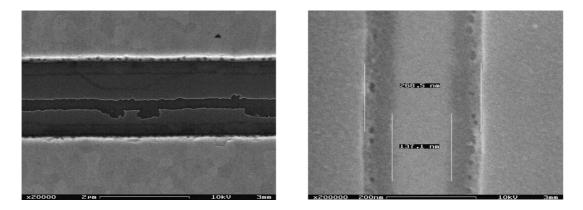

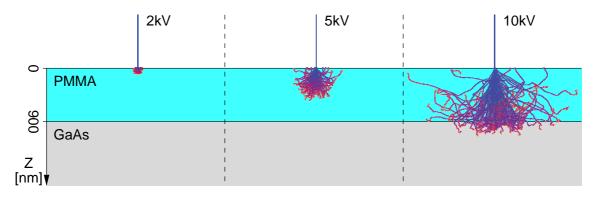

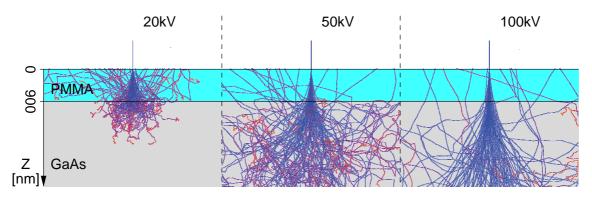

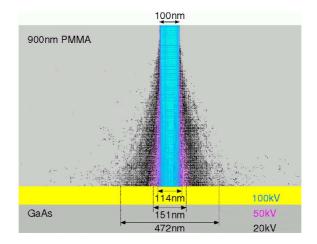

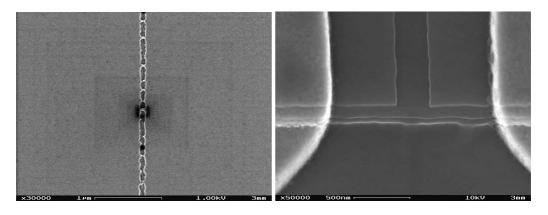

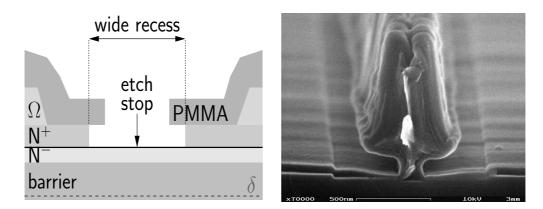

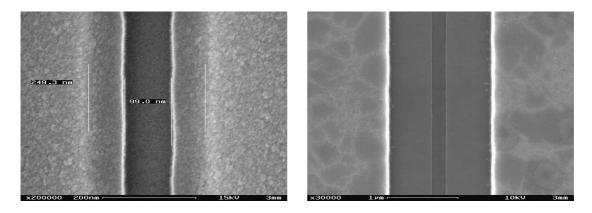

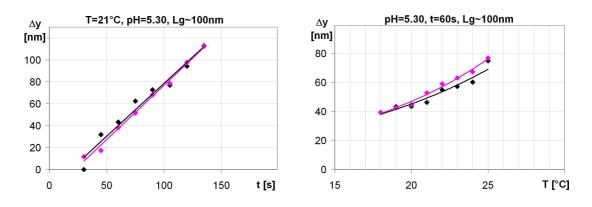

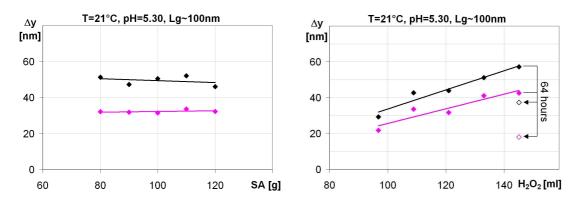

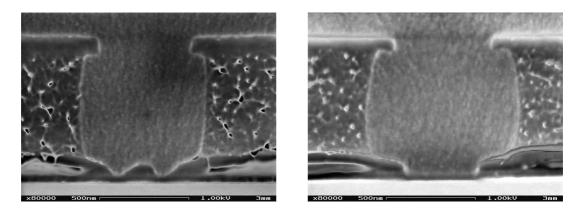

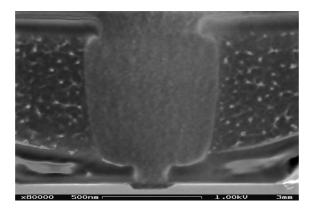

High-Electron-Mobility-Transistors (HEMTs) represent a special type of Field-Effect-Transistors (FETs) deriving its name from a superior mobility of the majority charge carriers. Growth techniques like Molecular Beam Epitaxy (MBE) and Metal Organic Vapor Phase Deposition (MOCVD) allow an industrialized fabrication of semiconductor structures with optimized composition and high crystal quality. The control of semiconductor growth on an atomic scale is mandatory to define reproducible heterojunction structures between two semiconductor materials of different composition and interfaces within limitations like mechanical strain based on different lattice constants. Double heterojunctions are used to form a channel structure where electrons are guided within a two dimensional electron gas (2DEG). A cross section of the HEMT device is shown in 2.1 as a sketch and a SEM-image. For device operation, two voltage sources are required; one for the device supply at the drain contact  $(V_{DS})$  and another one for charge control at the gate  $(V_{GS})$ . The highly doped cap layer is required to realize a good electron transfer from the drain and source contacts to the channel. To form the Schottky contact at the gate, the cap layer is removed by a recess that further has strong impact on device properties like the breakdown behavior discussed later.

#### 2 Field Effect Transistor

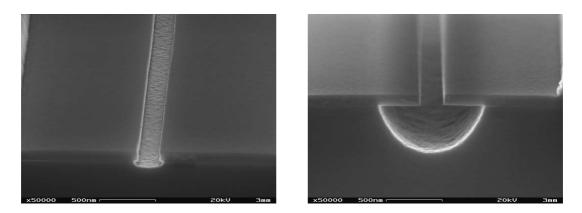

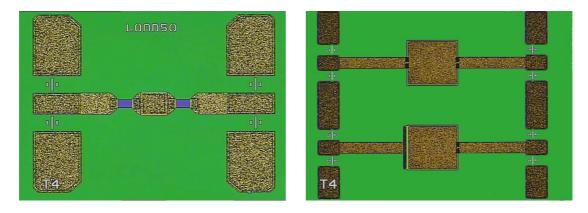

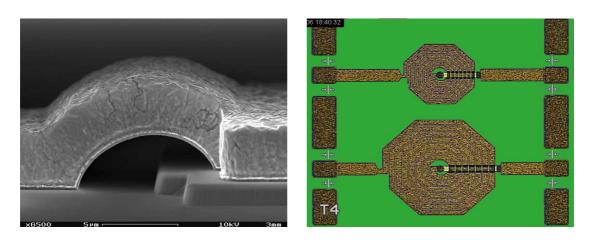

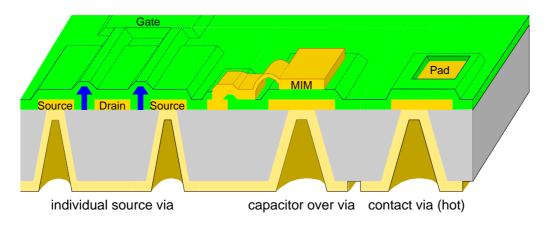

Figure 2.1: Sketch (l) and cross section SEM-image (r) of a HEMT.

The modulation of the charge density is realized by setting the energy level of the discrete states in the channel by  $V_{GS}$  with respect to the Fermi level. Such modulation of the 2DEG in GaAs-AlGaAs heterojunctions has been described first in 1979 by G. Abstreiter and K. Ploog [28] based on gate voltage dependent Raman-spectroscopy. Usually pulse doping outside the channel is preferred for charge supply allowing a separation in space between the activated donators and the 2DEG. This separation mainly helps to reduce Coulomb scattering as a noise source; for similar charge densities, the two dimensional electron gas shows superior electron mobilities compared to bulk electrons [29]. First applications of such field effect transistors were published in 1980 by T. Mimura [30] and D. Delagebeaudeuf [31, 32].

Following, the principles of the HEMT are discussed with respect to the pseudomorphic and metamorphic HEMT approach. A simple linear model is used to derive the charge density in the channel as a function of the gate voltage; non-linearities of the real device are discussed afterwards for low-noise and power application operation.

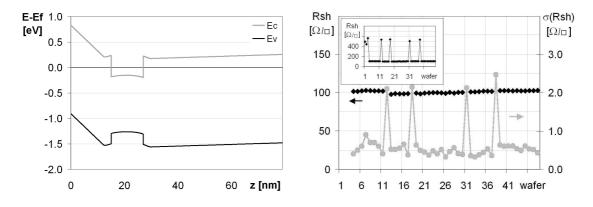

#### 2.1.1 Charge control model

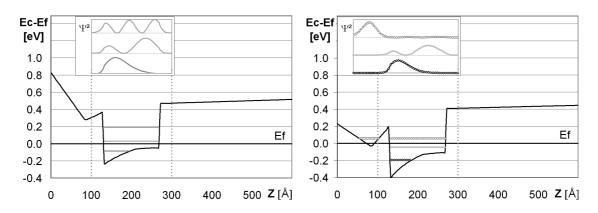

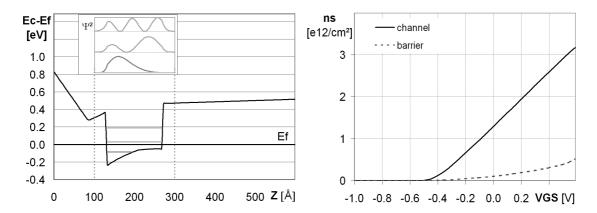

The conduction band of a HEMT structure shown in figure 2.2 was computed with a self consistent Schrödinger-Poisson solver [33] for two gate voltages of  $V_{GS} = 0$  V and  $V_{GS} = +0.6$  V. At zero gate bias, only one discrete electron state of the channel is below the Fermi level and occupied; the electrons are located at the front part of the quantum well, and the distance to the barrier can be roughly described by the barrier thickness. Increasing the gate voltage, more electron states are occupied broadening the 2DEG. For strong enhancement, electrons enter into the barrier forming a parasitic MESFET close to the delta doping profile. Here, the electron mobility is worse compared to the 2DEG in the quantum well related to strong interaction with activated Si-donators. However, the impact on device performance is minor since the parasitic MESFET is not relevant for low-noise biasing at low current level or shows similar saturation velocities compared to channel electrons when operated at high drain voltage for high output power.

Figure 2.2: Simulation of a HEMTs conduction band and discrete channel states (c-band [33]) for zero gate voltage (l) and enhancement mode (r) with  $V_{GS} = +0.6$  V. The inlay shows the probability function of electron location. While only one electron level is below  $E_f$  at zero gate bias, more occupied states are below the Fermi level for enhancement mode operation.

For a simple linearized charge control model, non-linear effects due to the parasitic MES-FET and gradual pinch-off related to substrate doping are neglected. Bending of the conduction band can be described by the electrostatic potential V(z). With the effective electron mass, the eigenenergies  $E_i$  and wave functions  $\Psi_i(z)$  can be calculated from the Schrödinger equation. The electron concentration is given by the squared wave-function. The location of the charge centroid depends on the channel structure and the surface potential controlled by the gate voltage which becomes evident by the inset charts of the squared wave functions in figure 2.2. Since the electro static potential V(z) is only linked to vertical z-direction, the wave-function  $\Psi(x, y, z)$  can be described as follows

$$\Psi(x, y, z) = \zeta(z) \exp(i\theta z) \exp(ik_x x + ik_y y) , \qquad (2.1)$$

with lateral components of the wave vector  $k_x$  and  $k_y$ , the wave vector  $\theta$  and effective mass  $m_z$  in vertical z-direction and the solution  $\zeta_i(z)$  of the one-dimensional Schrödinger equation given in equation 2.2.

$$\left[-\frac{\eta^2}{2m_z}\frac{d^2}{dz^2} - eV(z)\right] \cdot \zeta_i(z) = E_i \cdot \zeta_i(z) \quad \text{with} \quad \zeta_i(z) = 0 \text{ for } z \to \pm \infty$$

(2.2)

Two dimensional movement of the electrons along the quantum well channel can be described by the two-dimensional Schrödinger equation given in equation 2.3 with the effective mass  $m_x$  and  $m_y$  parallel to the interfaces.

$$\left[-\frac{\eta^2}{2m_x}\frac{d^2}{dx^2} - \frac{\eta^2}{2m_y}\frac{d^2}{dy^2}\right] exp(ik_x x + ik_y y) = E_{x,y} exp(ik_x x + ik_y y)$$

(2.3)

With the eigenvalues  $E_i$  from the one-dimensional Schrödinger equation representing discrete sub-bands within the quantum well and free two dimensional electron movement in lateral direction, the energy dispersion of the two dimensional electron gas is given by equation 2.4.

$$E_i(k) = E_i + \frac{\hbar^2 k_x^2}{2m_x} + \frac{\hbar^2 k_y^2}{2m_y}, \qquad i = 0, 1, 2, \dots$$

(2.4)

In order to calculate the electron concentration of the two dimensional electron gas in the quantum well, the product of density of states  $D_{2D}$  given in 2.5 [34] and the Fermidistribution f(E) has to be integrated over the energy by equation 2.6.

$$D_{2D}(E) = \frac{m_{ll}^{\star}}{\pi\hbar^2} \sum_{i} H(E - E_i), \qquad H(x) = \begin{cases} 0 & \text{for } x < 0\\ 1 & \text{for } x \ge 0 \end{cases}$$

(2.5)

$$N_{s} = \int_{E_{L}}^{\infty} f(E) D_{2D}(E) dE$$

(2.6)

In first order, the electron concentration is given by the occupied states located below the Fermi level. This interpretation is valid for very low temperatures close to T = 0 K where the Fermi-distribution is described by a step function; at higher temperature, states above the Fermi energy may get occupied due to the thermal energy of the electrons. A simple capacitor model can be used to describe the charge density of the channel electrons as a function of gate voltage  $V_{GS}$ . In contrast to the MESFET, the distance  $d_b$  between the gate electrode and the channel electrons is constant for HEMT structures in first order and is given by the barrier thickness neglecting the wave function charge centroid. Equation 2.7 describes the linearized relation between charge density and gate voltage with the dielectric constant  $\varepsilon_b$  of the barrier material and the threshold voltage  $V_{th}$ .

$$N_s = \frac{\varepsilon_b}{e \, d_b} (V_{GS} - V_{th}) \tag{2.7}$$

The threshold voltage is defined by the barrier height of the Schottky contact  $\Phi_b$ , the conduction band discontinuity  $\Delta E_c$  between channel and barrier, the pinch-off voltage  $V_p$  required for complete depletion of the barrier, the distance between the gate electrode, the  $\delta$ -doping plane  $d^*$  and the charge concentration of activated donors  $N_b$  within the barrier.

$$V_{th} = \Phi_b - \frac{(\Delta E_c - E_f)}{e} - V_p, \quad \text{with} \quad V_p = \frac{e \, d^*}{\varepsilon_b} N_b \tag{2.8}$$

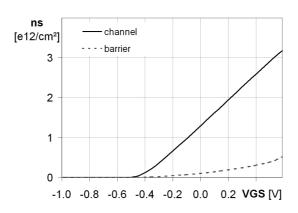

Deviations from the linear charge control approximation may occur due to the parasitic MESFET and a non-ideal gradual device pinch-off; the effective distance between the electron gas and the gate electrode is not constant due to the bias dependent location of the charge centroid. Moreover, influence from real device operation like drain biasing and charge transport in the channel are totally neglected. A more accurate hyperbolic tangent charge control model for the HEMT is discussed by Karmalkar [35]. The onset of the parasitic MESFET is shown in figure 2.3 where the charge density is calculated separately versus  $V_{GS}$  for the electrons in the channel and the barrier. A low-noise device has to be operated at low current levels to suppress effects related to the parasitic MESFET that are: Low RF-gain due to low electron mobilities in the barrier layer and Coulomb scattering with activated donators causing RF-noise.

Figure 2.3: The charge-density is calculated over  $V_{GS}$  for electrons in the channel and the barrier forming a parasitic MESFET (c-band [33]).

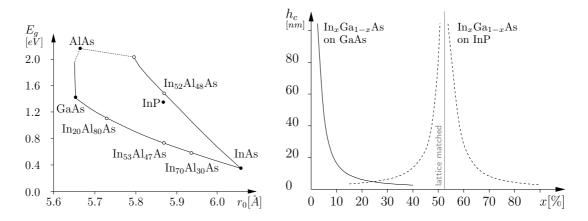

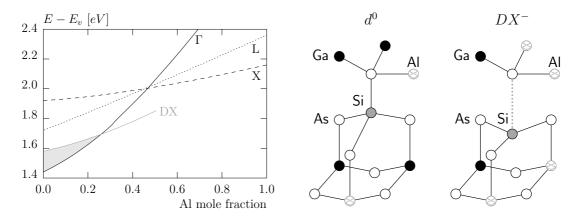

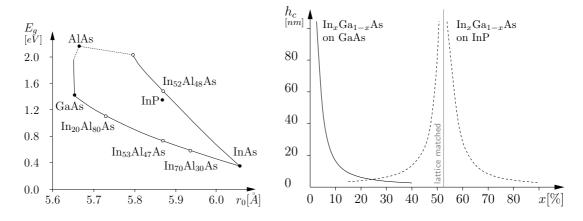

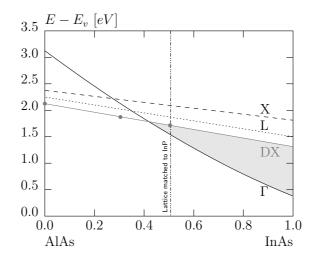

To optimize for a large area of linear charge control, the depth of the quantum well has to be maximized linked to a optimization of the conduction band discontinuity  $\Delta E_c$  at the heterostructures. The conduction band offset is mainly given by the different bandgap of the semiconductors used for the channel and the barrier layers. An overview of the bandgap  $E_g$  for several III-V compounds as a function of the lattice constant  $r_0$  is shown in the left part of figure 2.4.

Figure 2.4: The lattice constant and bandgap of common III-V semiconductors (l) and the critical thickness  $h_c$  of  $\ln_x Ga_{1-x}As$  grown on GaAs- and InP substrates (r) as a function of the indium-content [36].

Due to mechanical constraints not any variation of the barrier and channel can be realized by epitaxy growth. On GaAs substrates,  $Al_xGa_{1-x}As$  can be grown for any mole fraction x due to an almost similar lattice constant; therefore it is well suited to form the barrier layers. Since the barrier also includes the Si-based delta doping profile, the aluminium concentration is limited to 25 % to prevent deep DX-center states that reduce donor activation. To optimize for the conduction band discontinuity,  $In_xGa_{1-x}As$ is used for the channel of the pseudomorphic HEMT having a lower band gap than GaAs. However, there is a tradeoff between the indium concentration, the layer thickness and defect density due to mechanical strain that can be realized by epitaxy growth. Using low temperature **M**olecular **B**eam Epitaxy, the indium content is limited to around 20 % for a 12 nm thick  $Al_{25}Ga_{75}As/In_xGa_{1-x}As/Al_{25}Ga_{0.75}As$  pseudomorphic channel structure grown on GaAs substrate; the conduction band discontinuity is limited to  $\Delta E_c = 0.42 eV$ (c-band simulations [33]). Based on the lattice constant for InP - either by using InP substrates or metamorphic buffer growth on GaAs - a higher conduction band discontinuity can be realized for the  $In_xAl_{1-x}As/In_xGa_{1-x}As/In_xAl_{1-x}As$ -system. With a channel indium concentration of 70 % and 47 % in the barrier, the conduction band discontinuity is 0.64 eV. The metamorphic structures offer better charge confinement of the 2DEG than the pseudomorphic HEMT structure based on GaAs. However, the one dimensional view of the linear charge control model neglects all lateral impact coming from drain biasing for real device operation.

#### 2.1.2 Channel electron transport

The electron movement in the channel from source to drain is driven by electric fields linked to the drain voltage  $V_{DS}$ . The drain current can be calculated from the charge density  $n_s(x)$  at the position x of the channel, the electron velocity v(x) and the gate width of the device W.

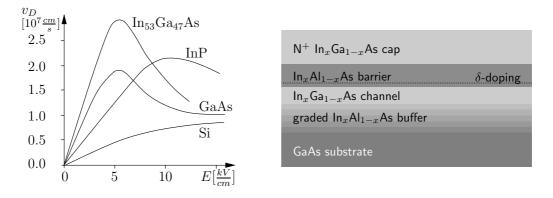

$$I_D = e W n_s(x) v(x) \tag{2.9}$$

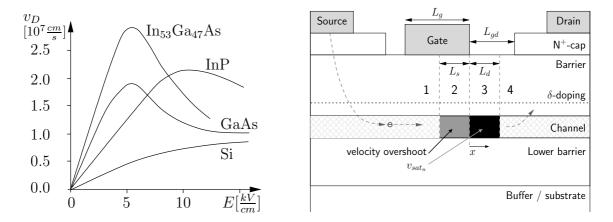

The electron velocity v(x) itself can be described by the product of the low electric field electron mobility  $\mu_n$  and the electrical field  $E_x(x)$  along the channel. The field dependence of the electron velocity over the electrical field is shown in the left part of figure 2.5 for several semiconductor materials. For the III-V-compound semiconductors there is velocity overshoot. While In<sub>53</sub>Ga<sub>47</sub>As shows a more pronounced velocity overshoot compared to GaAs the saturated drift velocity at high fields is almost equal. Velocity overshoot is linked to the retarded transfer of central valley electrons to the higher mass satellite valleys of the conduction band; electrons of the central valley are accelerated by electrical fields exceeding the saturated velocity until they have enough energy to scatter into the satellite valley of significantly higher mass and therefore lower velocity. The analytical approximation for the drift diffusion model (DD) of the carrier mobility in equation 2.10, does not consider velocity overshoot since carrier temperatures are assumed to be constant.

$$\mu_n(E) = \frac{\mu_n}{\sqrt{1 + \left(\frac{\mu_n E}{v_{sat_n}}\right)^2}}; \quad \text{with the low field mobility } \mu_n. \quad (2.10)$$

A hydrodynamic (HD) model has been developed by Hänsch [37] given in equation 2.11 with the fitting factor  $\beta$  depending on the semiconductor material.  $T_n$  and  $T_L$  denote for the electron and lattice temperature with the carrier energy relaxation time  $\tau_{wn}$ .

$$\mu_n(T_n) = \frac{\mu_n}{\left(1 + \alpha_n (T_n - T_L)^{\frac{1}{\beta}}\right)^{\beta}} \quad \text{with} \quad \alpha_n = \left(\frac{3k_B \,\mu_n}{2e\tau_{wn} \,v_{sat_n}^2}\right)^{\frac{1}{\beta}} \tag{2.11}$$

In this approach an additional parameter  $\beta$  was introduced based on HEMT simulations [38] to match with static overshoot obtained by Monte Carlo simulations in the channel. The field dependent electron mobility reads as:

$$\mu_n(|E|) = \frac{2^{\beta} \mu_n}{\left(1 + \sqrt{1 + \left(\frac{2\mu_n |E|}{v_{sat_n}}\right)^{\frac{2}{\beta}}}\right)^{\beta}}$$

(2.12)

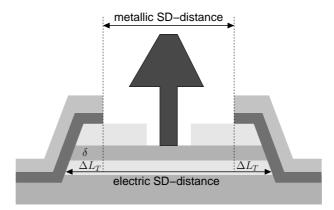

To illustrate the electron transport for a real HEMT a cross sectional schematic diagram of the device is shown in the right part of figure 2.5. Below the gate, electrical fields are low at the source-side (area 1), and electron velocity is below the saturation level. From  $x = L_s$  towards the drain (area 2), velocity saturation is reached. However, there is velocity overshoot, and the mean electron velocity exceeds the saturation velocity. The expansion of the drift zone  $x = L_d$  between the gate and the drain side of the recessed cap at  $x = L_{gs}$ (area 3) strongly depends on the applied drain voltage and the influence of surface states; electrons move with saturated velocity. Outside the drift region towards the drain (area 4) the electron velocity is again below saturation due to low electrical fields.

Figure 2.5: Drift velocities of electrons (I) depending on the electrical field E for several semiconductor materials. Cross sectional schematic diagram of the HEMT (r) showing the areas of different electron velocity. At the source side of the gate (1) and the end of the drift zone (4) electrical fields are low linked to a slow electron velocity. In the high electric field drift zone, velocity overshoot may occur in area (2) described by the hydrodynamic transport model, while velocity saturation is found in area (3). Velocity overshoot is important for low-noise operation; a high saturation velocity is required for power devices.

An iterative solution for the drain current  $I_D$  as a function of biasing at  $V_{GS}$  and  $V_{DS}$  is given in [39] based on the drift diffusion model by the calculation of the saturation zone  $L_s$  underneath the gate and the drift zone  $L_d$ . However, the basic dependencies between the electron transport in the channel and device RF-properties can be discussed in a simple way. To improve the RF-gain of the device, one has to optimize for a short electron transfer time  $\tau$  from source to drain. The electron transfer time of the intrinsic device can be summarized from the transfer time of regions 1 to 3 with the mean velocities  $V_i$  and saturation drift velocity  $v_{sat_n}$ .

$$\tau = \frac{L_g - L_s}{v_1} + \frac{L_s}{v_2} + \frac{L_d}{v_{sat_n}}$$

(2.13)

To optimize the transfer time, the gate length  $L_g$  can be reduced also supporting the impact of velocity overshoot in region 2 [40]. Furthermore, the expansion of the drift zone can be minimized by low drain voltage operation. However, this is only an option for low-noise devices that do not have to provide much output power.

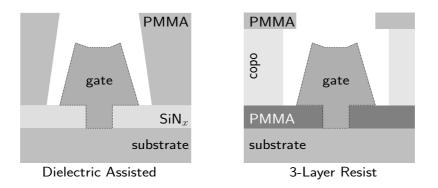

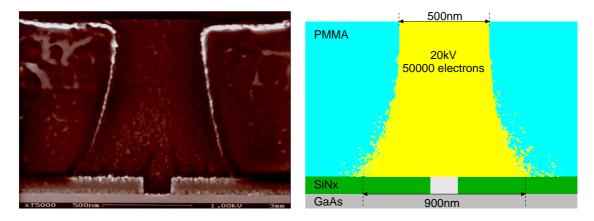

To assess the different transport properties for metamorphic and pseudomorphic HEMT structures, simulations of generic device structures have been performed with the commercial tool ATLAS (Silvaco) 2.6. For the device model, the structure of the HEMT is split into segments of different material and physical parameters. For each semiconductor segment Poisson's equation and the continuity equation have to be solved numerically for each carrier type to calculate the electric field and charge density; thermionic-field emission and tunneling has to be taken into account at heterojunction interfaces while surface states, especially at the gate recess, form a built-in electrical field perpendicular to the semiconductor surface. Models and most materials parameters are provided by the simulators library. Detailed investigations on numerical device simulations of HEMT structures have been performed by Brech [38].

Figure 2.6: Generic metamorphic and pseudomorphic HEMT structure including physical parameters required for device simulation. Geometry aspects like the gate length, gate recess and barrier thickness are similar for both structures; merely the ohmic contact is realized differently with direct contacting of the metamorphic channel.

The generic device structure used for simulation is shown in figure 2.6; the left part of the picture represents the metamorphic, the right part the pseudomorphic structure. For comparison, similar geometry parameters like the barrier thickness (18 nm), recess size (270 nm) and gate length (70 nm) have been chosen for both technologies. Unstrained  $In_{0.53}Ga_{0.47}As/In_{0.52}Al_{0.48}As$  layers are used for the channel of the metamorphic structure

showing a higher conduction band discontinuity  $\Delta_{Ec}$  and low field electron mobility  $\mu$  compared to the pseudomorphic device structure. Referring to figure 2.5, the saturation velocity  $v_{sat}$  at high electrical field as found in the drift zone of the device is almost equal for both channel materials. However, there is velocity overshoot in the channel area underneath the gate foot before electrons are retarded to their high field saturation velocity. Velocity overshoot described by the hydrodynamic transport model is more pronounced for higher indium concentration and electrons of the metamorphic device can achieve a higher overshoot velocity and therefore a higher mean velocity for charge transfer. Physical parameters of the materials have been taken from the library of the simulation tool without modification. Merely the doping levels and the height of the Schottky barrier have been adjusted to reach typical values for device pinch-off obtained in previous work [15, 41].

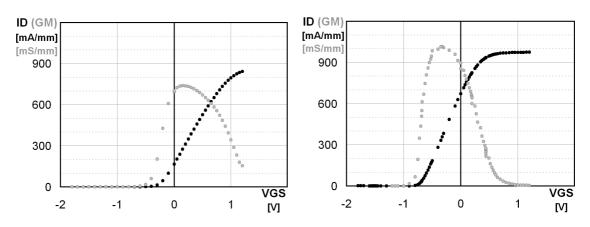

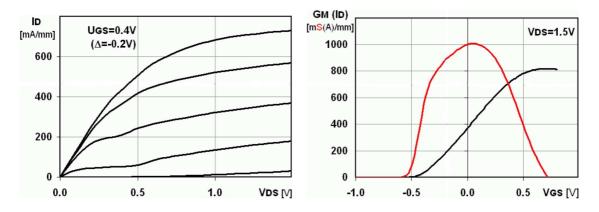

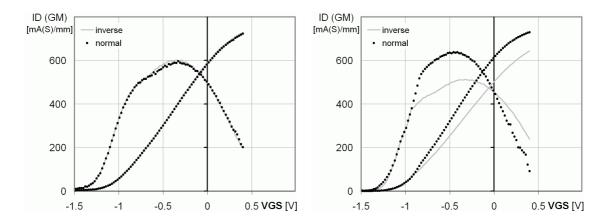

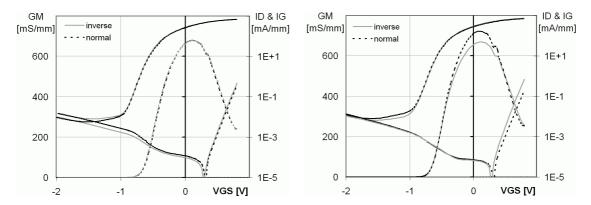

Device simulations shall only provide a qualitative view on the DC-transport properties of the metamorphic and pseudomorphic HEMT structures and will deviate from results obtained by experiment. The transfer characteristics have been simulated for a constant drain voltage of  $V_{DS} = 1.5$  V for both HEMT structures as shown in figure 2.7. Due to the higher conduction band discontinuity for the metamorphic device, more carriers are confined in the channel and a higher current density combined with a more negative pinchoff are observed. Since surface states located near the gate recess have been neglected in the simulation, the maximum saturation currents exceed typical measured results presented later by around 20 % on both structures. The peak transconductance  $G_{max}$  of more than 1000 mS/mm is significantly higher for the metamorphic structure compared to 740 mS/mm for the pseudomorphic structure.

Figure 2.7: Simulated transfer characteristic of the pseudomorphic (l) and metamorphic (r) HEMT structure at  $V_{DS} = 1.5$  V.

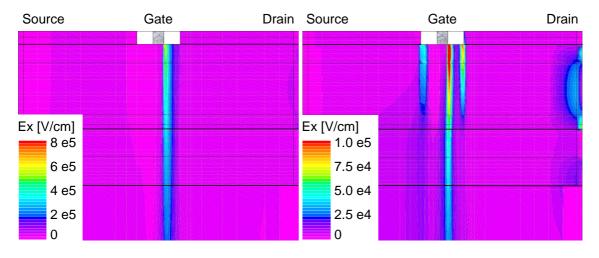

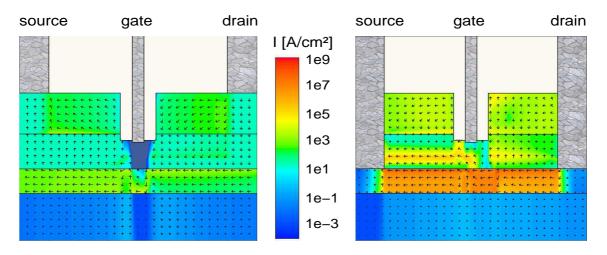

Besides the calculation of the IV-characteristics, the distribution of the electrical field been simulated for open channel operation at  $V_{GS} = 0.4$  V and  $V_{DS} = 1.5$  V and device pinch-off at  $V_{GS} = -1.2$  V and  $V_{DS} = 2.5$  V. Results are presented in figure 2.8 for the metamorphic structure. The pinched off device shows a maximum electric field of around 600 kV/cm at the drain-side of the gate foot. For the open channel operation condition at  $V_{GS} = 0.4$  V, the maximum electric field is still observed at the drain-side of the gate foot but lowered to around 100 kV/cm. This is due to the reduced drain to gate voltage  $V_{GD}$  and the appearance of a second high field domain at the drain-end of the gate recess but also real space transfer of hot electrons into the barrier and buffer layers [42]. Simulations of the pHEMT

structure showed no remarkable qualitative difference for the electric field distribution.

Figure 2.8: Simulated electrical field distribution of the metamorphic HEMT structure for pinchoff (l) and open channel condition (r) at  $V_{DS} = 2.5$  V and 1.5 V, respectively.

Due to the assumption of ideal boundary conditions in this model there are too large errors for a quantitative evaluation of the HEMT structures. For a more accurate model, the surface states in the gate recess area which affect the electric field distribution have to be considered carefully, and several simulation iterations are required to obtain good agreement with experimental data. Usually, the model parameters have to be adjusted by fitting factors to find a compromise for the DC- and RF-behavior. Fitting of material parameters has to agree with literature data that frequently show large variations.

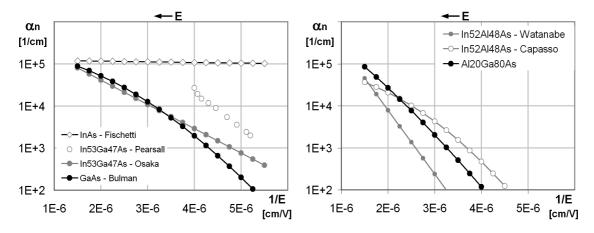

Figure 2.9: Impact ionization coefficient  $\alpha_n$  for electrons in typical channel (1) [43, 44, 45, 46] and barrier (r) material [47, 48, 49, 50].

For instance in figure 2.9, there is a is a big difference for the ionization coefficient  $\alpha_n$  for the metamorphic channel material In<sub>53</sub>Ga<sub>47</sub>As depending on the literature source [43, 44]. Compared to GaAs, Osaka observed slightly higher impact ionization rates for In<sub>53</sub>Ga<sub>47</sub>As only at low electrical fields. Much more pronounced impact ionization between that of GaAs and InAs has been reported by Pearsall [44]. However, the lower  $\alpha$ -values given by Osaka are considered as the correct ones due to good agreement to

noise simulations [43] and are implemented in the library of ATLAS. Similar uncertainties are found for the  $In_{52}Al_{48}As$  barrier material. Therefore, it is difficult to simulate the device breakdown precisely as desired to optimize the channel of the device regarding impact ionization. In sub-channel architectures for instance [51], hot-electrons may transfer from the low band gap high mobility channel into the sub-channel of higher band gap before impact ionization is observed.

#### **2.2 DC-characteristics and parameters**

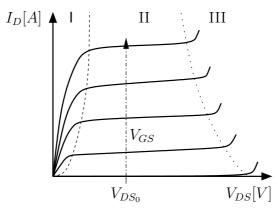

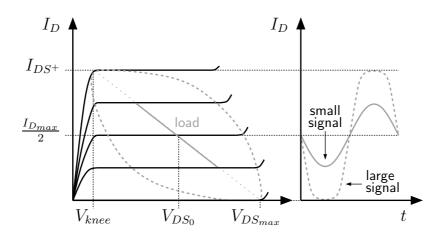

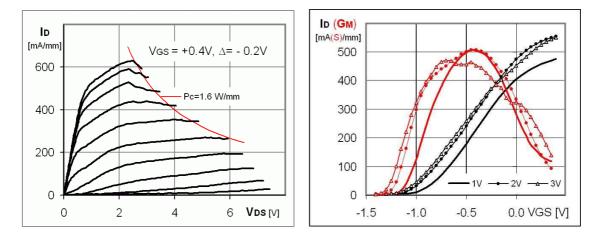

The output characteristics shown in figure 2.10 can be separated into three areas. In the access region (I) at low  $V_{DS}$ , the electron velocity is below saturation and the device works as an voltage controlled resistor; this area is of less interest for a transistor working as an amplifier but becomes more important if the device is used as a mixer. In the second area (II), the device represents a voltage controlled current source with the saturation current  $I_D(V_{GS})$ ; the expansion of the drift zone at the drain side of the gate strongly depends on the drain voltage  $V_{DS}$ . Device breakdown occurs in the third area (III) due to several mechanisms discussed later.

Figure 2.10: Schematic output characteristics of a HEMT with the access (I), saturation (II) and breakdown area (III).

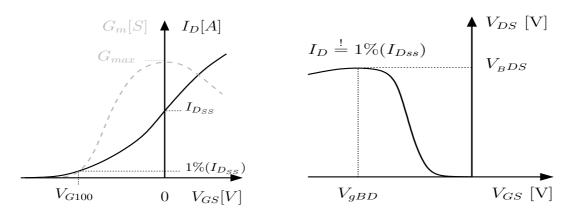

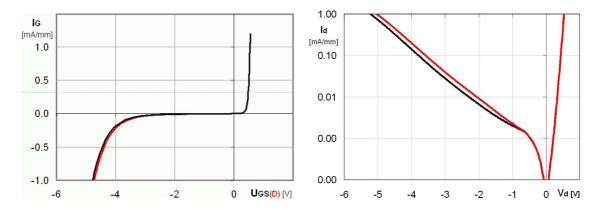

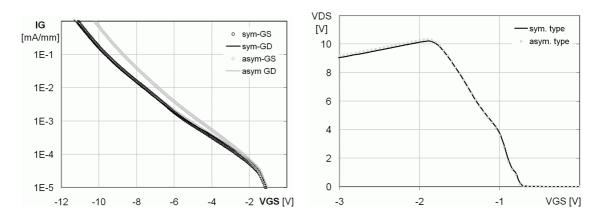

There are several key DC-parameters to describe the properties of the device as shown in figure 2.11. For a constant drain voltage  $V_{DS}$ , a gate voltage sweep is performed from deep pinch-off to open channel to obtain the transfer characteristic of the device. The maximum saturation current  $I_{DS^+}$  is determined at a gate voltage adequate to the Schottky barrier height which is 0.7 V for the pseudomorphic and 0.5 V for the metamorphic HEMT. The definition of the saturation current  $I_{DSS}$  at  $V_{GS} = 0$  V originates from JFET technologies and represents the drain current at the transition from depletion to enhancement mode device operation;  $I_{DSS}$  is close to zero for enhancement mode devices. For depletion mode devices considered in this work, the device pinch-off voltage  $V_{G100}$  is defined at a drain current of 1% of  $I_{DSS}$ . The transconductance  $G_m$  is derived from the transfer characteristic with the peak transconductance  $G_{max}$ . Diode breakdown voltages  $V_{GD}$  and  $V_{GS}$  are obtained from two port measurements for a reverse current of 1 mA/mm. The device breakdown voltage  $V_{bDS}$  is extracted from a gate voltage sweep for a constant drain current of 1% of  $I_{DSS}$  as shown in the right part of figure 2.11. The off-state breakdown  $V_{bDS}$  does not have to be related to avalanche breakdown in the channel but might be linked to thermionic field emission or tunneling.

2 Field Effect Transistor

Figure 2.11: Transfer characteristic (l) from a  $V_{GS}$  sweep at constant drain voltage  $V_{DS}$  including key DC-parameters. The three terminal device breakdown (l)  $V_{bDS}$  is obtained from a  $V_{GS}$ -sweep for a leakage current of 1 % of the saturation current  $I_{DSS}$ .

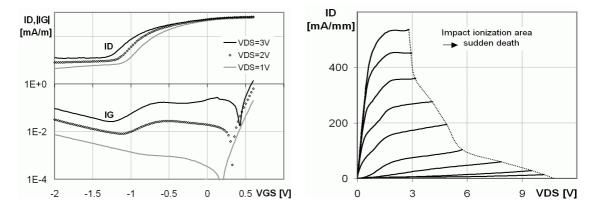

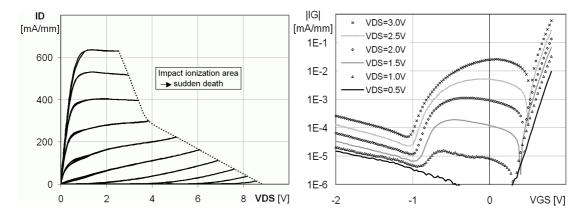

In contrast to the off-state breakdown  $V_{bDS}$ , the evaluation of the on-state breakdown behavior at open channel is more difficult because the open channel represents the counter electrode including lateral current flow. Device operation in this area is very sensitive to oscillations - there is no on-state breakdown parameter that can be systematically assessed by automatic measurement tools. Device breakdown may occur due to:

- Gate breakdown: there are leakage currents over the gate barrier due to thermionic field emission and tunneling mechanisms [52]. The device may work properly, however, these currents can degrade the gate metal by electro migration forming local interruptions of the Schottky contact. Due to locally increased current densities, hot spots are formed that may locally destroy the device by thermal run away. Furthermore, gate breakdown can be linked to avalanche breakdown due to high electric fields in the barrier layer.

- Avalanche breakdown: critical electrical fields can be reached in the active layers causing impact ionization and avalanche current multiplication. The device fails by instantaneous burn-out.

- Substrate breakdown & leakage: Critical electrical fields may occur in the substrate between source and drain but also between the drain areas and the grounded back-side metalization of the device. Furthermore, there are leakage pathes supported by impact ionization in the channel; holes injected and accumulated in the buffer lower the energy level of the conduction band and work against device pinch-off.

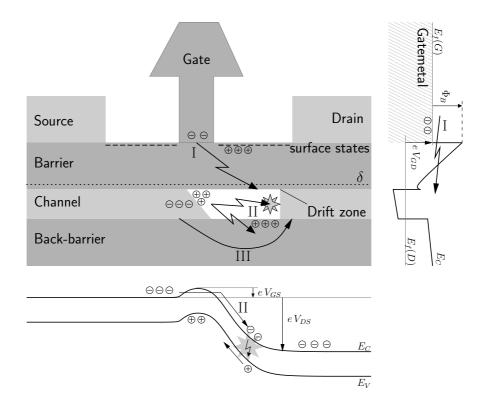

The breakdown mechanisms of the HEMT are sketched in figure 2.12. In contrast to an ideal Schottky diode, the depletion zone of the gate diode is also expanded laterally causing two barriers in series with a poor ideality factor around 1.4. At high drain voltage or electric field, the conduction band is strongly bent between the Schottky contact and the end of the drift zone at the drain side of the channel. Electrons may overcome the barrier I) by thermionic field emission and tunneling [52] and may contribute to impact ionization due to the high electric field in x-direction. The gate breakdown voltage is usually determined by two-terminal measurements for a fixed reverse leakage current (typically 1 mA/mm).

Figure 2.12: Breakdown mechanisms in a HEMT: I) gate breakdown, II) channel breakdown and hot-electron transfer into the buffer and III) substrate leakage. Holes from impact ionization are accumulated at the recess surface and the valence band maximum below the gate. Band diagrams for electron injection across the Schottky barrier and along the channel are sketched right and below the cross section of the device.

The off-state breakdown  $V_{bDS}$  is determined from three-terminal measurements where the channel is pinched off down to a fixed drain leakage current. Gate breakdown but also channel breakdown contribute to drain leakage, where source-side electrons are injected into the high field drift zone by overcoming the channel barrier II) towards the drain; this hot electron effect is more pronounced for a short gate length. Holes created by impact ionization accumulate in the valence band maximum [53, 54] right below the gate and may recombine radiative by electroluminescence [55, 56]. However, holes get also injected into layers outside the channel and act as a fixed positive charge, lowering the energy barrier at the source/channel junction and enhancing the electron injection into the high field area of the channel - in the substrate, this phenomenon is often referred as the parasitic bipolar effect [57, 58, 59] (PBE). The parasitic bipolar effect can be successfully suppressed by a p-type doped substrate body contact placed below the back barrier [60]. Depending on the value for the leakage currents, different temperature dependencies might be observed for the off-state breakdown [61] allowing a rough identification of the dominating breakdown mechanism. Compared to MESFETs, HEMTs can achieve a higher off-state breakdown voltage for similar maximum drain current density; this is related to the lateral extension of the drift zone and surface states located at the gate recess which cause surface depletion discussed later in the recess section. At open channel, the on-state breakdown is dominated by hot channel electrons and impact ionization.

### 2.3 **RF-characteristics and parameters**

RF-properties of the devices are usually characterized by small signal, RF-noise and power measurements. Based on data from several bias conditions and device geometries, lumped element models are extracted to describe the transistors characteristics and are used for circuit design and simulation. Depending on the application, these models may differ from each other; e.g. the noise elements are neglected for the non-linear model of a power device, while power considerations are not required, if the focus is set on low-noise.

#### 2.3.1 Small signal model and equivalent circuit

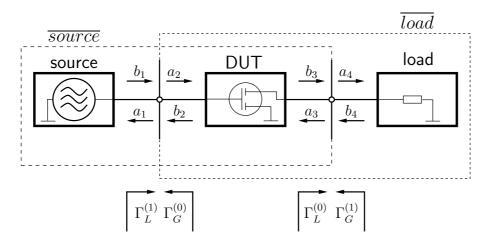

In the range of high radio frequencies, voltages and currents cannot be measured directly anymore. Scattering matrices are used to describe the small signal properties based on normalized waves at the device ports i and j. The complex elements  $s_{ij}$  of the scattering matrix  $\dot{S}$  reflect the linear connection between the entering  $a_i$  and emitted  $b_i$  waves as given in equation 2.14 for a two port device like the HEMT.

$$b_1 = s_{11} a_1 + s_{12} a_2$$

$$b_2 = s_{21} a_1 + s_{22} a_2$$

(2.14)

During small signal characterizations, the device under test (DUT) is placed between a linear RF-source and a passive load as shown in figure 2.13. At the connections of the building blocks, reference planes are defined where e.g. the emitted wave  $b_1$  of the source is equal to the entering wave  $a_i$  at the input of the device. The ratio of the returning  $b_i$  and entering wave  $a_i$  defines the complex reflection coefficient  $\Gamma_k^{(j)}$  indexed with the view-point k with G from the generator and L from the load. The upper index indicates for combinations of building blocks; e.g.  $\Gamma_G^1$  is the reflection coefficient of the combined source consisting of the source and the device under test. Matching is realized at the reference planes, for a conjugate complex relation between the both reflection coefficients. In the case of input matching  $\Gamma_L^{(1)} = \Gamma_G^{(0)*}$  the total available power of the emitted wave  $b_1$  enters into the test device without any returning power ( $b_2 = 0$ ).

Figure 2.13: Small signal scattering parameter characterization.

A descriptive interpretation of the scattering matrix elements in the case of a two-port device like the HEMT is given as follows:

$$S_{11} = \frac{b_1}{a_1}\Big|_{a_2=0}$$

Input reflection coefficient for matched output (2.15)

$$S_{22} = \frac{b_2}{a_2}\Big|_{a_1=0}$$

Output reflection coefficient for matched input (2.16)

$$S_{21} = \frac{b_2}{a_1}\Big|_{a_2=0}$$

Transmission coefficient for matched output (2.17)

$$S_{12} = \frac{b_1}{a_2}\Big|_{a_1=0}$$

Transmission coefficient for matched input (2.18)

Comparing the output power of the combined source including the test device with the power of the wave generator alone is the definition of the available power gain  $G_A$  with the output conjugately matched in equation 2.19.

$$G_A = \frac{|s_{21}|^2 \left(1 - |\Gamma_G|^2\right)}{|1 - s_{11}\Gamma_G|^2 - |s_{22} \left(1 - s_{11}\Gamma_G\right)|^2}$$

(2.19)

Internal feedback may cause device oscillation that generates RF-output power from the DC-supply without external stimulation; the denominator in equation 2.19 is zero leading to infinity gain. Thus, for device stability following conditions have to be fulfilled:

$$|s_{22}| < 1$$

(2.20)

$$|s_{12}| |s_{21}| < 1 - |s_{22}|^2$$

$$|s_{11}| < 1$$

(2.21)

(2.21)

(2.22)

$$\begin{aligned} |s_{11}| &< 1 \\ |s_{21}| |s_{12}| &< 1 - |s_{11}|^2 \end{aligned}$$

(2.22)

(2.23)

$$k > 1$$

(2.24)

For normal active two-ports based on transistor devices, most stability conditions are fulfilled automatically and can be reduced to the stability factor k defined by Rollet [62] in equation 2.25.

$$k = \frac{1 - |s_{11}|^2 - |s_{22}|^2 + |det(\overset{\leftrightarrow}{S})|^2}{2|s_{12}||s_{21}|}$$

(2.25)

With the stability factor k, the maximum available gain (MAG) can be expressed as follows.

$$MAG = \frac{|s_{21}|}{|s_{12}|} \left(k - \sqrt{k^2 - 1}\right).$$

(2.26)

The maximum stable gain (MSG) represents the maximum gain that can be obtained from the originally instable device using external stabilization circuits.

$$MSG = \frac{|s_{21}|}{|s_{12}|} < MAG$$

(2.27)

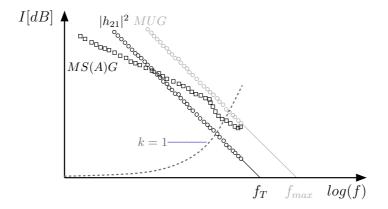

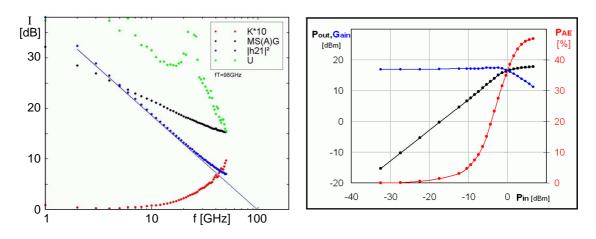

From small signal measurements, important key parameters like the maximum oscillation frequency  $f_{max}$  and the transit frequency  $f_T$  can be extracted from the frequency dependence of the unilateral power gain MUG and current gain  $|h_{21}|^2$  given in equations 2.28 and 2.29.

$$MUG = \frac{|s_{21}/s_{12} - 1|^2}{2k |s_{21}/s_{12}| - \Re(s_{21}/s_{12})}, \qquad MUG(f_{max}) = 1$$

(2.28)

$$h_{21} = \frac{-2s_{21}}{1 - s_{11} + s_{22} - s_{11}s_{22} + s_{12}s_{21}}, \qquad |h_{21}|^2(f_T) = 1$$

(2.29)

At the maximum oscillation frequency  $f_{max}$  the unilateral power gain is 1 or 0 dB. Similar for the current gain  $|h_{21}|^2$  for the transit frequency  $f_T$  representing the electron transition below the gate of the device. The frequency dependencies of the different gain types are shown in figure 2.14 for an exemplary transistor.

Figure 2.14: Extrapolation of the transit  $f_T$  and maximum oscillation frequency  $f_{max}$ .

For very high frequencies the maximum oscillation frequency and transit frequency cannot be determined from the measurement directly due to frequency limitations of the vector analyzer setup; values are extrapolated assuming a first order low pass behavior with a slope of 20 dB/decade. For a stability factor k below 1 the slope of the maximum stable gain MSG is 10 dB/decade. The maximum available gain (k > 1) shows a significantly larger drop over the frequency approaching the unilateral power gain.

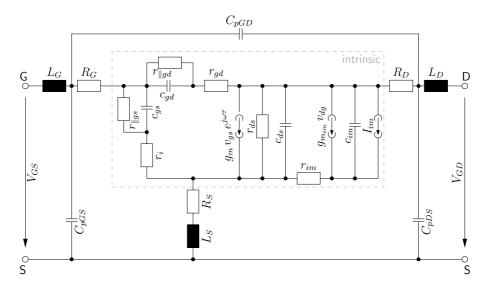

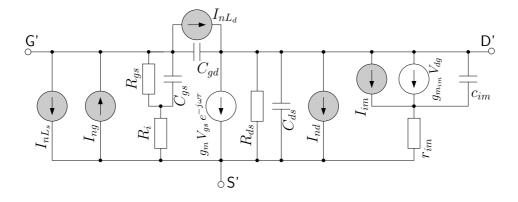

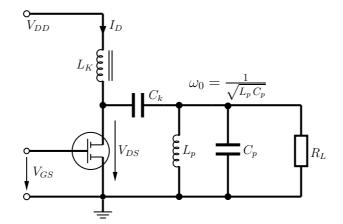

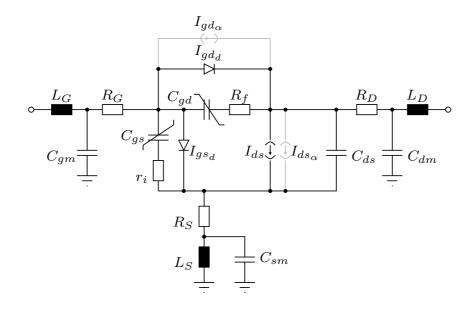

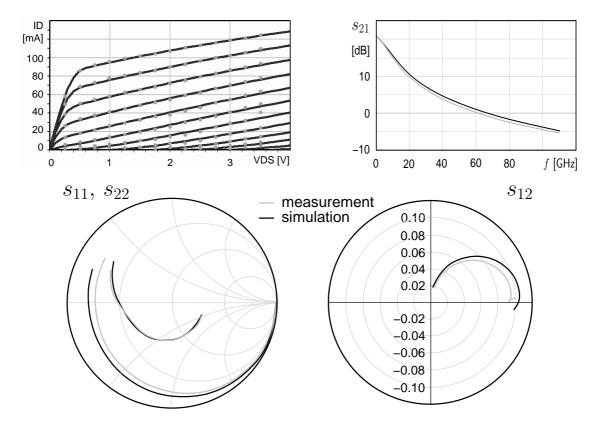

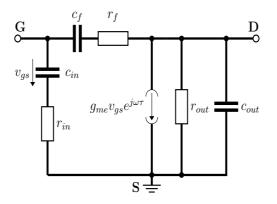

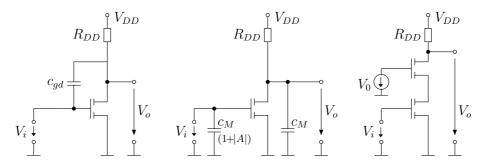

The radio frequency behavior of the HEMT can be described by a lumped element model as depicted in figure 2.15. There is a distinction between intrinsic parts representing the active device and extrinsic elements linked to metallic pads as part of the input lines required to connect the device to the outer world.

Figure 2.15: Small signal equivalent circuit of a HEMT.

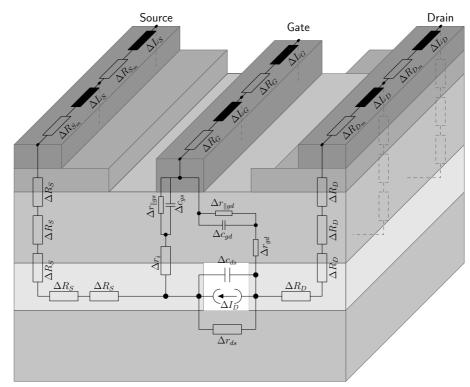

A physical interpretation of the lumped elements for the HEMT is sketched in figure 2.16.

Figure 2.16: Physical interpretation of the intrinsic lumped elements model neglecting impact ionization ( $r_{im}$ ,  $g_{m_{im}}$ ,  $c_{im}$  and  $I_{im}$ ) found in the small signal equivalent circuit in figure 2.15.

Elements are distributed along the device periphery. In this parallel plate capacitor model, the input capacitance  $\Delta c_{gs}$  is formed between the gate and the source-side charges. The effective distance between the gate and source-side charges depends on biasing conditions and is in the order of the barrier thickness. Similar for the feedback capacitance  $\Delta c_{gd}$  and output capacitance  $\Delta c_{ds}$  where effective distances strongly depend on the expansion of the channel drift zone. Parallel resistors  $\Delta r_{\parallel gs}$  and  $\Delta r_{\parallel gd}$  describe vertical leakage across the Schottky barrier. The access resistance of the device is formed as a series of drain and source resistors  $\Delta R_D$  and  $\Delta R_D$  that itself consist in parts to the channel, barrier and the ohmic contact. Neglecting impact ionization, the output conductance is given by  $\Delta r_{ds}$  representing short channel effects linked to the gate length and leakage through the substrate. For increasing drain voltage, impact ionization lowers the output conductance as considered by additional current sources in the small signal equivalent circuit in figure 2.15.

Elements of the small signal equivalent circuit can be approximately extracted from frequency dependent scattering parameter measurements described in [63] and [64]. Parasitic capacitances of the extrinsic device might be gained from "dead" devices having no channel or from active devices under "cold", deep pinch-off conditions. For the resistive and inductive parts, extractions can be carried out from shortened devices (drain-source) or from active devices under "hot", strong forward bias conditions. "Dead" structures offer only the pure metallic part of the parasitic elements. The "hot-cold" method includes depletion effects coming from the semiconductor. Yet, the "hot" measurement may damage sensitive devices due to strong forward gate currents. While extrinsic elements strongly depend on the geometric aspects of the device like pad arrangement and number of gate fingers, the intrinsic parameters linearly scale with the gate width. In order to describe the active devices within a scalable small signal model, devices of different gate width but similar gate configuration have to be characterized and fitted to the geometrical variations.

The small signal model may be extended for some large signal modulation, by fitting lumped elements along the load line. However, this approach is quite inaccurate due to non-linear effects such as current dispersion related to traps or impact ionization [65, 66]. RF-key parameters like the transit  $f_T$  and maximum oscillation frequency  $f_{max}$  can be brought into relation with small signal equivalent circuit elements. Two definitions are found for the transit frequency as given in equation 2.30 including or neglecting the feedback capacitance  $c_{gd}$ . For a high transit frequency, a high transconductance and small capacitances are required.

$$f_{T_i,c} = \frac{g_m}{2\pi(c_{gs} + c_{gd})}$$

and  $f_{T_i} = \frac{g_m}{2\pi c_{gs}}$  (2.30)

$F_{max}$  can be approximated by equation 2.31 [67]. To optimize  $f_{max}$ , a high transit frequency is needed on the one hand but also a low source and gate resistance as well as a low feedback capacitance  $c_{qd}$ .

$$f_{max} = \frac{f_{T_i}}{\sqrt{4g_{ds}(r_i + R_G + R_S) + 2\frac{c_{gd}}{c_{gs}}\left(\frac{c_{gd}}{c_{gs}} + g_m(r_i + R_G + R_s)\right)}}$$

(2.31)

#### 2.3.2 Noise considerations

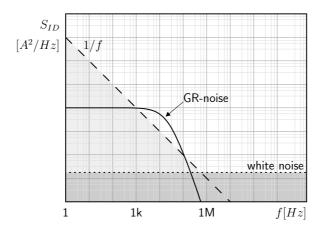

All electronic devices show small deterministic fluctuations in measured parameters called noise. Four types of noise are of importance in semiconductors.

- Thermal noise: Any resistance R shows spontaneous current or voltage fluctuations according to  $S_V = 4k_BTR$  or  $S_I = 4k_BT/R$ . The spectrum thermal noise is white whatever the nature of the conduction process or the mobile charge carriers.

- Shot noise: The current carried by electrons that cross a potential barrier in a semiconductor a randomly generated and lead to fluctuations around the current I with the white spectrum  $S_I = 2qI$ .

- Generation-recombination noise: The number of free electrons N in the conduction band may fluctuate because of generation and recombination processes.  $S_N = \overline{\Delta N^2} / N^2 \cdot 4\tau / (1 + \omega^2 \tau^2)$  where  $\tau$  is the characteristic trap relaxation time usually in the range of  $10^{-6} \dots 10^{-3}$  s.

- 1/f-noise or flicker noise: This is a fluctuation in the conductance with a power spectral density proportional to f<sup>-γ</sup> and γ = 1.0±0.1 in a wide frequency range [68]. Unlike the first three well understood noise sources above, the origin of the 1/f noise is still open.

Typical noise spectra of above mentioned noise sources are sketched in figure 2.17. Thermal and shot noise contribute to a constant noise level over frequency and dominate the noise performance of the device at high frequencies. At lower frequency, recombinationgeneration or GR-noise with Lorentzian characteristics may be observed on top of the 1/fflicker-noise spectrum. The origin of flicker noise is still open. For finite values for the integral of the power density and the Fourier transform, the slope of the spectrum has to be steeper than -1 below and above a lower and upper cut off frequency. While the upper cut off frequency is hidden by RF-noise in the MHz-regime, the lower cut off frequency could not be experimentally determined by measurements down to  $10^{-6}$  Hz [69].

Figure 2.17: Frequency behavior of different noise sources.

Flicker noise has been considered by McWhorter as a surface effect [70], where the 1/f-spectrum is explained by the superposition of several GR-centers of different recombination constants. With respect to the large bandwidth of flicker noise, relaxation times of a material have to cover a very wide range from  $10^6$  to  $10^{-6}$  s. In GaAs and InP, 1/f-noise has been described by charge mobility fluctuations linked to lattice scattering in the semiconductor material [71].

Flicker noise plays an important role in non-linear oscillator or mixer applications showing up-conversion of the 1/f-noise spectra. Low frequency noise is of minor importance for the W-band low noise amplifiers in this work and was not regarded in the RF-noise model.

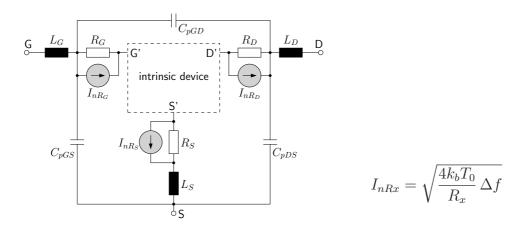

#### 2.3.3 Noise model

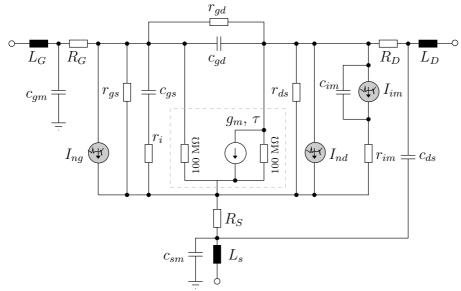

Resistors of the extrinsic device model shown in figure 2.18 contribute to white RF-noise which is constant over frequency with noise currents  $I_{nRx}$  described by pure thermal noise. It is related to charge velocity fluctuations within the resistors caused by the thermal energy of the carriers. The temperature  $T_0$  of the resistors normally is close to the ambient temperature with a slight increase due to device operation and self heating.

Figure 2.18: Extrinsic noise elements (grey) of the HEMT creating thermal or Johnson noise.

For the intrinsic device, the contribution to RF-noise may be described by two noise sources - the channel noise source  $I_{nd}$  and the correlated gate noise source  $I_{ng}$  [72]. Noise currents and the correlation coefficient C are given in equation 2.34 with the dimensionless constants P and R.

$$\overline{|I_{nd}|^2} = 4k_b T_0 \Delta f g_m P \tag{2.32}$$

$$\overline{|I_{ng}|^2} = 4k_b T_0 \Delta f \frac{\omega^2 C_{gs}^2}{g_m} R$$

(2.33)

$$jC = \frac{I_{ng}^{\star} \bar{I}_{nd}}{\sqrt{|I_{ng}|^2 |I_{nd}|^2}} .$$

(2.34)

A more detailed view on intrinsic noise sources is given in figure 2.19. There is shot noise  $I_{nL_S}$  and  $I_{nL_D}$  linked to leakage currents  $I_{Lx}$  across the non-ideal Schottky barrier. The noise currents are given by  $I_{nL_x} = \sqrt{2q I_{Lx} \Delta f}$ . Since shot noise is also white or constant over frequency, usually, its contribution is modeled by an equivalent thermal noise source [73] with an equivalent noise resistance  $R_{qs}$  and noise temperature  $T_{GS}$ .

Figure 2.19: Intrinsic noise elements (grey) of the HEMT.

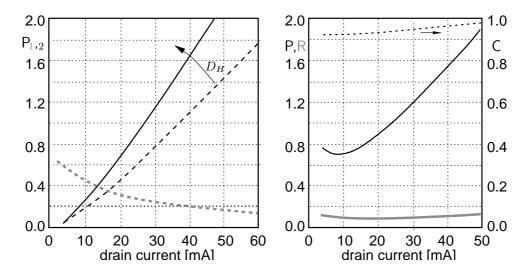

Generation-recombination noise linked to impact ionization is taken into account by the current source  $I_{im}$ ; the frequency dependence is modeled by the noiseless resistor  $r_{im}$  and capacitor  $c_{im}$ . The channel noise sources are linked to velocity fluctuations of electrons due to phonon and Coulomb scattering. In a HEMT structure, the part related to Coulomb-scattering is lower compared to the MESFET due to the spacial separation of the channel electrons from the positively charged activated donor-states in the barrier layer. Electron transport properties in the channel of the device show a strong electrical field dependence discussed before (fig. 2.5 page 11). The source of the channel noise  $I_{nd}$  is divided into two parts. Before electrons reach velocity saturation, they contribute to Johnson or thermal noise which is inversely proportional to the drain current [74].

$$\overline{|I_{nd_1}|^2} \sim 4 \, k_B \, T_0 \Delta f \frac{|V_p|}{I_{ds} \, r_{ds}^2} \tag{2.35}$$

The second part of channel noise comes from the high-field drift zone. Here, the high-field diffusion constant  $D_H$  introduced by Pucel [75] describes the formation of dipole layers that drift through the saturation velocity zone. Drift diffusion noise of the channel  $|\overline{I_{nd_2}}|^2$  is proportional to the high-field diffusion constant  $D_H$  and the drain current; a high saturation velocity  $v_{sat}$  helps to reduce diffusion noise [76]:

$$\overline{|I_{nd_2}|^2} \sim 4k_B T_0 \,\Delta f D_H \frac{I_{ds} d_{gc}}{W^2 v_{sat}^3 r_{ds}^2} \tag{2.36}$$

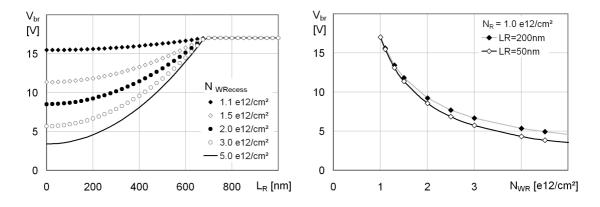

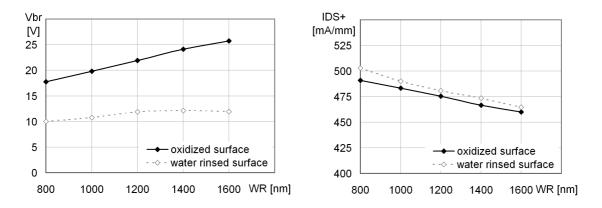

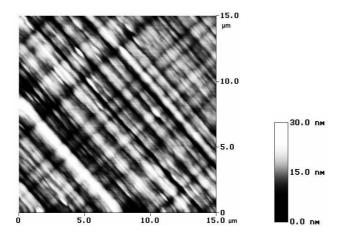

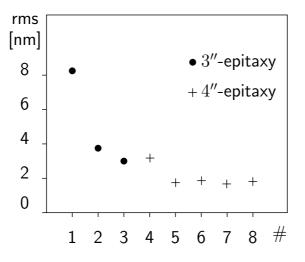

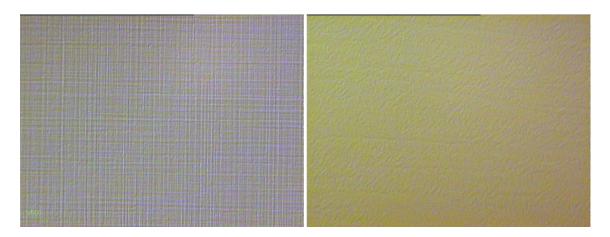

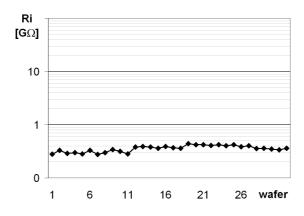

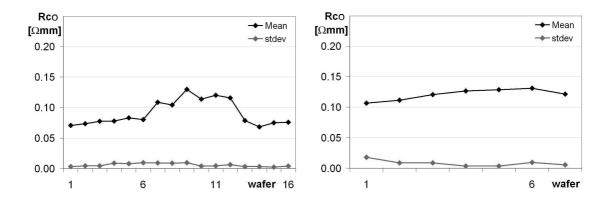

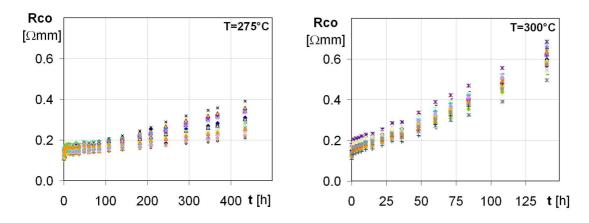

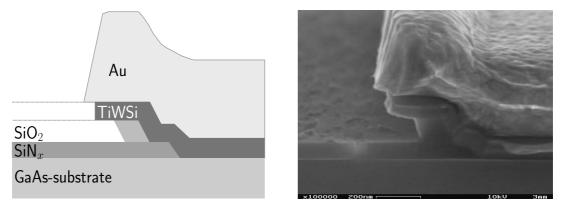

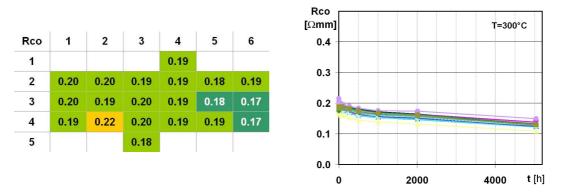

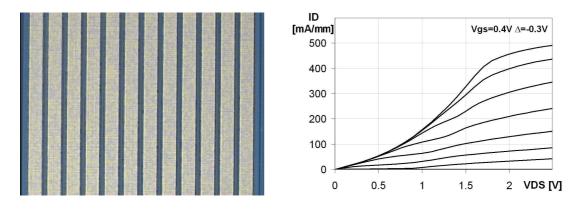

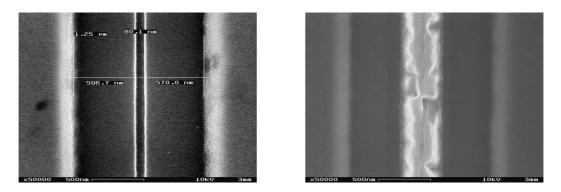

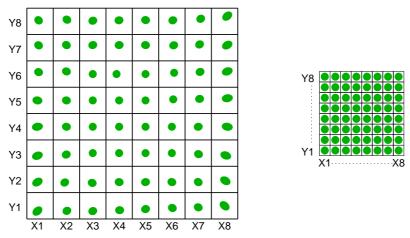

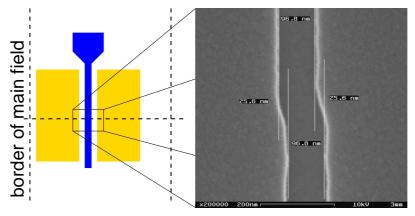

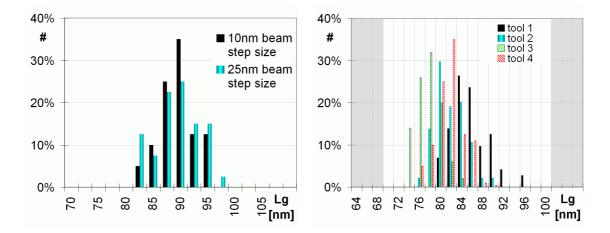

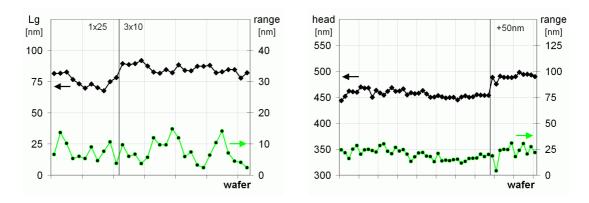

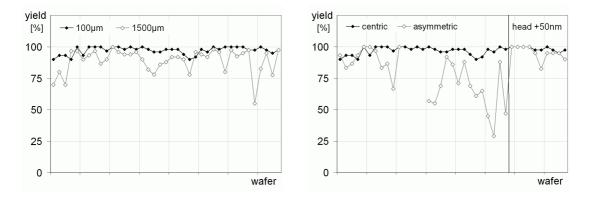

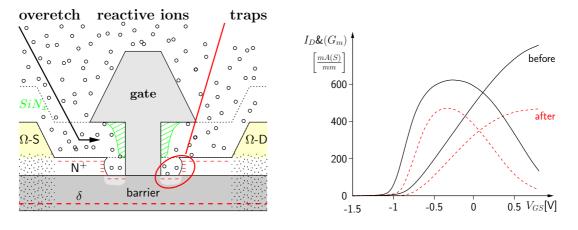

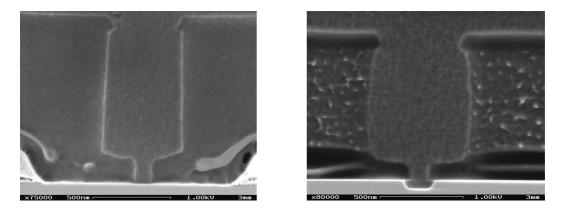

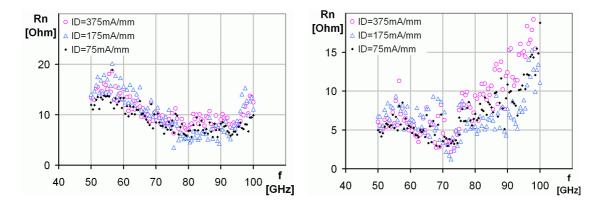

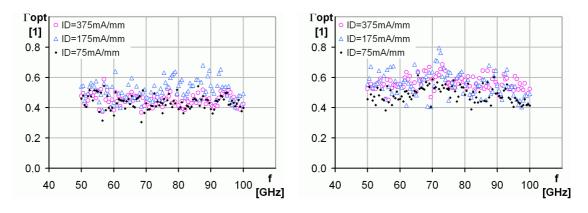

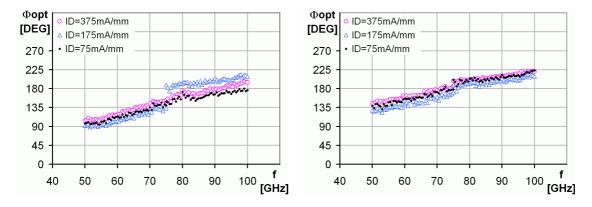

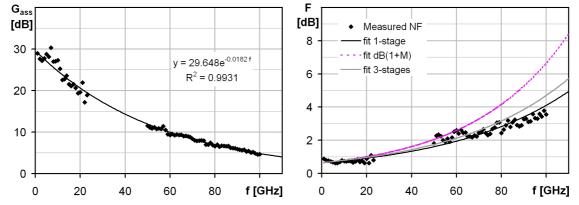

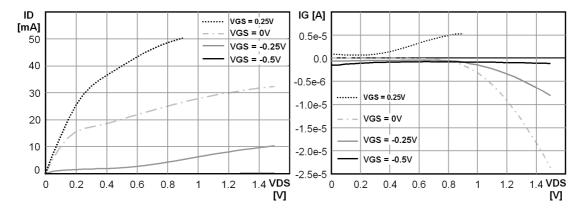

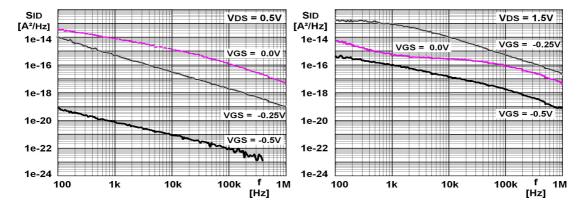

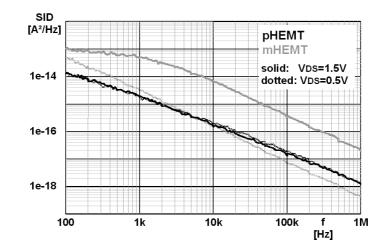

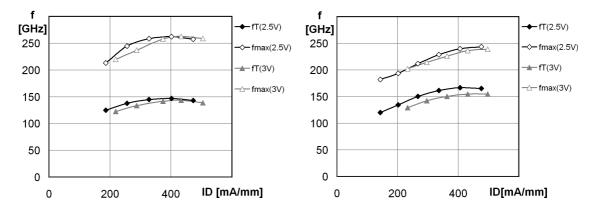

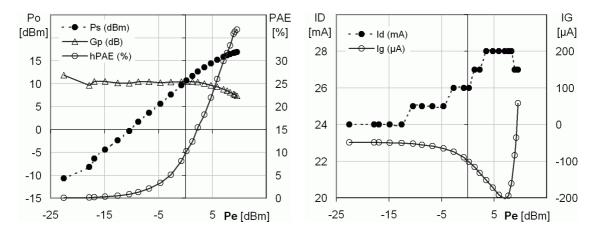

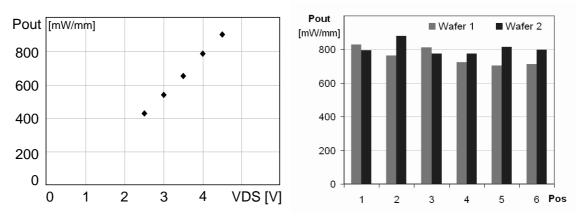

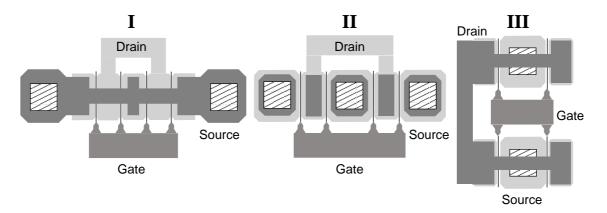

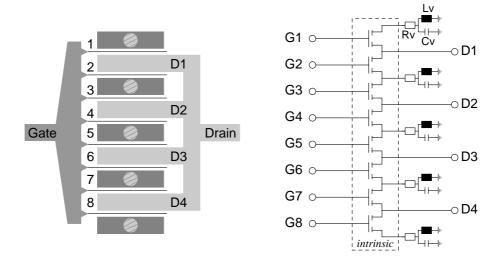

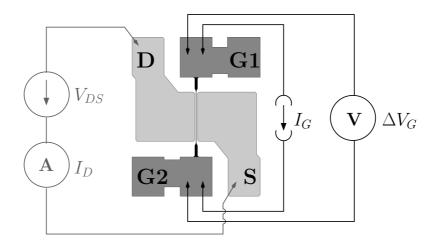

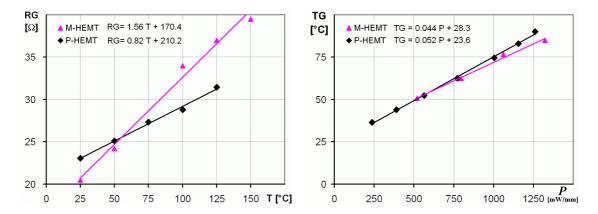

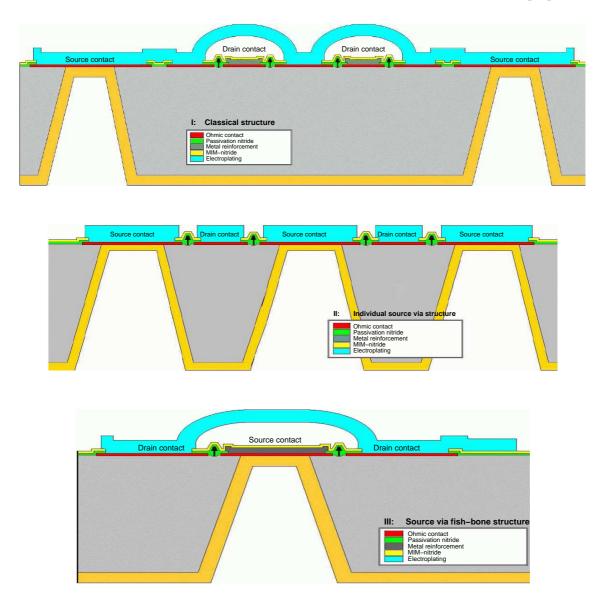

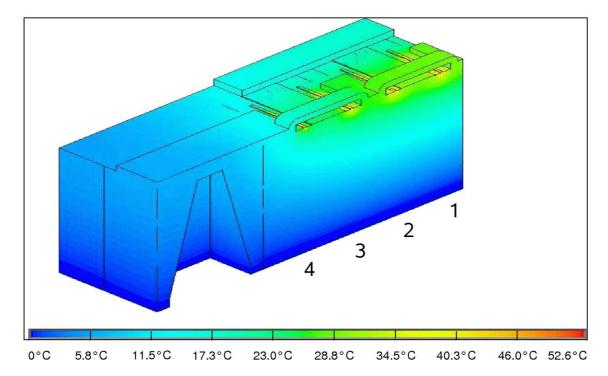

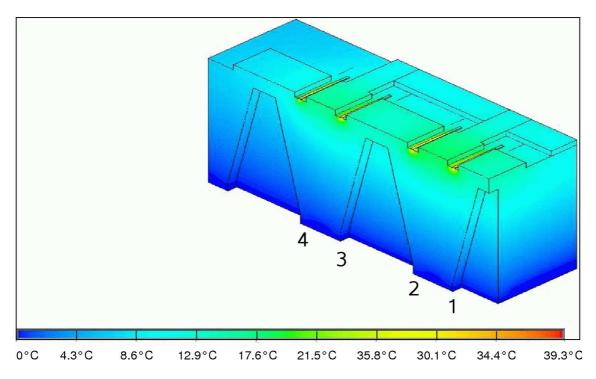

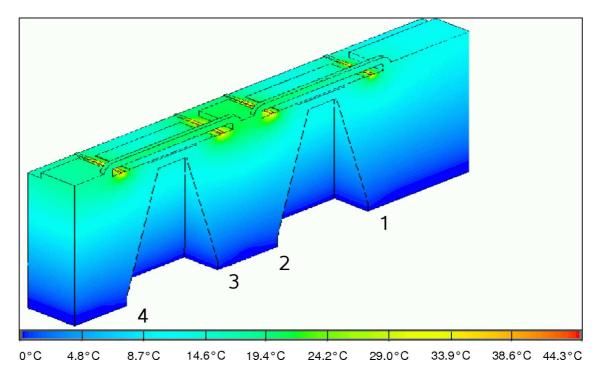

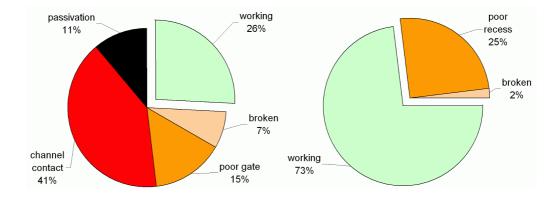

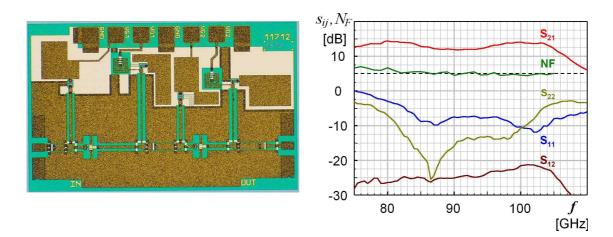

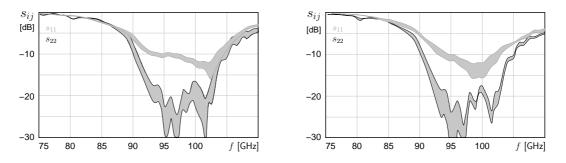

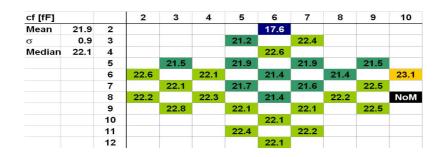

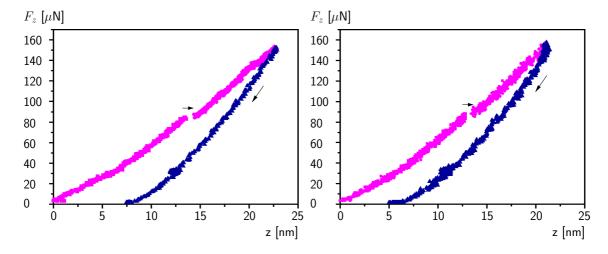

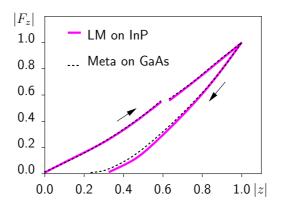

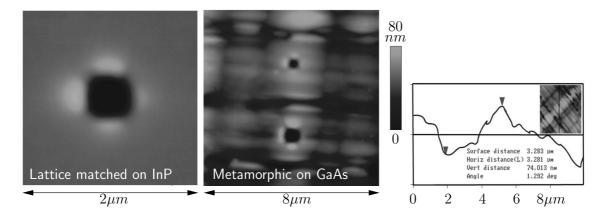

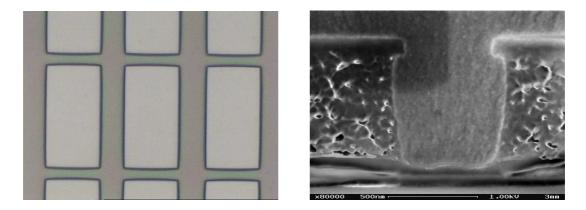

Since both parts of channel noise behave oppositely, there is an optimum drain current for minimum channel noise. Drift-diffusion noise is the more dominating factor for open channel and the optimum drain current is found at comparably low current levels as shown in the left part of figure 2.20 [76]. Fluctuations of the current in the channel are directly transferred to the gate by capacitive coupling and create an additional noise source  $I_{ng}$  partly correlated with channel noise. Similar for the gate noise, there are two parts related to thermal and diffusion noise as considered by Bergamaschi in detail [76]. There, the principle noise parameter behavior over the drain current is shown in the right part of figure 2.20, where P and R represent the channel and gate-noise, and C the correlation factor.