# **Technology and Characterization of InAIN/GaN FETs**

# DISSERTATION

zur Erlangung des akademischen Grades eines

# **DOKTOR-INGENIEURS**

(DR.-ING.)

der Fakultät für Ingenieurwissenschaften und Informatik der Universität Ulm

von

# Mohammed Alomari aus Dayr Yusef

Gutachter: Prof. Dr.-Ing. Erhard Kohn

Prof. Dr.-Ing. Andrei Vescan

Amtierender Dekan: Prof. Dr.-Ing. Klaus Dietmayer

Ulm, 12.10.2012

I would like to acknowledge all those who participated and assisted me in this work. I am greatly indebted for Prof. Erhard Kohn for his constant guidance and encouragement through my Ph.D. years. I am also indebted for Dr. F. Medjdoub who first introduced me to the field of GaN HEMTs, and was a constant source of inspiration and activity. I am also grateful for my colleagues in EBS for the nice work atmosphere they created, and their constant collaboration, specially David Maier for his patient assistance in many technical matters, Patrick Herfurth for many fruitful discussions, and Stefano Rossi for efficiently managing the diamond growth aspect in this work.

I am also grateful for the exceptional GaN growth teams in EPFL and III-V Lab for the excellent material quality they provided. Many thanks also to Clemens Ostermaier from the University of Wien for his valuable collaboration during our partnership in the EU projects.

Finally I would like to thank my brother Nabil, who has been a constant source of support and wisdom. Many thanks Nabil.

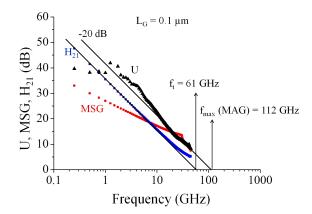

In this work the lattice matched In<sub>0.17</sub>Al<sub>0.83</sub>N/GaN heterostructure was investigated. The work started by establishing the main features of this heterostructure in a HEMT configuration through the investigation of the DC, small signal and large signal characteristics of planar HEMTs. The study included heterostructures with variable barrier thicknesses, but still thinner than what is conventionally used in AlGaN/GaN HEMTs. Using these heterostructure a barrier scaling study combined with static simulations revealed an initially low surface potential, which is combined with the high polarization discontinuity of this heterostructure, thus yielding HEMTs with high current densities and high aspect ratios. Current densities above 1 A/mm and up to 2.4 A/mm could be achieved in this work and the HEMTs demonstrated high cut-off frequencies, scaling with the gate length, up to an  $f_t$ = 61 GHz and  $f_{max}$ = 112 GHz for 0.1 µm long gates. In addition, the high thermal stability of the heterostructure was established through a series of storage and operating tests at temperatures above 500 °C and up to 1000 °C. This allowed the optimization of a thermal oxidation process to reduce the HEMT gate leakage but most importantly as an efficient preparation for surface passivation. The oxidation process was investigated by using actual HEMT structures, with the corresponding DC, small signal and large signal analysis, and also dedicated structure to investigate the effect of localizing the oxidation process around the gate area, which is the area of interest for power operation. This passivation scheme yielded a lag free device at 4 GHz with output power density of 11.6 W/mm at a drain voltage of 20 Volts, so far the highest reported for this heterostructure. In addition, relying on the initial experiments indicating the heterostructure stability, nanocrystalline Diamond overgrowth experiments were conducted for efficient heat extraction from the device, as was evaluated using thermal simulations. The Diamond deposition conditions were optimized to yield films with high thermal conductivity reaching 1000 W/mK in the vertical direction of heat flow toward the position where the heat sink would be placed. These conditions were restricted to deposition temperatures above 700 °C, with bias enhanced nucleation also conducted above 700 °C, with slow deposition rate of around 0.1 µm/hour. A series of experiments were conducted to verify the heterostructure stability under these conditions by fabricating devices after growth and complete removal of the overgrown Diamond film. After establishing the heterostructure stability, a series of experiments progressed toward obtaining a fully Diamond coated HEMT by growth experiments on gateless HEMTs and the subsequent optimization of the ohmic contact, and the growth on gateless HEMTs with different passivation and the subsequent optimization of the passivation deposition process, to reach finally a fully processed Diamond coated HEMT with 1 µm Diamond film thickness. This was done using two different Diamond nucleation techniques, namely the bias enhanced nucleation and the nanoparticle seeding. The first Diamond overgrown GaN HEMTs operating at frequencies above 1 GHz were demonstrated, keeping a relatively high current density above 1 A/mm. The optimization of this

process also enabled continuous operation at very high temperatures above 500 °C and up to 1000 °C, thus reaching with this heterostructure to limits beyond the best achieved with any other semiconductor. Moreover, another approach of combining Diamond with GaN through direct heteroepitaxy of AlGaN/GaN HEMT structure on single crystalline Diamond was investigated, and achieved through a dedicated effort from the growers, enabling the demonstration of the first ever reported GaN HEMT on Diamond substrates.

#### Contents

```

1 INTRODUCTION AND THESIS OUTLINE

2 GAN BASED HETEROSTRUCTURES: ADVANTAGES AND CHALLENGES

2.1 III-N group electronics

2.2 Gan based heterostructures for HEMT applications

The formation of 2DEG

2.3 Lattice matched InAlN/GaN heterostructure barrier scaling properties

Estimation of the heterostructure surface potential

Basic model of GaN HEMTs

2.4 Technological limitations: Barrier scaling, thermal and chemical limita-

2.5 Intrinsic limitations: Current collapse and device self heating

27

Main power limitation: Current collapse

2.5.2

Device self-heating

29

3 LATTICE MATCHED INALN/GAN HETEROSTRUCTURE FOR HEMT APPLICATIONS

3.1 Advantages and state-of-the-art of LM-InAlN/GaN HEMTs

3.2 Heterostructure growth

3.3 HEMT basic fabrication technology and characterization

3.3.1 Barrier scaling properties

36

3.4 Thermal stability and high temperature operation of LM-InAlN/GaN HEMT

3.5 Thermal oxidation of InAlN

41

3.6 HEMT passivation and output power performance

3.6.1 MOSHEMT with local oxide recess

COMBINING DIAMOND AND GAN: ADVANTAGES AND CHALLENGES

55

4.1 Nanocrystalline Diamond on GaN

NCD growth conditions and film properties

4.1.2 HEMT stability under NCD growth conditions

4.1.3 Development of high thermally stable metallization scheme

66

4.2 NCD coated HEMTs

4.2.1 Fully overgrown HEMTs using BEN

4.2.2 Fully overgrown HEMTs using nanoparticles seeding

4.3 GaN on single crystalline Diamond

5 CONCLUSIONS AND OUTLOOK

A APPENDICES

A.1 HEMT FABRICATION LITHOGRAPHIC STEPS

A.2 HEMT STATIC SILVACO SIMULATION FILE

BIBLIOGRAPHY

83

```

V

| Figure 1  | A schematic of (a) the ideal hexagonal lattice of III-nitride and (b) the tetrahedron shaded in (a) with the polarization vectors induced by the difference in electronegativity of the constituent nitrogen and                                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2  | metal atoms. 8 (a) Lattice constant $a_0$ and (b) $c_0$ in dependence of alloy composition. A LM-InAlN alloy with 83% Al content has the same lattice constant $a_0$ as GaN. (c) Alloy bandgap in dependence of the lattice constant $a_0$ and (d) the spontaneous polarization in dependence of $a_0$ . After [1].                                             |

| Figure 3  | Theoretical values of the piezoelectric polarization ( $P^{pz}$ ) for III-N alloys grown on relaxed GaN buffer.                                                                                                                                                                                                                                                 |

| Figure 4  | Schematic of the formation of polarization induced bound sheet charge density in polar GaN. The source of these charges is not considered at the moment.                                                                                                                                                                                                        |

| Figure 5  | Schematic of polarization-induced interface charge in pseudomorphically grown heterostructure. 12                                                                                                                                                                                                                                                               |

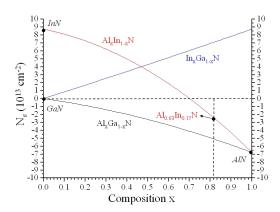

| Figure 6  | Theoretical maximum 2DEG sheet charge density $(N_s)$ for III-N alloys grown on relaxed GaN buffer with Ga-face polarity in dependence of alloy composition.                                                                                                                                                                                                    |

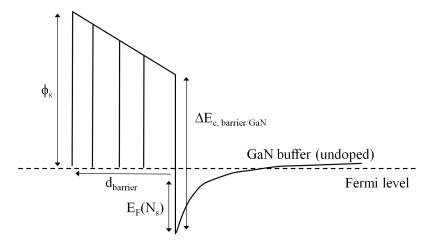

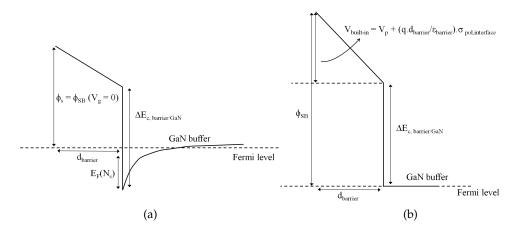

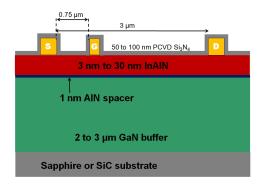

| Figure 7  | Band diagram of a GaN based HEMT with barrier of thickness $d_{\text{barrier}}$ and an unpinned surface potential $\phi_s$ . In this case N <sub>s</sub> is constant and independent of the barrier thickness, and its value is expressed by equation 2.8, provided that $\phi_s$ is known. The case of a pinned surface potential is described in Fig. 9c 14   |

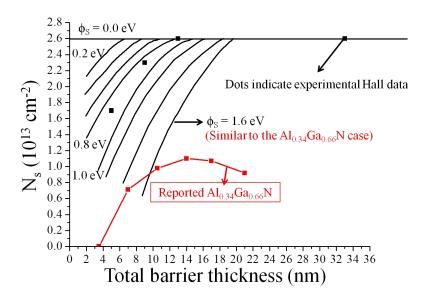

| Figure 8  | Experimental Hall $N_s$ values vs. $d_{barrier}$ compared to calculated values using different surface potential levels $\phi_s$ . Also shown in the graph data for the AlGaN/GaN case from [2].                                                                                                                                                                |

| Figure 9  | Simulated LM-InAlN/GaN band diagrams for the case of (a) a fully undepleted surface resulting in a flat band in the barrier (b) fully depleted surface or no source of electrons to provide for the channel, resulting in a flat band in the buffer (c) with limited density of donor like surface traps, equal to the polarization discontinuity, at an energy |

| Figure 10 | of 0.8 eV below the conduction band. 17 Schematic of HEMT band diagram under the gate (a) in case of no applied gate voltage $\phi_s$ equals the contact potential $\phi_{SB}$ , and (b) $\phi_s$ is controlled by the gate voltage, as shown here for the case of a pinched-off channel. 19                                                                    |

- Figure 11 Schematic of gate diode characteristics for a single barrier HEMT. The leakage current in the forward direction follows a tunneling mechanism, and similarly in the reverse bias direction up to channel pinch-off, where the characteristics resemble a current limiter. 23

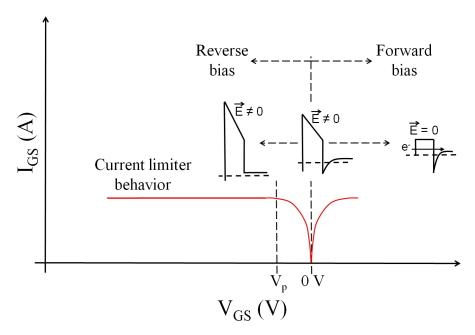

- Figure 12 Schematic of I-V characteristics of GaN based HEMT under DC operation and under current collapse conditions. The insets show the surface configuration that leads to the current collapse, due to lateral charge injection in the surface donor traps. 28

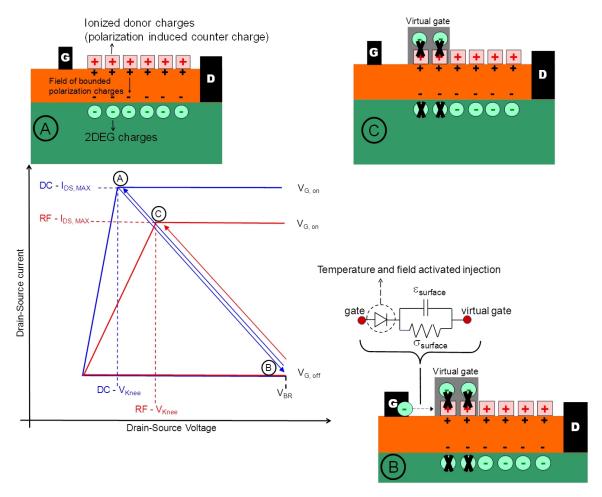

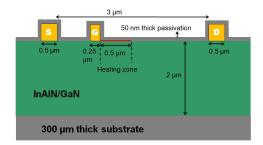

- Figure 13 Cross section of the typically used heterostructure and device dimensions. 34

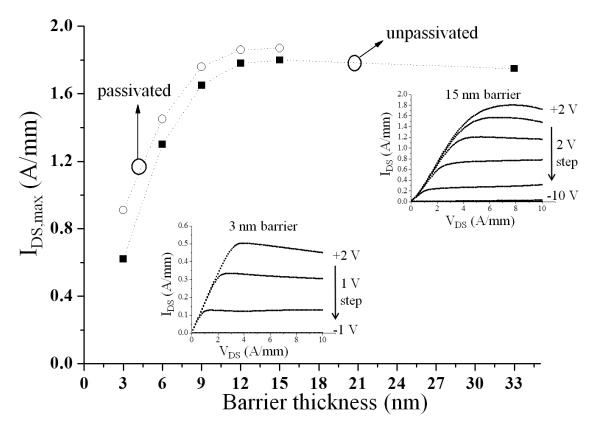

- Figure 14 The barrier down-scaling effect on the HEMT characteristics causes a decrease in  $I_{DS,max}$  and increase in  $g_m$  (not shown here). PCVD  $Si_3N_4$  passivation seems to reduce the surface potential effect. However, due to the relatively small surface potential of LM-InAlN/GaN HEMT, fully functional devices can be obtained with barriers as thin as 3 nm.

- Figure 15 The barrier down-scaling also causes a (a) decrease in the contact resistance (b) decrease in the pinch-off voltage and (c) increase in the reverse gate leakage current. 38

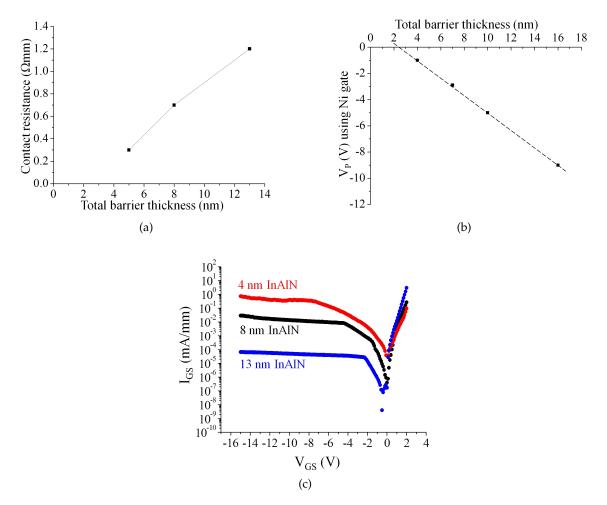

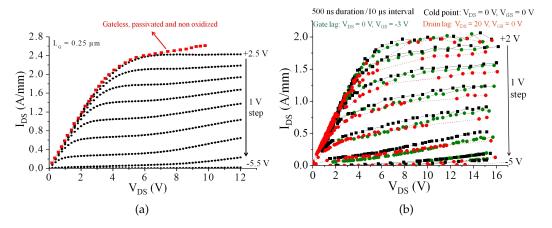

- Figure 16 DC output characteristics of PCVD-Si<sub>3</sub>N<sub>4</sub> passivated LM-InAlN/GaN HEMTs before and after 30 min. stress at 1000 °C in vacuum for (a) a 15 nm barrier (b) 3 nm barrier and (c) gate diode characteristics of the 3 nm barrier HEMT before and after the stress test. 40

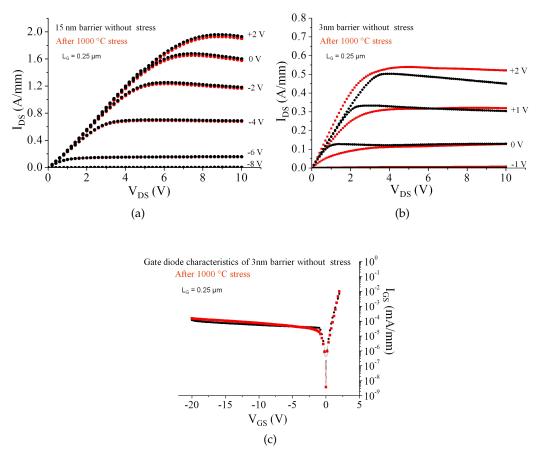

- (a) Long time operation test of 10 nm InAlN/GaN HEMT. The HEMT operated for 250 hours at 500 °C and 250 hours at 600 °C and 25 hours at 700 °C. (b) The sudden HEMT failure at 700 °C is due to metallization break and melting short circuiting the source and drain. The unbiased devices were not damaged and could be operated normally after the test.

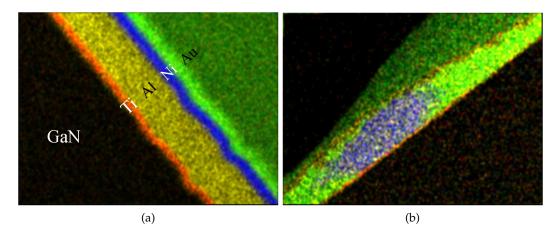

- Figure 18 TEM color-coded elemental maps (performed by E. Elektronen-mikroskopie, Ulm) of the ohmic contact stack (a) before the annealing step and (b) after annealing at 850 °C for 30 seconds. Ti largely stays at the interface with the HEMT and Al disperses everywhere. Au and Ni on the other hand tend to segregate causing an excess of non alloyed metal which could later electromigrate at high temperatures specially for a ductile metal like Au. 42

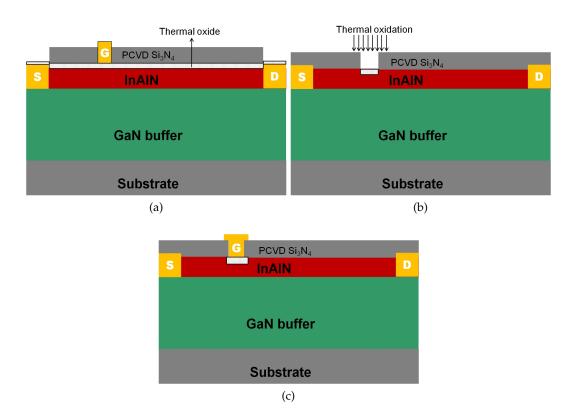

- Figure 19 Cross section of (a) a MOSHEMT fabricated using a global oxidation scheme (b) local oxidation scheme used to characterize the effect of oxidation before gate deposition and (c) MOSHEMT with thermally generated oxide recess. 43

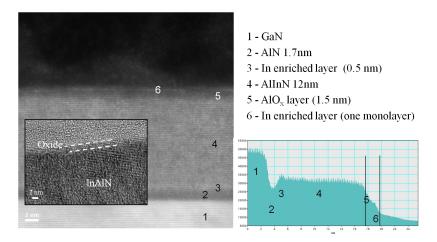

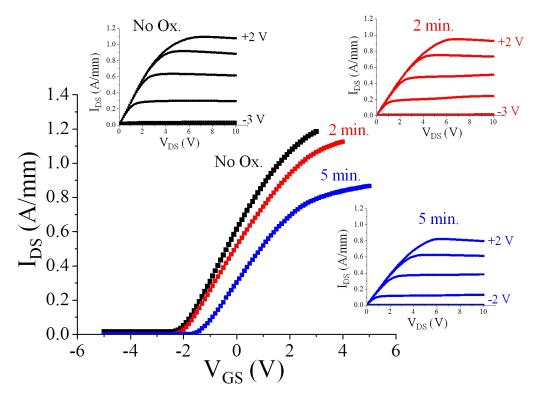

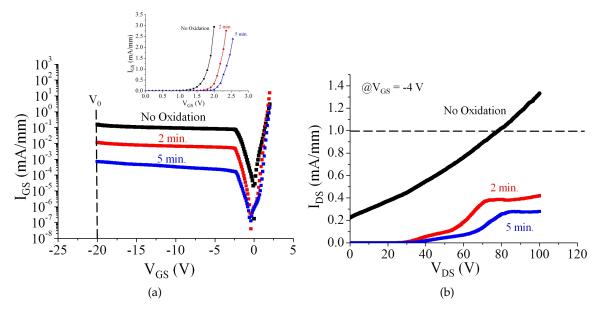

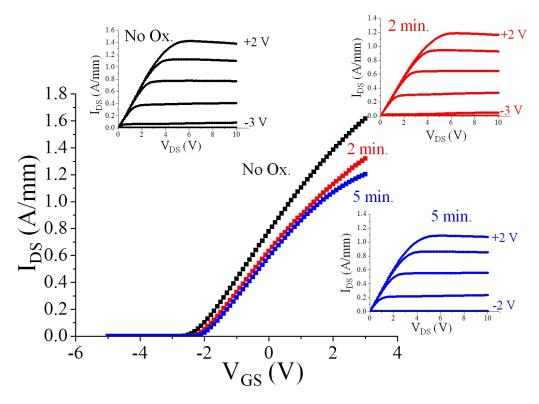

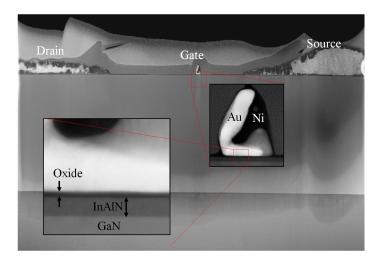

Figure 20 HAADF-STEM and HR-TEM cross sections (performed by E. Elektronenmikroskopie, Ulm) of initially a 15 nm barrier LM-InAlN/GaN oxidized thermally for 5 minutes at 800 °C. The HAADF-STEM elemental analysis (right insert) identifies the composition of the heterostructure after oxidation, and shows that the formed oxide is mostly  $Al_2O_3$ . 44 Transfer characteristics of 0.25  $\mu$ m x 50  $\mu$ m MOSHEMTs prepared by thermal oxidation compared to non oxidized HEMT. The insets show

thermal oxidation compared to non oxidized HEMT. The insets show the output characteristics ( $V_g$  in 1 V steps) of the devices. 44

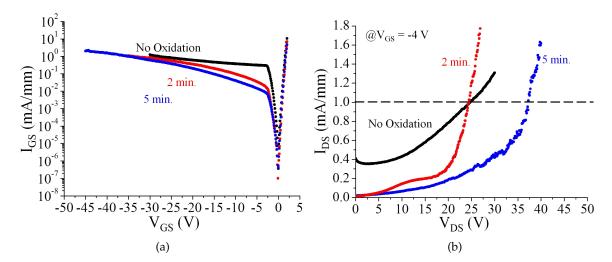

Figure 22 (a) Gate diode characteristics and (b) 3-terminal breakdown defined at 1 mA/mm of the HEMT and MOSHEMTs shown in Fig. 21. In addition to an increase in the gate turn on voltage, reduction in gate leakage current and increase in the 3-terminal breakdown of the devices were observed with increased oxidation time. 45

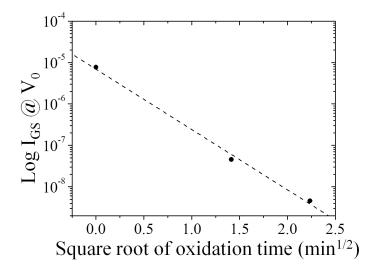

Figure 23 Dependence of leakage current (at  $V_g$  = -20 V) on the square root of oxidation time indicates an initially diffusion limited oxidation mechanism similar to the case of Silicon oxidation. 46

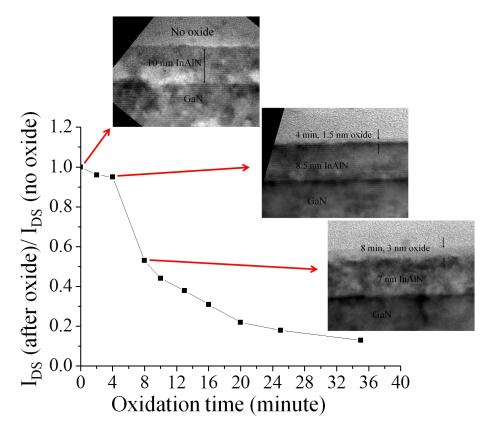

Figure 24 Relative change in  $I_{DS}$  with oxidation time. The insets show TEM cross sections (performed by MFA) of the layer before oxidation and after 4 and 8 minutes of oxidation. 47

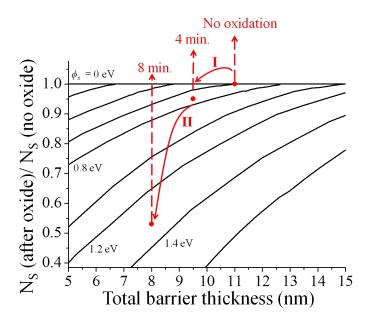

Figure 25 The effect of oxidation on carrier density using the data obtained from Fig.24 and 8 can be explained by (I) a constant surface potential for reduced barrier thicknesses at short oxidation times and (II) an increase with the surface potential and barrier thickness. After 8 min. of oxidation,  $\phi_s$  increases to approximately 1.1 eV. 48

Figure 26 Transfer characteristics of 0.25  $\mu$ m x 50  $\mu$ m MOSHEMTs shown in Fig. 21 after passivation with 200 nm PCVD Si<sub>3</sub>N<sub>4</sub>. The insets show the output characteristics ( $V_g$  in 1 V steps) of the devices. 49

Figure 27 (a) Gate diode characteristics and (b) 3-terminal breakdown defined at 1 mA/mm of the devices shown in Fig. 22 after passivation with 200 nm PCVD  $\mathrm{Si}_3\mathrm{N}_4$ . The passivation caused a degradation of the gate diode characteristics compared to the unpassivated devices (see Fig. 27a) due to surface current leakage in the  $\mathrm{Si}_3\mathrm{N}_4$  layer or at its interface, which reflected on the 3-Terminal breakdown of the device (see Fig. 27b) limiting it to 35 volts of source-drain bias in the best cases. 50

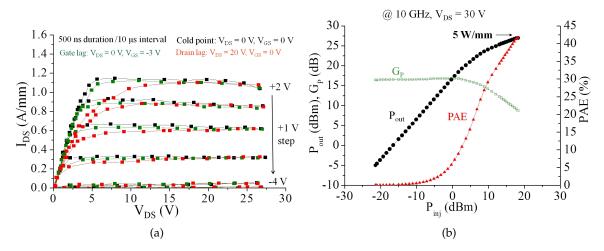

Figure 28 (a) Pulsed  $I_{\rm DS}$ - $V_{\rm DS}$  characteristics ( $V_{\rm GS}$  swept from -3 to 2 V by step of 2 V) at the quiescent bias points ( $V_{\rm DS0}$  = 0 V,  $V_{\rm GS0}$  = 0), ( $V_{\rm DS0}$  = 0 V,  $V_{\rm GS0}$  = -3) and ( $V_{\rm DS0}$  = 20 V and 25 V,  $V_{\rm GS0}$  = -3) of MOSHEMT with 2 min. oxidation and (b) the load-pull measurements of the MOSHEMT at  $V_{\rm DS}$  = 30 V. The measurements were performed by IEMN. 51

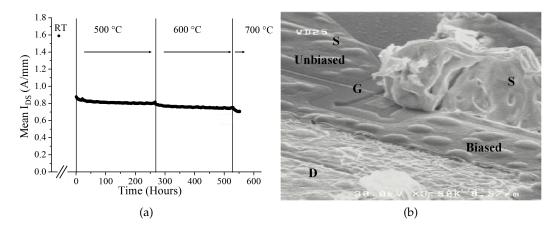

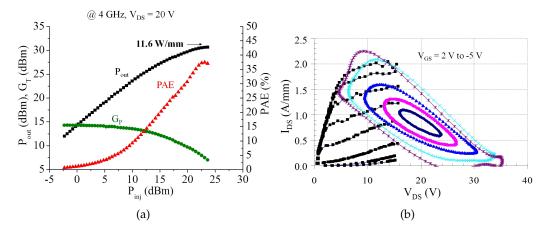

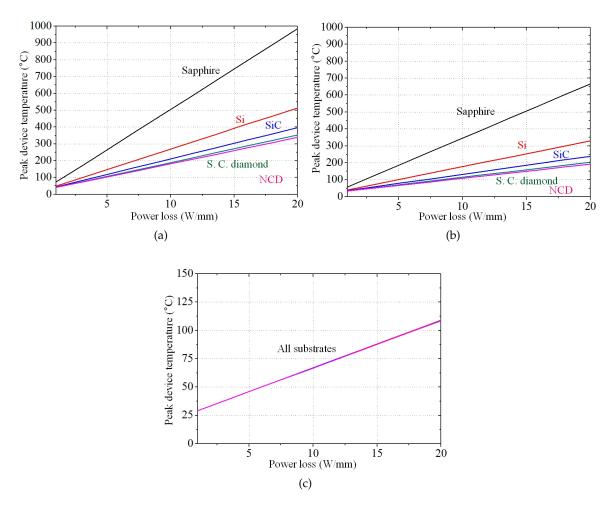

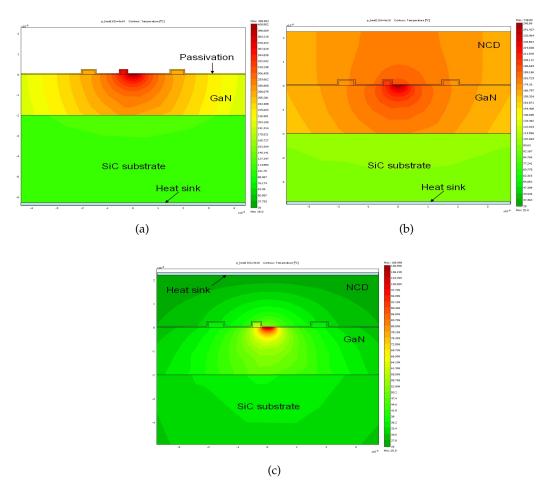

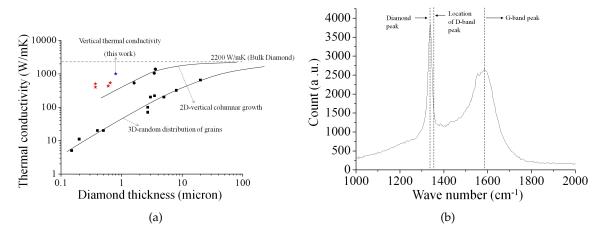

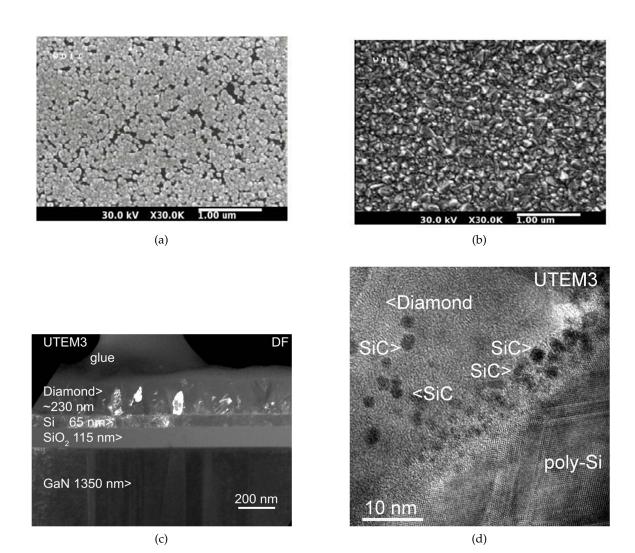

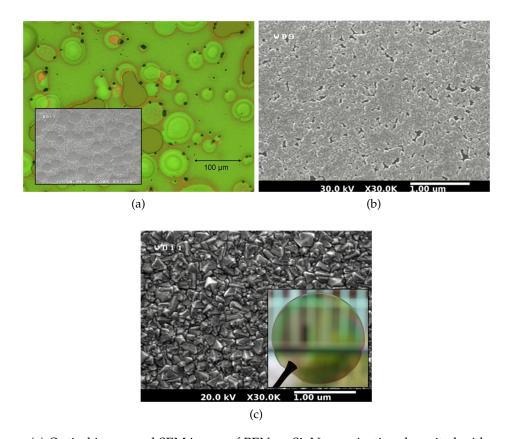

Figure 29 TEM cross section (performed by E. Elektronenmikroskopie, Ulm) of the MOSHEMT with 2 min. oxidation after thermal stress at 800 °C for 30 min. Despite the segregation and flow of Au in both the ohmic and gate contact no inter-diffusion into the oxide was seen, and the interface remained sharp and well defined. Figure 30 (a) DC output characteristics of 0.25 µm x 50 µm MOSHEMT with thermally generated oxide recess. The maximum current density of 2.4 A/mm in the layer could be accessed after oxidation. (b) Pulsed  $I_{DS}$ - $V_{DS}$  characteristics (performed by IEMN) of the device indicated a largely lag free device. Figure 31 (a) Load-pull measurements of the oxide recessed MOSHEMT at  $V_{DS}$  = 20 V and (b) Measured RF load lines for a class-A bias point superimposed on pulsed DC characteristics (cold point) of the device. No current compression is observed in the output ellipse, and the full current density of 2.4 A/mm could be accessed. The measurements were performed by IEMN. Figure 32 s-parameter measurements of 0.1 μm x 50 μm MOSHEMT with oxide recess. Figure 33 GaN HEMT device geometry used in the 2D FEM simulation. 56 Figure 34 HEMT maximum channel temperature as a function of power loss for different heat dissipation configurations. (a) For bottom heat spreader and heat sink, the device temperature depends on the substrate type. (b) For bottom heat spreader and heat sink but with a 2 µm NCD layer on top, a slight reduction in the maximum temperature of the device can be achieved. (c) Using a 2 µm NCD heat spreading layer with an attached heat sink on top, the device temperature is significantly reduced and is independent of the substrate type. Figure 35 Temperature distribution in the simulated HEMT structure on SiC substrate using different heat spreading configurations at a power loss of 20 W/mm (a) with heat spreader and heat sink on bottom (b) with heat spreader and heat sink on bottom but with top NCD layer (c) with top NCD heat spreader with an attached heat sink. Figure 36 (a) Collected thermal conductivity data of NCD films as function of the film thickness and structure([3, 4, 5, 6, 7, 8]). Also shown in the figure the thermal conductivities (measured by GLG) of the films grown in this work (denoted by stars) optimized for vertical thermal conductivity. (b) Raman spectroscopy of the grown films, showing the dominant Diamond content in the film. Figure 37 SEM images of (a) BEN nucleation and (b) NCD overgrowth on LM-InAlN/GaN. (c) TEM cross sections (performed by MFA) showed a continuous void free NCD layer nucleated from SiC clusters (d) propagating from the nucleation layer.

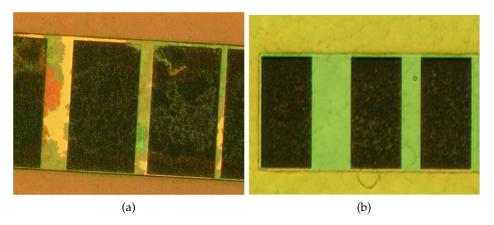

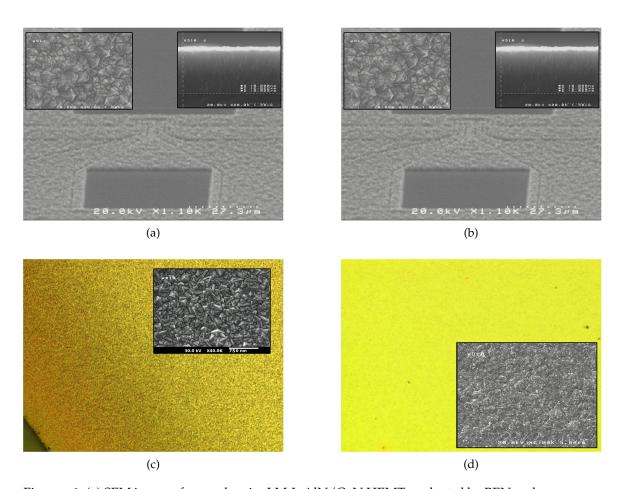

- Figure 38 (a) Standard Au-containing contacts did not survive the NCD growth process. (b) Au was removed from the stack and the gateless HEMTs could be overgrown. 65

- Figure 39 (a) Optical image and SEM image of BEN on  $Si_3N_4$  passivation deposited with ammonia precursor. Outgasing in the film prevented the growth of a closed layer. (b) BEN on  $Si_3N_4$  passivation deposited with  $N_2$  precursor. No outgasing was observed and high nucleation density is achieved allowing (c) closed films to be grown uniformly up to 2" wafers. 66

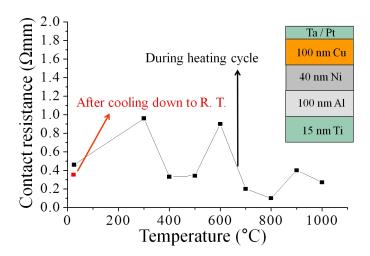

- Figure 40 TLM measurement of the Au-free ohmic contact stack (shown in inset) at temperature up to 1000 °C. This stack is compatible with NCD overgrowth. 67

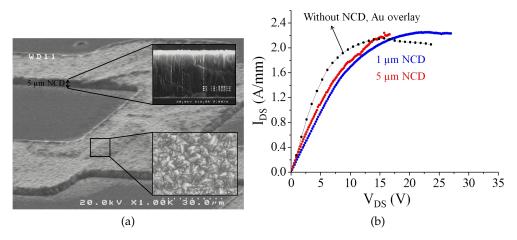

- Figure 41 (a) SEM images of 5 µm NCD layers grown on gateless LM-InAlN/GaN HEMT. (b) The DC characteristics are comparable to HEMTs with 1 µm NCD and without NCD. 68

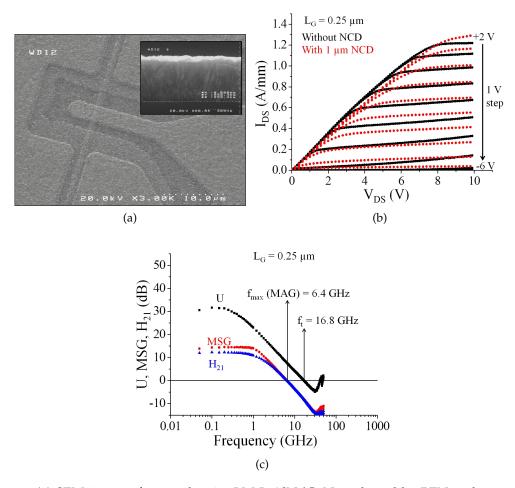

- (a) SEM image of 10 nm barrier LM-InAlN/GaN nucleated by BEN and grown with 1 µm NCD layer. (b) The DC characteristics of the device are largely identical to the characteristics before growth and (c) the cut-off frequencies are in the GHz regime but still limited by parasitics (measurements performed in EBS, Ulm University).

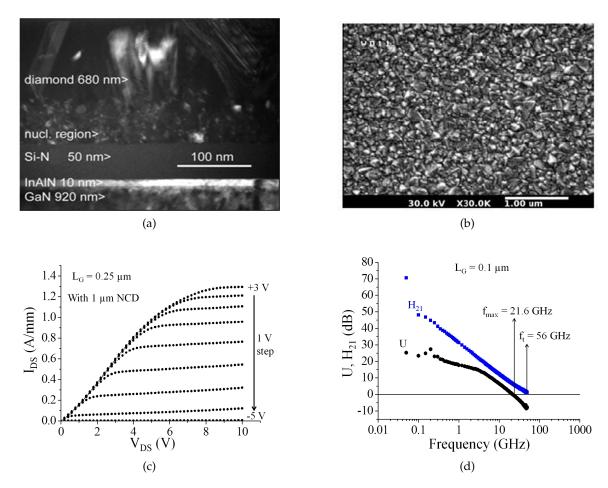

- Figure 43 (a) TEM cross section (performed by MFA) of NCD layer nucleated by nanoparticles seeding and grown by MP-CVD followed by HF-CVD growth on InAlN/GaN HEMT (b) SEM image of the 1 μm NCD overgrown HEMT (c) DC characteristics of the 0.25 μm x 50 μm HEMT and (d) the cut-off frequencies of the HEMTs with 0.1 μm long gates (measurements performed in EBS, Ulm University).

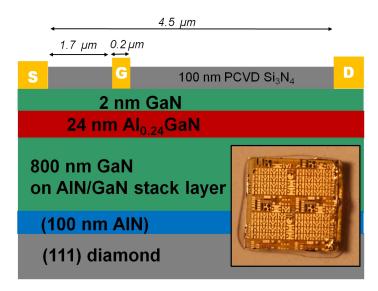

- Figure 44 Cross section of AlGaN/GaN on (001) Diamond grown by MBE in EPFL. The inset is a photo of the fabricated devices on the 3 mm x 3 mm Diamond substrate.

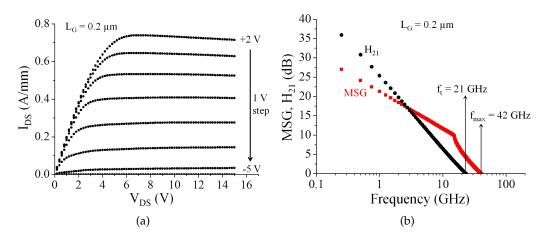

- Figure 45 (a) DC output characteristics of 0.2 mm x 50  $\mu$ m AlGaN/GaN HEMT on (001) Diamond. Complete pinch-off of the device at  $V_p = -5$  V was seen throughout the devices with no significant buffer leakage. (b) The HEMT cut-off frequencies (measurement performed by IEMN).. 74

Figure 46 (a) SEM image of 10 nm barrier LM-InAlN/GaN HEMT nucleated by BEN and overgrown with 3  $\mu$ m NCD film (b) Despite the harsh and long growth conditions the HEMT could be modulated but suffered from a parasitic leakage due to a degradation of the PCVD Si<sub>3</sub>N. An alternative to this passivation would be using (c) in-situ deposited Si<sub>3</sub>N<sub>4</sub> passivation or (d) a ALD-deposited Al<sub>2</sub>O<sub>3</sub>. Both passivation passed initial NCD growth tests. 78

#### List of Tables

| Table 1 | Basic material parameters of GaN, SiC and Diamond compared to Si and GaAs. After [9, 10, 11, 12, 13]                                                                                                                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2 | Time line summary of the state of the art LM-InAlN/GaN HEMT. It should be mentioned that all barriers used are thinner than 15 nm. *Performed in This work. **The Si <sub>3</sub> N <sub>4</sub> is combined with thermal oxidation. 33 |

| Table 3 | Lattice and thermal mismatch to substrates used for GaN growth.  After [9, 14]. 34                                                                                                                                                      |

| Table 4 | Material parameters used in the thermal simulations. 58                                                                                                                                                                                 |

# List of abbreviations

2DEG Two Dimensional Electron Gas

2DHG Two Dimensional Hole Gas

ALD Atomic Layer Deposition

AlGaN Aluminium Gallium Nitride

AllnN Aluminium Indium Nitride

AIN Aluminum Nitride

BEN Bias Enhanced Nucleation

FEM Finite Element Method

FET Field Effect Transistor

GaAs Gallium Arsenide

GaN Gallium Nitride

hcp Hexagonal-Closed-Packed

**HEMT High Electron Mobility Transistor**

HF-CVD Hot Filament Chemical Vapor Deposition

HR-XRD High Resolution X-Ray Diffraction

HfO<sub>2</sub> Hafnium Oxide

InGaN Indium Gallium Nitride

InN Indium Nitride

InP Indium Phosphide

ISFET Ion Sensitive Field Effect Transistor

LDMOS Laterally Diffused Metal-Oxide-Semiconductor

LED Light Emitting Diode

LM-InAIN Lattice-Matched Aluminium Indium Nitride

MBE Molecular Beam Epitaxy

MESFET Metal Semiconductor Field Effect Transistor

MISFET Metal Insulator Semiconductor Field Effect Transistor

MOCVD Metal Organic Chemical Vapour Deposition

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MOVPE Metal Organic Vapour Phase Epitaxy

MP-CVD Microwave Plasma Chemical Vapour Deposition

NCD Nanocrystalline Diamond

PAE Power Added Efficiency

PCVD Plasma Chemical Vapour Deposition

**RIE** Reactive Ion Etching

RTA Rapid Thermal Annealing

SiC Silicon Carbide

Si<sub>3</sub>N<sub>3</sub> Silicon Nitride

SiO<sub>2</sub> Silicon Oxide

TEM Transmission Electron Microscopy

TBR Thermal Boundary Resistance

ZrO<sub>2</sub> Zirconium Oxide

# List of symbols

$V_{Built-in}$  Built-in voltage

$\triangle E_c$  Conduction band offset

$a_0$  Length of the basal hexagon (at equilibrium) in a hexagonal lattice

c<sub>0</sub> Height of the hexagonal prism (at equilibrium) in a hexagonal lattice

C<sub>GD</sub> Gate-drain capacitance

*C*<sub>GS</sub> Gate-source capacitance

C<sub>barrier</sub> Barrier capacitance

$d_{barrier}$  Barrier thickness

$E_{\rm q}$  Bandgap

E<sub>Br</sub> Break down field

$E_{\rm F}$  Fermi level

*E*<sub>c</sub> Critical field

$f_{\text{max}}$  Maximum oscillation frequency

$f_{\rm t}$  Cutt-off frequency

g<sub>m</sub>. Transconductance

$I_{DS}$  Drian-source current

$J_T$  Tunniling current density

*L*<sub>G</sub> Gate length

P<sup>tot</sup> Net polarization

$P_{pz}$  Piezoelectric polarization

$P_{\rm sp}$  Spontaneous polarization

*q* Elementary charge

R<sub>C</sub> Contact resistance

R<sub>on</sub> On-resistance

$R_{sheet}$  Sheet resistance

*R*<sub>GS</sub> Gate-source resistance

T(E) Transmission probability

$u_0$  Anion-cation bond length (at equilibrium) along the c-axis of a hexagonal lattice

$V_{\rm Br}$  Break down voltage

$V_{\rm DS}$  Drain-sorce voltage

$V_{\rm GS}$  Gate-sorce voltage

V<sub>knee</sub> Knee voltage

$V_p$  pinch-off voltage

W<sub>G</sub> Gate width

N<sub>s</sub> Sheet charge density

μ Electron mobility

$v_e$  Electron velocity

$\phi_{SB}$  Contact potential

$\phi_s$  Surface potential

$\sigma_{pol,interface}$  Excess bound sheet charge density

$\sigma_P$  Polarization induced bound sheet charge density

$v_{sat}$  Saturation velocity

$\epsilon_r$  Dielectric constant

$\epsilon_i$  Strain in direction j

e<sub>ij</sub> Piezoelectric coefficients along the direction j

INTRODUCTION AND THESIS OUTLINE

Silicon semiconductor devices have replaced many conventional electrical parts in the past four decades in a wide spectrum of applications ranging from military applications to civil applications and consumer products. Although silicon is expected to remain as the dominant semiconductor of choice in many applications, wide band gap semiconductors (usually defined as having a band gap larger than 1.7 eV), like GaN, SiC, and Diamond are being investigated as a replacement for silicon technology in some applications, where silicon is reaching its physical limit. These limits are imposed by an increased market need for electronics that are faster, more thermally stable, more robust and more miniaturized and compact, in an era that witnesses the wide spread application of wireless communications like in radars and base stations, and energy conversion like lightening, and optical communication, and information transmission, while at the same time trying to reduce the overall energy consumption and losses.

These needs can be met using wide bandgap semiconductors, the properties of which are summarized in table 1 and compared to Si and GaAs. The difference in the crystal structure (Diamond-cubic for Si and single crystal Diamond, hexagonal Wurtzite (hcp) or zinc blind for GaN and SiC, and zinc blind for GaAs) and the composition gives rise to different widths of the bandgap, dielectric constants, electron and hole mobilities and saturation velocities and thus fundamentally different electronic properties. But in general, the properties listed address the fundamental needs mentioned earlier, for example, the wide bandgap of GaN, SiC and Diamond allows for a higher break down voltage ( $V_{\rm Br}$ ) enabling the application of higher supply voltages, which makes these materials attractive for high power applications [15]. Moreover, the larger bandgap makes these materials less susceptible for thermal noise (if the material can be grown with a low trap concentration) and allows operation at higher temperatures [16]. For high frequency applications the product of mobility and saturation velocity is essential. This makes InP and GaAs prime candidates for high frequency applications but limited to low voltage applications due to their relatively low breakdown field. In addition, the higher thermal conductivities of GaN, SiC and Diamond allow better thermal management for high power applications, where device self-heating is coupled with output power. Thus GaN, SiC and Diamond seem to provide the best compromise for achieving high power/high frequency operation, power switching and high temperature applications.

Based on the arguments above, it is clear that Diamond (in its single crystal form) is expected to outperform the other materials. However, the maturity of the technology for the relevant semiconductor has to be taken into account. For example, silicon is still the dominant semiconductor of choice for electronics due to its long research history, the maturity of its material growth and fabrication technology, in addition to its ability to form a stable native oxide. Diamond has been intensively studied and is being used in many

|           | $E_{g}$ | μ           | $v_{sat}$             | $E_{\mathrm{Br}}$ | К       | $\varepsilon_{\rm r}$ |

|-----------|---------|-------------|-----------------------|-------------------|---------|-----------------------|

|           | [eV]    | $[cm^2/Vs]$ | $[10^7 \text{ cm/s}]$ | [MV/cm]           | [W/cmK] |                       |

| Si        | 1.12    | 1400        | 1                     | 0.3               | 1.3     | 11.9                  |

| GaAs      | 1.42    | 8500        | 1.2                   | 0.55              | 0.55    | 12.9                  |

| GaN (hcp) | 3.4     | 1200        | 1.3                   | 5                 | 1.3     | 9.5                   |

| 6H-SiC    | 3       | 400         | 2                     | 3                 | 4.9     | 9.7                   |

| Diamond   | 5.43    | 4500        | 1.6                   | 1                 | 22      | 5.7                   |

Table 1: Basic material parameters of GaN, SiC and Diamond compared to Si and GaAs. After [9, 10, 11, 12, 13]

non-electronic applications in its polycrystalline form as hard coating material but the use of Diamond in electronic applications is limited by the lack of a large area substrate. The difficulty to grow single crystalline Diamond on foreign substrates like silicon and the difficulty of doping seem to have slowed down its advance in the electronics industry[17]. SiC faces a similar limitation due to its high wafer cost compared to GaN. GaN on the other hand has reached a fairly advanced maturity in terms of material growth technology and understanding the atomic surface behavior [18] pushed by the intensive research to use the material as an efficient light emitting source. The main factor driving the wide use of GaN in optical application is the ability to grow ternary and quaternary GaN based alloys, referred to as the III-nitride group, thus enabling the engineering of the bandgaps and quantum wells and thus varying the wavelength of the emitted light, from blue, as first demonstrated in an LED by Nakamura et. al. in 1994 [19], to even ultra-violet ranges [20, 21].

Along with the mastery of growth, III-nitride alloys of GaN, AlN, and InN (in Wurtzite structure) are attractive for electronic applications due to the unique property of obtaining large polarization fields, which promotes the ability to form heterostructures with large carrier densities at the interface as a two dimensional electron gas (2DEG) with high mobilities, as will be discussed in section 2.1. GaN based heterostructures, like the traditionally used AlGaN/GaN, having a high breakdown voltage and a large carrier density with high mobility, made it firstly ideal for high frequency/high power applications, as HEMT devices, the basics of which will be described in section 2.3.2, and now also in power switching and high temperature electronics. The ultimate performance of such heterostructures will be gained when both ends of the III-nitride alloys are used, namely employing an AlN barrier on a GaN buffer (AlN/GaN HEMT structure), the main reason being that this heterostructure has the highest polarization induced carrier density at the interface. This will be discussed in details in section 2.1. Starting from GaN or InN this can be achieved by increasing the Al-content, thus following either an Al-GaN line or Al-InN line. Along the latter, one encounters the AlInN alloy with 83% Al-content, which is lattice matched to GaN. This material is the focus of the work presented here and will be denoted LM-InAlN throughout this work.

Many demonstrations of such GaN based HEMTs (AlGaN/GaN, AlInN/GaN and AlN/GaN) have already shown the capability to exceed what is achieved by Si technology [22] in terms of output power and operation frequency, particularly beyond what is reached by Silicon LDMOS (Laterally Diffused Metal-Oxide-Semiconductor) power amplifiers and above 2 GHz. High output power densities at operation frequencies above 1 GHz [23, 24, 25], up to 40 W/mm [26] have been demonstrated. Moreover, the on-resistance  $(R_{on})$ - breakdown voltage product is approaching the physical limit of SiC [27, 28, 29, 30, 31] proving the suitability of GaN HEMTs for power switching applications. High current gain cut-off frequency and maximum oscillation frequency ( $f_t$  and  $f_{max}$ ) in the GHz regime can be routinely achieved due to a high channel mobility and high transconductance and the relatively high device aspect ratios that can be achieved. A recent example is a LM-InAlN/GaN HEMT with  $f_t$  of 300 GHz [32], so far the highest reported  $f_t$  for a GaN HEMT. Based on the high polarization fields and high breakdown fields in GaN heterostructures a natural super-junction breakdown voltage of 9000 V was demonstrated [33]. In addition, these heterostructures are expected to operate more reliably than Si in harsh environment like elevated temperatures above 200 °C, or in chemical sensing environments that are aggressive to Si.

But despite this impressive performance, stability issues are not usually reported and GaN based HEMTs still did not establish their presence commercially due to stability and reliability issues [25, 34, 35] intrinsic to the HEMT structure. Mainly these are the surface charge stability issues like current collapse (discussed in section 2.5.1) and the device self-heating at high output powers (discussed in section 2.5.2). Due to their intrinsic nature, these limitations can not be completely eliminated but rather the onset of their effects on the device can be pushed further beyond the targeted operating range. To achieve this, several technological solutions are proposed. For example, using a cap layer for surface passivation or to growing the HEMT device on highly thermally conductive substrates like SiC [11], and lately by direct growth on Diamond substrates [36] as will be shown in this work, or via hybrid integration by wafer bonding to Diamond substrates [37, 38], for a better thermal management of the device. However, to apply more advanced and unconventional solutions, like what will be presented in this work, a proper choice of the heterostructure material is essential.

The heart of this work is the development of a processing technology for overgrowing high performance LM-InAlN/GaN HEMTs with nanocrystalline Diamond films, for heat spreading purposes. The work presented here has been part of a larger effort in the European community (through the EU projects Ultra GaN (http://www.ultragan.eu/) and Morgan (http://www.morganproject.eu/)) to investigate the potential of this heterostructure. The work involved a high level of cooperation with the growth teams, and a constant feedback with the characterization teams, in order to optimize the heterostructure for subsequent Diamond growth. The heterostructure growth was performed by several groups, namely, Ecole Polytechnique Federal de Laussan in Switzerland (EPFL), Alcatel-Thales III-V labs in France (III-V Labs), AIXTRON in Germany and FORTH in Greece. The small signal and large signal characterization was performed in the Institute D'electronique, de Microelectronique et de Nanotechnologie (IEMN) in France. Material

4

analysis using high resolution TEM was conducted partly in the Materialwissenschaftliche Elektronenmikroskopie Department at Ulm University (Z. E. Elektronenmikroskopie) and partly in the Research Institute for Technical Physics and Materials Science (MFA) in the Hungarian Academy of Sciences in Budapest. The thermal characterization of the grown nanocrystalline Diamond films was conducted by the University of Glasgow (GLG).

The other side of the technology, namely the optimization of the overgrown nanocrystalline Diamond films for heat spreading purposes, was conducted in the Institute of Electron Devices and Circuits (EBS) in Ulm University by M. Dipalo and S. Rossi. The work presented here is the result of a common optimization of both technologies.

The application of the Diamond overgrowth technology is allowed by the exceptional properties of the heterostructure. The LM-InAlN/GaN with 83% Al-content is very close to the sought-after AlN/GaN heterostructure, which is difficult to grow due to the high stress between the AlN barrier and the GaN buffer. In the LM-InAlN/GaN 2DEG densities up to  $2.6 \times 10^{13} \text{ cm}^{-2}$  can be achieved, enabling high power densities at moderately low drain voltages. However, the most attractive feature of this heterostructure is its ceramic-like stability, first demonstrated in 2006 by short time HEMT operation at 1000 °C in vacuum [39]. This high thermal stability is invested in this work in applying novel solutions for the surface passivation problem (or current collapse) using thermal oxidation, and thermal management for high power applications by combining monolithically integrated polycrystalline Diamond heat spreader by direct growth on top of a completely prefabricated HEMT. Both processes are performed at temperatures above 700 °C, not suitable for the other heterostructures, like the commonly used AlGaN/GaN, and require optimization of several aspects of the HEMT design, like the barrier thickness, the metallization schemes used and the HEMT passivation. The thesis outline will thus follow the rout taken to optimize, apply and characterize these technologies.

Firstly, an introduction to the III-nitride heterostructure, and specifically of GaN based HEMTs, will be presented to illustrate the role of polarization charges and surface counter charges in the formation of the 2DEG. This is followed by outlining the basic model of GaN HEMTs. These sections will serve as a guide to discuss the technological limitations of GaN HEMTs (device scaling properties), as well as intrinsic limitations (current collapse and self heating). After that, an argument will be presented of why the LM-InAlN/GaN HEMT can be a very good compromise in terms of high performance and high stability, even when using a simple planar device fabrication technology as in this work. After describing the fabrication technology used here and identifying the basic HEMT properties, through modeling and scaling experiments, experimental evidence of the high thermal stability of this heterostructure is presented together with a first insight into failure mechanisms for high temperature storage or operation.

As mentioned before, the HEMT high thermal stability will be utilized in applying a thermal oxidation/nitride passivation scheme efficient to suppress current collapse effects. After characterization and optimization of the oxidation process the passivation scheme was applied to a power HEMT. This enabled using the full current density of the device (2.4 A/mm as characterized by pulsed DC conditions) for power operation at 4 GHz, yielding a record output power density of 11.6 W/mm at relatively moderate drain voltage of 20 V.

This passivation scheme also proved to be crucial in stabilizing the HEMT surface, specially around the gate region, and thus allowed high continuous large signal operation at high temperatures above 500 °C and up to 1000 °C in vacuum, never achieved before for any other semiconductor. This opens new possibilities for electronics to extend its presence to harsher environments, which could not be accessed before.

This optimization also paved the way to applying an advanced heat spreader configuration, using the high thermal stability of polycrystalline Diamond deposited on top of a fully fabricated HEMT. The harsh polycrystalline Diamond growth conditions are difficult to be applied on other heterostructures, even bare and before the fabrication of the HEMT, without compromising the heterostructure properties. These growth conditions will be described after presenting a theoretical evaluation of the advantages of using this configuration. Finally the optimized technological steps leading to the first demonstration of a Diamond coated HEMT operating in the GHz regime will be described. The technology developed also served as a base for a Diamond-GaN ISFET for harsh chemical applications, owing to the inertness of Diamond, as presented in [40, 41, 42].

Together with the demonstration of the world premier high frequency GaN HEMT directly grown on single crystalline Diamond, also demonstrated in this work in cooperation with EPFL, both technologies present an ultimate solution to heat management issues in high power HEMTs if combined.

Finally an outlook concerning possible alternatives for passivation and fabrication technology, which enables an even higher HEMT thermal stability (required for example to grow thicker Diamond films on top of the HEMT), are presented followed by a summary and conclusion of the work.

In this chapter the advantages and challenges of GaN based HEMTs will be discussed. The advantages of using GaN HEMTs for high power and high frequency applications originate first from the basic physical properties it possesses by belonging to the wide bandgap semiconductors class. The III-N group in particular has the unique property of obtaining large polarization fields due to its crystal structure as will be discussed in section 2.1, which promotes the ability to form heterostructures with large carrier densities as will be discussed in section 2.2. GaN based heterostructures, having a high breakdown voltage and a large carrier density with high mobility, makes them ideal for high frequency/high power applications, power switching applications and high temperature applications, as HEMT devices, the basics of which will be described in section 2.3.2. However, the devices performance is limited below the ideal expectations imposed by the actual material properties. Section 2.4 will discuss these limitations briefly as a preliminary for the solutions presented in this work.

# 2.1 III-N group electronics

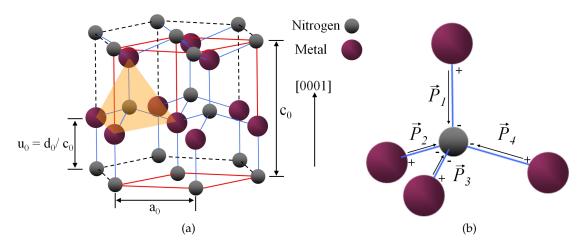

The III-nitrides material group GaN, AlN and InN can crystallize in the Wurtzite crystal structure or zincblende crystal structure. But in contrast to cubic III-V semiconductors like GaAs and InP, which retain a thermodynamically stable zincblende structure, III-nitrides retain the thermodynamically stable Wurtzite structure under ambient conditions. Fig. 1a shows a schematic of the hexagonal Wurtzite lattice of III-nitrides defined by the lattice parameters  $a_0$  (the length of the basal hexagon),  $c_0$  (the height of the hexagonal prism) and  $u_0$  (the anion-cation bond length along the c-axis) where the subscript "o" indicates values at equilibrium. The ideal Wurtzite crystal is composed of two hexagonal lattices shifted ideally by a ratio of  $c_0/a_0 = (8/3)1/2 = 1.633$  and  $u_0 = 3/8$ . This will result in symmetrical tetrahedrons (each atom is bonded with four nearest neighbors atoms) of equal side lengths and equal angles (Fig. 1b). This unit cell lacks the inversion symmetry (non-centrosymmetric) which means that each plane is composed of the same atom type (cation or metal) while the next plane is composed of nitrogen atoms (anions) and gives rise to polar crystal surfaces, which has either the metal face consisting of group-III elements (Ga, Al or In) polarity designated (0001) or nitrogen face polarity designated (0001).

In both cases of polarity the small atomic radius and the high electronegativity of the nitrogen atom shifts the negative charge centroid towards it and away from the metal thus creating a local polarization. This occurs along the c-axis bond and the basal plane bonds. If the crystal structure has inversion symmetry and an ideal  $c_0/a_0$  ratio of 1.633 (called the ideality factor) the resultant polarization vectors will compensate each other. The III-nitrides with its non-centrosymmetry however deviate from this ideality factor,

Figure 1: A schematic of (a) the ideal hexagonal lattice of III-nitride and (b) the tetrahedron shaded in (a) with the polarization vectors induced by the difference in electronegativity of the constituent nitrogen and metal atoms.

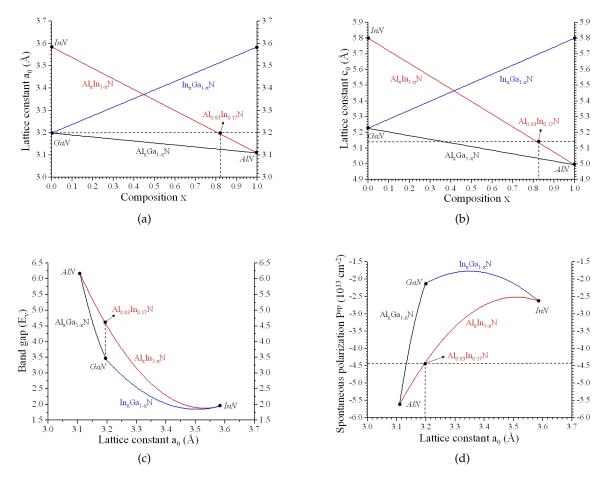

with GaN being the closest by a  $c_0/a_0$  ratio of 1.625, thus resulting in a net polarization along the c-axis. This polarization occurring at equilibrium is referred to as spontaneous polarization ( $P_{sp}$ ). The degree of the strength of this polarization depends on the  $c_0/a_0$ ratio. Bernardini et al. presented a calculation of the spontaneous polarization in relation with the lattice parameter [43]. The different cation and ionic radii of Ga, Al and In gives rise to different  $a_0$  and  $c_0$  lattice parameters and thus different lattice parameter  $u_0$ , or a non ideal factor, resulting in binary alloys with different bandgaps and different spontaneous polarization values. The same is true for ternary alloys ( $In_xGaN_{1-x}$ ,  $In_xAlN_{1-x}$ , ...) and quaternary alloys ( $In_xAl_{1-x}GaN$ ) where the bandgap and spontaneous polarization is extrapolated through Vegard's law as a first approximation. Ambacher et al [1] presented an extensive review of the III-nitrides properties taking into account the bowing parameters. The empirical formulas presented in this review will be adopted here. Figures 2a and 2b show the relation between the composition of the alloy and its lattice parameters for a crystal with Ga face polarity. It is worth noting that an AlInN alloy with 83% Al content has the same lattice constant  $a_0$  as GaN, or in other words it is lattice matched to GaN in the plane of growth direction [0001]. This alloy (Al<sub>0.83</sub>In<sub>0.17</sub>N) will be referred to throughout the text with "LM-InAlN". The variation in the lattice parameters leads to a variation in the bandgap (Fig. 2c) and the spontaneous polarization values (Fig. 2d). The negative sign of polarization indicates that the polarization vector points towards the substrate, from Ga atom to N atom, opposite to the [0001] direction. It is to be noted that all III-nitride alloys have a negative spontaneous polarization.

The change in the lattice parameters can also occur without changing the composition of the alloy but by exerting external mechanical forces in form of strain and hence altering

Figure 2: (a) Lattice constant  $a_0$  and (b)  $c_0$  in dependence of alloy composition. A LM-InAlN alloy with 83% Al content has the same lattice constant  $a_0$  as GaN. (c) Alloy bandgap in dependence of the lattice constant  $a_0$  and (d) the spontaneous polarization in dependence of  $a_0$ . After [1].

the net polarization by adding the piezoelectric polarization vector ( $P_{pz}$ ).  $P_{pz}$  is described by Hook's law as in equation 2.1:

$$P_{i}^{pz} = \sum_{j} e_{ij} \epsilon_{ij} \tag{2.1}$$

Where  $e_{ij}$  are the piezoelectric coefficients and  $\epsilon_j$  is the strain in direction j. Neglecting the shear strain and employing the non zero piezoelectric coefficients ( $e_{33}$ ,  $e_{31}$  and  $e_{15}$ ) the piezoelectric polarization along the c-axis is then described by equation 2.2:

$$P_3^{pz} = e_{33}\epsilon_{33} + e_{31}(\epsilon_1 + \epsilon_3) \tag{2.2}$$

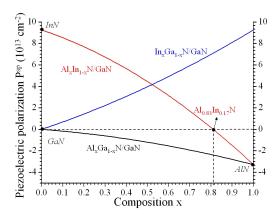

Figure 3: Theoretical values of the piezoelectric polarization ( $P^{pz}$ ) for III-N alloys grown on relaxed GaN buffer.

Where  $\epsilon_3 = (c - c_0)/c_0$  is the strain along the c-axis and  $\epsilon_1 = \epsilon_2 = (\alpha - \alpha_0)/\alpha_0$ , with  $a_0$  the lattice constant of the relaxed alloy and a the lattice constant of the strained heteroepitaxially grown alloy. The strain along the c-axis is connected to the strain along the basal plane by the elastic constants  $c_{13}$  and  $c_{33}$  through equation 2.3:

$$\epsilon_3 = -2\frac{c_{13}}{c_{33}}\epsilon_1\tag{2.3}$$

Thus the piezoelectric polarization along the c-axis can be written in terms of the strain in the basal plane only as equation 2.4:

$$P_3^{pz} = 2\frac{a - a_0}{a_0} \left( e_{31} - e_{33} \frac{c_{13}}{c_{33}} \right) \tag{2.4}$$

Since  $e_{31}$  is always negative and  $e_{33}$ ,  $e_{13}$  and  $e_{33}$  are always positive [43] then for a tensile stress ( $a > a_0$ )  $P^{pz}$  is always negative and for compressive stress ( $a < a_0$ )  $P^{pz}$  is always positive. The theoretical calculations of the piezoelectric polarization for III-N alloys grown on relaxed GaN buffer is shown in Fig. 3. The piezoelectric polarization of LM-InAlN on GaN is implicitly zero.

The net polarization ( $P^{\text{tot}}$ ) in an alloy is then the summation of the spontaneous polarization and the piezoelectric polarization as in equation 2.5:

$$P^{\text{tot}} = P^{sp} + P^{pz} \tag{2.5}$$

## 2.2 Gan based heterostructures for HEMT applications

The advances made in the growth methods and techniques of III-nitride alloys allowed an advanced stage in engineering materials with parameters like bandgap, polarization,

dielectric constant, thermal conductivity, etc..., tailored for specific applications. However, the ability to grow heterostructures of III-nitride based materials remains a corner stone for electronic applications, specially power electronics. The built-in spontaneous and piezoelectric fields induced by the difference in the lattice constants between the host substrate and the grown alloy on top, should by theory give rise to high 2-Dimensional Electron (or hole) Gas (2DEG or 2DHG) at the heterostructure interface, without the need of external doping, and thus high lateral breakdown field.

### 2.2.1 The formation of 2DEG

To explain the formation of a 2DEG in III-nitride HEMTs the most commonly used GaN based heterostructures will be used as an example. In these examples a III-nitride alloy (usually called a *barrier*) is grown pseudomorphically on top of a relaxed GaN buffer. Both layers are assumed to be undoped and grown with Ga-face polarity. Variations on this configuration (different buffer, N-face polarity) will however follow the general rules presented here and details can be found in [1, 44, 45, 46].

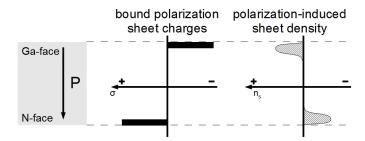

The gradient of  $P^{\text{tot}}$  in GaN or its alloys (see Fig. 4) leads to a polarization induced bound sheet charge density ( $\sigma_P$ ) to preserve charge neutrality given by:

$$\sigma_{P} = -\nabla . \overrightarrow{P} \tag{2.6}$$

Holes would then accumulate at the Ga-face and electrons at the N-face. This is illustrated in Fig. 4.

Figure 4: Schematic of the formation of polarization induced bound sheet charge density in polar GaN. The source of these charges is not considered at the moment.

Similarly if two III-nitride materials are grown pseudomorphically then an abrupt change in the polarization would occur at the interface (assuming a smooth interface) leading to an excess bound sheet charge density at the interface ( $\sigma_{pol,interface}$ ) as depicted Fig. 5 and given by equation 2.7 (represented here for an alloy grown on relaxed GaN buffer):

$$\sigma_{\text{pol,interface}} = P_{\text{GaN}}^{\text{tot}} - P_{\text{alloy}}^{\text{tot}} \tag{2.7}$$

Figure 5: Schematic of polarization-induced interface charge in pseudomorphically grown heterostructure.

where  $P_{GaN,alloy}$  tot is given by equation 2.5.

To preserve charge neutrality, a counter charge of the same magnitude but with opposite sign should form at the interface either as a 2DEG in the buffer, if it has a smaller bandgap, or 2DHG in the barrier if the barrier has the smaller bandgap, and mirrored by a surface counter charge. The generated sheet charge density (N<sub>s</sub>) would then be the difference in the total polarization of both materials (also shown in Fig. 5). However, this represents the maximum N<sub>s</sub> that can be obtained for a heterostructure with ideal crystals, without taking into account the influence of the barrier thickness (i.e. the surface counter charge and consequently the surface potential), nor the source of the counter charges or the electrons in the channel. Before discussing these effects, it is worth looking at the expected generated N<sub>s</sub> for different barriers grown on GaN buffer (with Ga-face polarity). This is shown in Fig. 6, based on the calculations presented earlier in Figures 2d and 3 and Equations 2.5 and 2.7 after [1]. It is noted that the sheet charge density can be a 2DEG or 2DHG depending on the polarization discontinuity between the GaN buffer and the barrier. In addition, large N<sub>s</sub> values are theoretically predicted for (Al,In)<sub>x</sub>Ga<sub>1-x</sub>N alloys with increasing the Al-content, like in the case of LM-InAlN (approximately 2.7 × 10<sup>13</sup> cm<sup>-2</sup>)

Figure 6: Theoretical maximum 2DEG sheet charge density  $(N_s)$  for III-N alloys grown on relaxed GaN buffer with Ga-face polarity in dependence of alloy composition.

and AlN (approximately  $6.8 \times 10^{13}~\text{cm}^{-2}$ ) as a 2DEG moving in the GaN side of the interface with high mobility (as suggested in table 1) and thus high current values can be achieved.

Considering first the general case of a GaN HEMT band diagram as sketched in Fig. 7, an analytical expression of  $N_s$  [47] can be written as:

$$N_{s} = \sigma_{\text{pol,interface}} - \left[ \frac{\varepsilon_{\text{barrier}}}{d_{\text{barrier}} \cdot q} \left( \phi_{s} + E_{F}(N_{s}) - \triangle E_{c_{\text{barrier}/GaN}} \right) \right]$$

(2.8)

where  $d_{barrier}$  is the barrier thickness, q the elementary charge,  $E_F(N_s)$  is the energy difference between the Fermi level and the conduction band at the bottom of the 2DEG,  $\triangle E_{c_{barrier}/GaN}$  is the conduction band offset between the barrier and the GaN buffer and  $\phi_s$  is the surface potential. The energies are in Volts. The charge concentration and polarization discontinuity are in cm<sup>-2</sup>. It should be noted that  $\phi_s$  is a result of the surface counter charge (relative to  $N_s$ ) thus controlling this charge is a key factor in optimizing the HEMT design, as will be discussed in section 2.3.1.

For a free surface (no gate contact and gate modulation), this apparent  $N_s$  (in the presence of a surface potential  $\varphi_s$ ) is generally less than the polarization discontinuity. In this case,  $N_s$  as a function of the barrier thickness is dependent mainly on the state of  $\varphi_s$ , which in turn can be either unpinned or pinned.

If  $\phi_s$  is unpinned as depicted in Fig. 7,  $N_s$  be independent of  $d_{\text{barrier}}$ . Thus  $N_s$  will be constant and equal to  $\sigma_{\text{pol,interface}}$  (representing the maximum theoretical value), if the voltage drop across the barrier is zero (flat barrier conduction band) as sketched in Fig. 9a. This however will occur only if the surface counter charge is eliminated. On the other hand, taking into consideration the effect of the surface counter charge (and thus  $\phi_s$ ),  $N_s$  will be constant and equal to equation 2.8, provided that the value of  $\phi_s$  is known for one barrier thickness (see Fig. 7).

On the other hand,  $\phi_s$  can be pinned and thus  $N_s$  becomes a function of the barrier thickness. In this case the maximum  $N_s$  can not be reached but can only be approached for very thick barriers. This barrier scaling behavior is observed for most GaN HEMTs

Figure 7: Band diagram of a GaN based HEMT with barrier of thickness  $d_{barrier}$  and an unpinned surface potential  $\phi_s$ . In this case  $N_s$  is constant and independent of the barrier thickness, and its value is expressed by equation 2.8, provided that  $\phi_s$  is known. The case of a pinned surface potential is described in Fig. 9c

like AlGaN/GaN, AlN/GaN and as will be shown in this work, for LM-InAlN, and initially prevented the use of very thin barriers to achieve enhancement mode devices without sacrificing the  $N_s$ . For better understanding of this behavior and to introduce an explanation of the source of electrons and the counter charge and surface potential pinning, the next section will present theoretical modeling of this behavior using experimental data of LM-InAlN/GaN heterostructures used in this work.

## 2.3 Lattice matched InAlN/GaN heterostructure barrier scaling properties

In planar HEMT technology  $d_{barrier}$  is a main defining parameter of the HEMT performance, controlling the channel density if the surface potential is pinned as discussed above (see also Fig. 9c). There is no way to ascertain that the surface potential is pinned for a bare, unprocessed heterostructure. Most likely, surface potential pinning occurs once the heterostructure is subjected to the processing environment, which normally includes the use of bases or weak acids, contact deposition and annealing etc..., which alters the original surface states distribution, through, for example, weakly bonded oxygen-Ga(Al, In) species at the surface. However, this processing routine is necessary to measure  $N_s$  as a function of the barrier thickness through, for example, Hall measurement. A recent method introduced lately to directly measure the surface potential via Kelvin probe microscopy [48] becomes difficult if  $\phi_s$  is small. Eventually, fabricating the HEMT will include fabrication steps similar to to the ones used for conducting the Hall measurement, and thus modeling the barrier scaling properties using experimental Hall data will be the closest to the actual state of the surface of the fully fabricated HEMT.

## 2.3.1 Estimation of the heterostructure surface potential

In the case of LM-InAlN/GaN heterostructures used here, HEMTs with a total barrier thickness ranging from 3 nm to 33 nm including the 1 nm AlN spacer were grown and characterized (using HRXRD) by EPFL.  $N_S$  as a function of  $d_{barrier}$  was measured by Hall measurements.  $\phi_s$  of the as-grown heterostructures was estimated based on these data. The heterostructure is simulated using a 2D Poisson-Schrödinger equation solver, fitted to the experimental Hall data of  $N_S$  vs.  $d_{barrier}$  data. To account for the source of electrons in the channel and the surface counter charge effects, a surface donor model was used (as was also presented for the AlGaN/GaN case in [2]). In this model, surface states (surface donor-like traps), being either electronic or a chemical redox couple on the surface, act as a source of electrons for the channel. The surface potential is thus dominated by these surface state properties, namely their energy level and density. Static simulations were conducted using the commercial *Atlas* Poisson-Schrodinger equation solver from Silvaco [49]. An example of the simulation input file is shown in the appendix with comments on the simulation.

Figure 8: Experimental Hall  $N_s$  values vs.  $d_{barrier}$  compared to calculated values using different surface potential levels  $\phi_s$ . Also shown in the graph data for the AlGaN/GaN case from [2].

To calculate the band diagram and the resulting 2DEG of the LM-InAlN/GaN free surface with variable  $d_{barrier}$ , the bandgaps of the LM-InAlN and GaN, the conduction band offset and the polarization discontinuity have to be defined. Experimental Hall data for  $N_S$  vs.  $d_{barrier}$  were used for fitting. The simulations proceeded as the following:

The bandgaps of InAlN and GaN are set to 4.65 eV and 3.42 eV respectively [1]. The AlN spacer was not included in the simulations but its 1 nm thickness was added to the InAlN barrier thickness. Gonschorek et al. showed that the AlN spacer does not play a role in the formation of the 2DEG if it is below a certain thickness (2nm in this case), which

the 1 nm AlN is, and the main contributor to the 2DEG is the polarization discontinuity with the InAlN barrier, taking into account an effective conduction band offset  $\sim$  0.8 eV between the LM-InAlN and GaN [50, 51]. This value was thus used for these simulations. In addition only 100 nm of the GaN buffer below the InAlN interface is simulated, and a doping density of 1 x 10<sup>16</sup> cm  $^{-3}$  in both materials is added to simulate the unintentional doping reported by the growers.

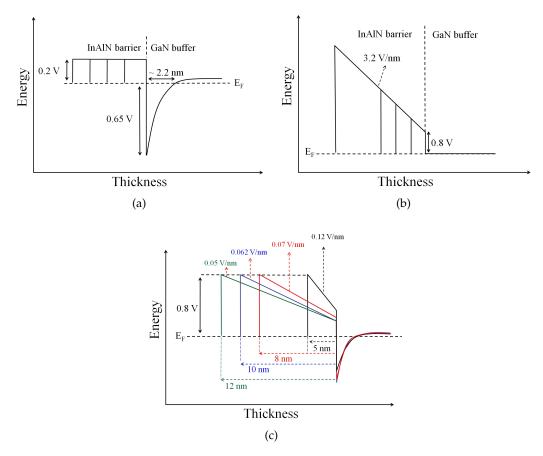

The value of the polarization discontinuity is set according to the experimental values shown in Fig. 8. As can be seen in the figure, N<sub>S</sub> increases up to a barrier thickness of 12 nm where it reaches a value of  $2.6 \times 10^{13} \text{ cm}^{-2}$  and remains constant up to 33 nm, the maximum barrier thickness which was grown. Since the maximum N<sub>s</sub> which can be reached in the heterostructure equals  $\sigma_{\text{pol,interface}}$ , this value of 2.6 x 10<sup>13</sup> cm<sup>-2</sup> is set as the polarization discontinuity, which is very close to the reported theoretically calculated value [1].  $\sigma_{pol,interface}$  can be set directly in the simulator but without a counter charge on the surface the simulator will assume a 2DEG density at the GaN side of the interface to preserve charge neutrality. This results in the calculated equilibrium band diagram shown in Fig. 9a where the 2DEG density is constant regardless of the barrier thickness, which is not the case found experimentally for a free surface and can be reached only with external gate bias, under the gate metal only, in the absence of any surface states. This case then also represents the HEMT at fully opened gate (barrier flat band condition). Thus a negative counter charge on the InAlN surface of the same magnitude should be added. In this case (shown in Fig. 9b) a constant voltage drop of 3.2 V/nm across the barrier (equivalent to  $\sigma_{polinterface}$ ) exists thus simulating the polarization field. However, without any source of electrons added so far, no  $N_S$  will form regardless of the barrier thickness. Even if all the dopants in the buffer and barrier (doping density of 1 x  $10^{16}$  cm  $^{-3}$  in both the InAlN and GaN layers are assumed as reported by the growers) are ionized and driven to the approximately 2.2 nm wide quantum well of the channel (assuming equilibrium as in Fig. 9a) they will amount only to less than 1 x  $10^{10}$  cm<sup>-2</sup> thus the doping can not be the source of electrons in the 2DEG.

The surface donor-like traps which are the source of electrons in this model are then added, not distinguishing the type of the traps, whether electronic or ionic (for example due to desorption of chemical species on the surface). The important parameters here are the traps energy level below the InAlN conduction band edge and the traps density. Here only discrete, single energy level traps are simulated. The traps on the surface could have a distribution of energies, if for example different species are adsorbed on the surface, but so far no evidence supporting this or information about the distribution width exists. Thus this case was not simulated. The trap energy was varied between fully ionized (o eV, being located at the conduction band edge of InAlN) and 1.6 eV below the conduction band edge (similar to the AlGaN case [2]) in steps of 0.2 eV. The barrier thickness was varied between 2 nm and 33 nm in steps of 0.3 nm. These configurations are limited by the mesh density allowed in the simulator.

For very thin barrier thickness (approximately less than 1 nm for the LM-InAlN/GaN as can be estimated from the Hall measurement data) the surface traps with energies larger than zero are below the Fermi level and are not ionized yet so no source of electrons for

Figure 9: Simulated LM-InAlN/GaN band diagrams for the case of (a) a fully undepleted surface resulting in a flat band in the barrier (b) fully depleted surface or no source of electrons to provide for the channel, resulting in a flat band in the buffer (c) with limited density of donor like surface traps, equal to the polarization discontinuity, at an energy of 0.8 eV below the conduction band.

the channel exists and no 2DEG is formed. The band diagram of this case is as shown in Fig. 9b. However, the constant electric field in the barrier will decrease with increasing barrier thickness and to keep the conduction band discontinuity constant, the relative position of the Fermi level will drop, or in other words the traps will become closer to the Fermi level, and at a certain thickness the traps will cross the Fermi level, and the ionized electrons are driven to the channel by the polarization field partially screening the polarization and leaving behind a positively charged trap.  $\phi_s$  will then be pinned to the trap energy level. For AlGaN/GaN the  $d_{barrier}$  where the channel starts to form is estimated to be around 3 nm [2]. It is very difficult to estimate this value for the InAlN case since even for barriers as thin as 2 nm the channel is already formed [52]. At such very thin barriers it is not clear whether the 1 nm AlN spacer starts to play a role in forming the channel. Quantum confinement effects have to be included in the simulations.

Since the trap energy is assumed to be a single level, all the traps will be ionized at once when the mentioned barrier thickness is reached, and  $\phi_s$  becomes pinned. Now, if the surface trap density is infinite,  $N_s$  will increase with increasing  $d_{barrier}$  (according to equation 2.8), up to the value when  $N_s$  equals  $\sigma_{pol,interface}$ . Until this point the surface potential will be pinned to the trap energy level. But increasing the thickness further will cause more electrons to move to the channel and thus more screening of the polarization occurs, until the equilibrium case shown in Fig. 9a is reached. However, beyond this point any further increase in the barrier thickness will lead to more traps to be ionized. But without the driving force of the polarization field,  $N_s$  will start to drop, a case comparable to the GaAs case. This was not observed in the experimental Hall data up to thicknesses of 33 nm.

To account for this behavior, an additional assumption, in contrast to standard models, is added by considering a limited trap density equal to the polarization charge discontinuity. This assumption will lead to a similar N<sub>s</sub> dependency as the case of infinite trap density, but with a lower increase rate for the same surface potential, up to the value when N<sub>s</sub> equals  $\sigma_{pol,interface}$ . Increasing the barrier thickness further than this point will decrease the voltage drop across the barrier but no increase in N<sub>s</sub> will occur since there are no more available donor traps, and N<sub>s</sub> will remain constant. The simulated data of N<sub>s</sub> vs.  $d_{\text{barrier}}$  superimposed on the experimental data are shown in Fig. 8 and compared to the Al<sub>0.34</sub>Ga<sub>0.66</sub>N /GaN case presented in [2]. A surface trap energy between 0.8 eV and 1.0 eV gives the best fit to the experimental data thus indicating a surface potential of the free surface which is significantly lower than the reported 1.6 eV for Al<sub>0.34</sub>Ga<sub>0.66</sub>N or 1.9 eV for AlN. As can be also seen in the figure, due to the lower surface potential and the higher polarization discontinuity the LM-InAlN/GaN heterostructure can provide higher N<sub>s</sub> values, compared to the AlGaN/GaN, even for very thin barriers, which enables high current HEMTs with high aspect ratio. The simulated band diagrams of barriers with 5 nm, 8 nm, 10 nm and 12 nm are shown in Fig. 9c.

Although this model, using the assumption of a limited trap density equal to the polarization discontinuity, can fit the observed experimental data, it does not specify the nature of the surface traps or why they are limited to the density of the polarization discontinuity. However, it maybe speculated that the trap formation needs a force, which must be internal, and linked to the polarization field. It is worth noting that this assumption was also used to explain the case of AlN/GaN barriers in [53] where the surface trap density was found to be very close to  $\sigma_{pol,interface}$  and a physical atomic arrangement model was suggested to explain this behavior.

So far, only a free surface case is considered in the simulations, where  $\phi_s$  can not be modulated. However,  $\phi_s$  can be modulated using a gate bias but this still does not apply to the free surface area between the contacts. And thus the direct implication of the surface potential pinning is the introduction of a current limiter. The depletion of  $N_s$  with decreasing the barrier thickness is in turn the natural way to obtain an enhancement mode HEMT, as will be shown in the next section. Excessive barrier downscaling will eventually cause the loss of  $N_s$ . Moreover, the surface traps responsible for the surface potential can not be eliminated, otherwise no channel will form. The surface depletion

can however be mitigated by using a heterostructure with an initially higher polarization discontinuity, thus despite the surface depletion, a fairly large N<sub>s</sub> value can still be obtained for relatively thinner barriers. This is done by increasing the Al content as (discussed in section 2.1) and the case presented here for the LM-InAlN/GaN (see Fig. 8) is certainly in that direction, aiming ultimately to use an AlN barrier. Another possibility is to have a heterostructure with an initially low surface potential, which also applies to the case of LM-InAlN/GaN compared to AlGaN/GaN. Thus the LM-InAlN barrier presents a good compromise between the surface potential, the polarization discontinuity and the barrier thickness that can be used. Other technological solutions can also be employed to mitigate the surface depletion effects, as will be presented later (see section 3.3.1). However, the existence of surface traps near the gate high field region in the HEMT also causes an intrinsic limitation to the HEMT power performance known as current collapse, which can not be eliminated but the onset of its effect relative to the operating voltage and frequency can be delayed, allowing higher operating voltages and frequencies. Before discussing the intrinsic HEMT limitations, and to better understand the barrier downscaling effect on the HEMT performance, it is necessary first to introduce the basic HEMT model, from which the HEMT technological and intrinsic limitations are discussed.

#### 2.3.2 Basic model of GaN HEMTs

The basic level analysis of the I-V characteristics of a HEMT (although basically a Metal Semiconductor Field Effect Transistor (MESFET)), maybe similar to a Metal-Oxide-Semiconductor FET (MOSFET) using a gradual channel approximation [54] taking into account two variations:

Figure 10: Schematic of HEMT band diagram under the gate (a) in case of no applied gate voltage  $\phi_s$  equals the contact potential  $\phi_{SB}$ , and (b)  $\phi_s$  is controlled by the gate voltage, as shown here for the case of a pinched-off channel.

• The capacitively coupled gate modulates the channel charge carriers by altering the built-in field in the barrier according to equation 2.8. However, under the gate  $\phi_s$

equals the contact potential  $\phi_{SB}$  (if no gate voltage is applied, see Fig. 10a), and is controlled by the gate voltage ( $V_q$ ), in which case  $\phi_s$  in equation 2.8 is written as:

$$\phi_{\rm S} = \phi_{\rm SB} - V_{\rm q} \tag{2.9}$$

In contrast to MOSFETs, the gate voltage can not be forward biased more than the barrier flat band condition shown in Fig. 9a without excessive leakage currents, specially if thin barriers are used, due to tunneling leakage currents.

• The pinch-off voltage  $(V_p)$  is defined for the case that  $N_s$  equals zero  $(V_p = V_g \mid)$  (see also Fig. 10b). This can be derived by replacing equation 2.9 in equation 2.8 and setting it to zero noting that  $E_F(N_s)$  equals zero at pinch-off, yielding:

$$V_{p} = V_{Built-in} - \frac{q \cdot d_{barrier} \sigma_{pol,interface}}{\varepsilon_{barrier}}$$

(2.10)

where  $V_{\text{Built-in}}$  is the built-in voltage, and is equal to  $\phi_{\text{SB}} - \frac{\triangle E_{c_{\text{barrier/GaN}}}}{q}$ , and is defined by the gate and heterostructure material parameters. Thus  $V_{\text{p}}$  for a given GaN HEMT can be changed by changing  $d_{\text{barrier}}$  as will be shown later in chapter 3 for LM-InAlN/GaN HEMT

Now the drain-source current ( $I_{DS}$ ) dependence on applied drain and gate voltages ( $V_{DS}$  and  $V_{GS}$ ) following the gradual channel approximation as in a MOSFET, can be written as:

$$I_{DS} = \mu C_{GS} \frac{W_G}{L_G} \left[ (V_{GS} - V_p) \cdot V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(2.11)

where  $C_{GS}$  is the gate-source capacitance, which equals the barrier capacitance ( $C_{barrier}$ ) in case of HEMT, and given by:

$$C_{GS} = \frac{\varepsilon_{barrier} W_G L_G}{d_{barrier}} \tag{2.12}$$

where  $W_G$  and  $L_G$  are the gate width and gate length respectively. Here, the term  $d_{barrier}$  neglects the 2DEG charge centroid and quantum capacitance, but needs to be corrected to the effective  $d_{barrier}$  in case of a very thin barrier.

The saturation drain current ( $I_{DSS}$ ) independent of  $V_D$  can be obtained by deriving equation 2.11 with respect to  $V_D$  and setting it to zero yielding:

$$I_{DSS} = \mu C_{GS} \frac{W_G}{L_G} (V_G - V_p)^2$$

(2.13)

and thus the transconductance  $(g_m)$  in the saturation region has no saturation velocity  $(v_{sat})$  limit and is a function of  $1/L_G$ , expressed by:

$$g_{m} = \frac{dI_{DSS}}{dV_{G}} = \mu C_{GS} \frac{W_{G}}{L_{G}} (V_{G} - V_{P})$$

(2.14)

However, these equations represent the long channel approximation and are valid only in the constant mobility regime where the electron velocity is below the saturation velocity ( $v < v_{sat} = \mu E_c$ ), where  $E_c$  is the critical field in the channel approximated by  $E_c = \frac{V_c}{L_G}$ . Due to the high mobility in GaN HEMTs, the saturation velocity can be reached even for small drain biases and hence the device will operate in the velocity saturation mode.  $I_{DSS}$  can be then written using a two-piece linear approximation [55, 56], ignoring hot electron overshoot and phonon scattering, as:

$$I_{DSS} \approx W_G C_{GS} \left( V_G - V_p \right) v_{sat} \tag{2.15}$$

and the transconductance is not a function of L<sub>G</sub> , and expressed by:

$$g_{\mathfrak{m}} = W_{\mathsf{G}} C_{\mathsf{GS}} v_{\mathsf{sat}} \tag{2.16}$$

thus the linear dependence of the transfer characteristics on  $V_G$ , in contrast to long-channel devices. Moreover, the cut-off frequencies of the device, neglecting extrinsic parameters, can be approximated by [54]:

$$f_{t} \approx \frac{g_{m}}{2\pi \left(C_{GS} + C_{GD}\right)} \tag{2.17}$$

and

$$f_{max} = \frac{g_m}{2\pi C_{GS} \sqrt{4(R_S + R_i + R_G)(g_d + g_m(\frac{C_{GD}}{C_{GS}}))}}$$

(2.18)

which for the case of small resistances can be reduced to:

$$f_{\text{max}} \approx \sqrt{\frac{f_{\text{t}}}{8\pi R_{\text{G}} C_{\text{GD}}}} \tag{2.19}$$

As in GaAs HEMTs, the natural way to increase the device cut-off frequencies is to aggressively scale down the device dimensions [57, 58] in addition to better channel confinement [59, 60, 61, 62]. As can be seen from equations 2.17 and 2.14 and neglecting the parasitic capacitances,  $f_t$  is an inverse function of  $L_G$ . Thus reducing  $L_G$  would yield higher  $f_t$ . However, this approach is limited by the short channel effects known for MOSHEMTs [54], where the fringing field capacitance can not be neglected anymore and the gradual channel approximation becomes invalid. In the case of GaN HEMTs, which reach saturation velocity at fields around 14 kV/s (and thus velocity overshoot also starts to play a role), the lateral field at the drain side makes the effective gate length asymmetric, and in total larger than the metallurgical gate length [63]. Thus to keep the internal field distribution the same, down scaling of the barrier is also required maintaining a certain aspect ratio  $L_G$  /  $d_{barrier}$ . In other words, getting the gate closer to the channel. This effect has been simulated for AlGaN/GaN HEMTs in [64] and observed experimentally in [65] where

a universal minimum aspect ratio of 15 was found to be a limit to avoid short channel effects, despite the multiple sample sources and barrier thicknesses. For power amplifiers, increased operation frequency has another limitation on the output power due to current collapse effect that will be discussed separately in section 2.5.1.

For linear operation of a class-A amplifier the output power ( $P_{out}$ ) can be estimated as [66]:

$$P_{out} = \frac{1}{8} I_{DS_{max}} \left( V_{DS_{|V_{Br}}} - V_{knee} \right)$$

(2.20)

Where  $V_{knee}$  is the knee voltage defined at the onset of current saturation and the factor  $\frac{1}{8}$  is due to undistorted sinusoidal current waveform of the class-A amplifier.

In the case of hard gate overdrive conditions (well into saturation and well into pinch-off) the microwave current waveform is that of a half wave rectifier, and the output power is given by [66, 67]: