## Thin Body InAIN/GaN HEMT Technology on Sapphire:

# Special Focus on High-Temperature and Electrochemical Applications

#### DISSERTATION

zur Erlangung des akademischen Grades eines

# **DOKTOR-INGENIEURS**

(Dr.-Ing.)

der Fakultät für Ingenieurwissenschaften, Informatik und Psychologie der Universität Ulm

von

# Patrick Herfurth aus Grafenrheinfeld

Gutachter: Prof. Dr.-Ing. Erhard Kohn

Prof. Dr. Ferdinand Scholz

Amtierende Dekanin: Prof. Dr. Tina Seufert

Ulm, 11. Mai 2015

# **Abstract**

This thesis is dedicated to the investigation of lattice-matched InAlN/GaN high electron-mobility transistors (HEMTs) for their application in high-temperature electronics and in electrochemical sensor systems. In this work, this refers to ambient temperatures as high as 600 °C or to the application in corrosive liquid media, like strong acidic (pH = 1) or alkaline (pH = 13) solutions. These two environments cannot be addressed with conventional silicon (Si) or gallium arsenide (GaAs) devices, but can be accessed using a more robust, more thermally stable material like the lattice-matched InAlN/GaN heterostructure. However, to further enhance performance and stability the proposed electrochemical sensor comprises an InAlN/GaN HEMT and, as the actual chemical sensor, an inert boron-doped diamond (BDD) electrode applicable for pH measurements or redox signal detection.

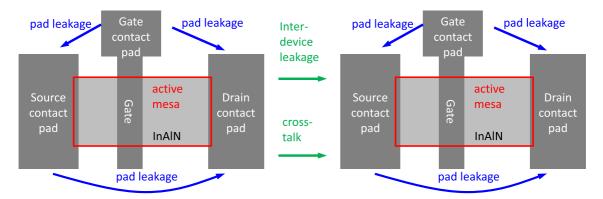

The integration with diamond and, apparently, the operation at elevated temperatures require a thermally stable HEMT. Additionally, both applications also require HEMTs exhibiting low overall device leakage characteristics. Therefore, in this work a new GaN-on-Sapphire (GOS) HEMT technology comparable to the Silicon-on-Insulator (SOI) technology was developed, capable of reducing parasitic leakage currents through the gate diode, through the buffer, and between separate contact pads (also between separate devices). Here, GOS implies the oxidation of the InAlN barrier, employment of a thin body (as thin as 50 nm GaN buffer + 50 nm AlN nucleation layer) material stack on sapphire, and the confinement of the active device mesa by dry-etching to small islands on the sapphire substrate.

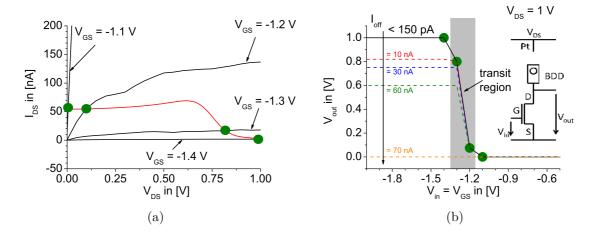

At room temperature, 0.25  $\mu$ m gate length devices prepared in this GOS technology exhibit an output current density of  $I_{DS}=0.4$  A/mm and a threshold voltage of  $V_{th}=-1.4$  V. The residual off-state current is 1 pA nearly independent of the gate width and the subthreshold swing is 73 mV/dec. The resulting current on/off ratio is larger than  $10^{10}$ , increased by 3 orders of magnitude compared to HEMTs prepared in a conventional device technology. Up to 600 °C such GOS HEMTs allow operation exploiting the full modulation range, i.e. from below threshold ( $V_{GS}=-2$  V) to fully open channel ( $V_{GS}=+2$  V). The corresponding device characteristics, e.g the maximum drain current, the transconductance, and the 1 MHz large signal output power, change only within less than 10 %. The residual off-current at 600 °C is approximatly  $I_{off}=10$  nA ( $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an, at this temperature, high current on/off ratio larger than  $I_{GS}=10$  nA ( $I_{GS}=10$  nA) resulting in an an at this temperature.

The electrochemical sensor system is analyzed with respect to two different measurement techniques yielding two essential combinations of the BDD electrode and the InAlN/GaN

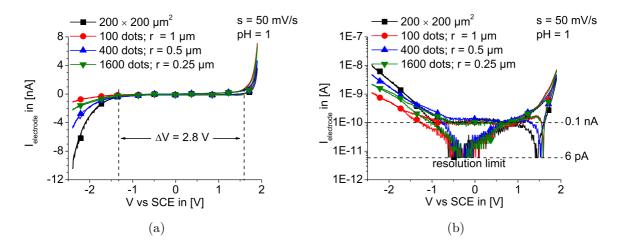

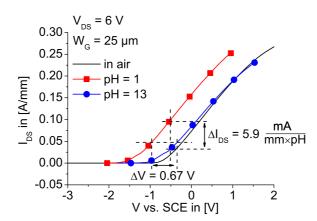

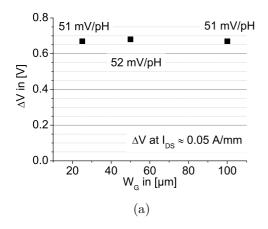

HEMT. Measurements of the pH are conducted in an extended gate ion-sensitive fieldeffect transistor (ISFET) configuration, where the electrode is connected to the HEMT gate. In the second measurement configuration the electrode is connected to the drain and the HEMT is used as switch to turn on or off redox reactions at the BDD electrode. To achieve optimal performance the two individual elements have to meet certain requirements, although in this case such requirements are mainly established by the electrode. Such boundary conditions are derived from individual BDD electrodes and are, e.g. the potential window of approximately 2.8 V, the background current of 0.1 nA, the resulting redox current, and the equivalent circuit of the BDD/electrolyte interface. Cyclic voltammetry, capacitance voltage measurements as well as electrochemical impedance spectroscopy were used to extract the relevant parameters and helped to derive design recommendations for the HEMT, in turn allowing a full exploitation of the HEMT saturation or subthreshold regime in the corresponding measurements. As ISFET the sensor system exhibits a high linearity over the whole pH scale with a pH sensitivity of 5 mA/mm per  $\Delta$ pH or 3.1 pH/dec in the subthreshold regime. As switch the HEMT is capable to completely turn on and off the redox reactions (in the nA regime), where the transfer region between on and off is less than 200 mV.

# **Contents**

| 1 | Intro                    | oduction and Motivation                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                  |

|---|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 2 | 2.1<br>2.2<br>2.3<br>2.4 | Crystal Structure of Nitride Semiconductors                                                                                                                                                                                                                                                                                                                                                                                   | 7<br>8<br>9<br>14<br>15                            |

| 3 | 3.1<br>3.2<br>3.3        | -Leakage Lattice-Matched InAIN/GaN HEMTs on Sapphire Sapphire as Substrate Material                                                                                                                                                                                                                                                                                                                                           | 21<br>22<br>26<br>28<br>30<br>33<br>38             |

| 4 | Thir 4.1 4.2 4.3 4.4     | Body InAIN/GaN MISHEMT: Device Operation up to 600 °C  2DEG Properties at High Temperatures                                                                                                                                                                                                                                                                                                                                   | 39<br>41<br>42<br>44<br>48                         |

| 5 | <b>Diar</b> 5.1 5.2 5.3  | mond Electrodes for the Integration with InAIN/GaN HEMTs  BDD Electrode Growth and Fabrication  Sample Preparation and Measurement Setup  BDD Electrodes for pH Identification  5.3.1 The BDD/Electrolyte Interface  5.3.2 Extraction of the pH Sensitivity  5.3.3 Potential Window and Background Current  5.3.4 Equivalent Circuit Model of the BDD/Electrolyte Interface  Detection of Redox Reactions with BDD Electrodes | 51<br>53<br>55<br>59<br>60<br>61<br>64<br>67<br>73 |

| 6 |                          | nbining InAIN/GaN HEMTs and BDD Electrodes for Electrochemical sing Applications InAIN/GaN HEMT and BDD Electrode Integration Technologies                                                                                                                                                                                                                                                                                    | <b>77</b> 79                                       |

<u>iv</u> Contents

|     | 6.2                      | Prerequisites for ISFET Measurements                                                                                                                                                                                 |                          |

|-----|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|     | 6.3<br>6.4               | 6.2.2 Matching the HEMT Input Circuit                                                                                                                                                                                | 94<br>96<br>97<br>101    |

| 7   |                          | ing Remarks                                                                                                                                                                                                          | 107                      |

|     | 7.1<br>7.2               | Summary and Conclusions                                                                                                                                                                                              | 107                      |

|     |                          | System                                                                                                                                                                                                               | 110                      |

| Bi  | bliogi                   | raphy                                                                                                                                                                                                                | 113                      |

| Α   | GaN                      | -On-Sapphire HEMT Technology Recipes                                                                                                                                                                                 | 127                      |

| В   | <b>Add</b><br>B.1<br>B.2 |                                                                                                                                                                                                                      |                          |

| C   | Add                      | itional Data for High-Temperature Operations                                                                                                                                                                         | 133                      |

| D   | D.1                      | Electrolytes and Electrochemical Potential Scale The BDD/Electrolyte Interface D.2.1 The Electrochemical Double-Layer D.2.2 The pH-Sensitivity of BDD Electrodes D.2.3 Charge Transfer Reactions Diffusion Processes | 137<br>137<br>138<br>139 |

| Ε   | Dete                     | ermining the Gate-Source Capacitance                                                                                                                                                                                 | 145                      |

| F   | Add                      | itional Data for Hybrid Measurement                                                                                                                                                                                  | 151                      |

| Lis | st of                    | Publications                                                                                                                                                                                                         | 153                      |

| Le  | bensl                    | auf                                                                                                                                                                                                                  | 157                      |

# **List of Figures**

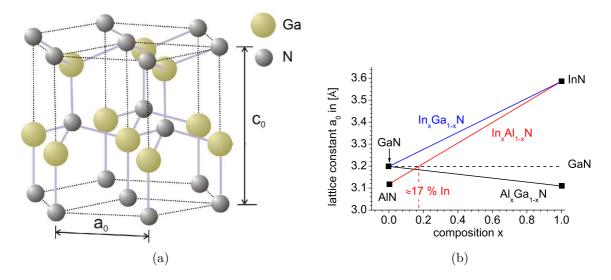

| 2.1  | (a) Hexagonal structure of the GaN crystal. (b) Change of lattice constant                        |     |

|------|---------------------------------------------------------------------------------------------------|-----|

|      | $a_0$ with alloy composition x                                                                    | 8   |

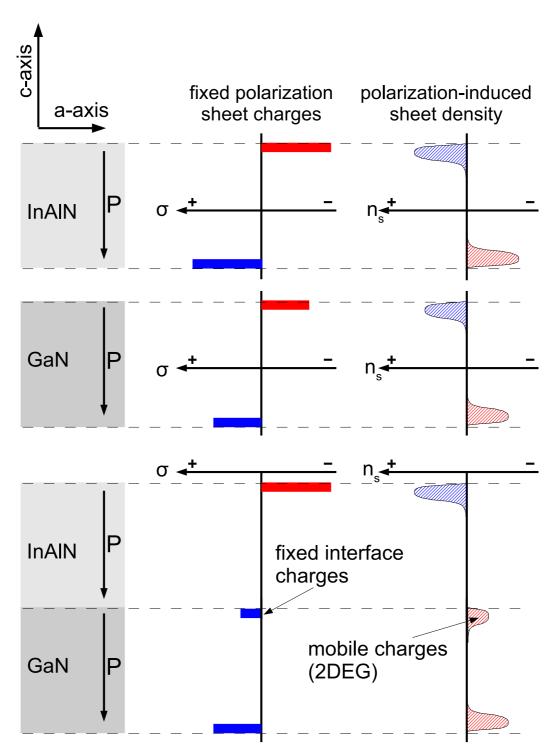

| 2.2  | Illustration of the development of free mobile charges at a heterointerface.                      | 10  |

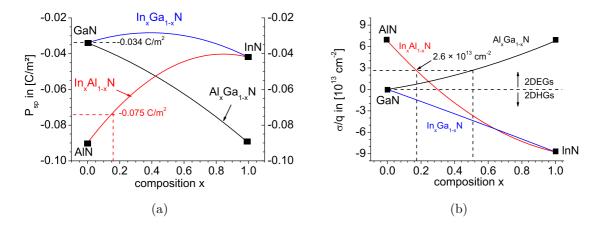

| 2.3  | (a) Change of spontaneous polarization with the composition of the ternary                        |     |

|      | alloy. (b) Calculated fixed interface charge for material on unstrained GaN.                      | 11  |

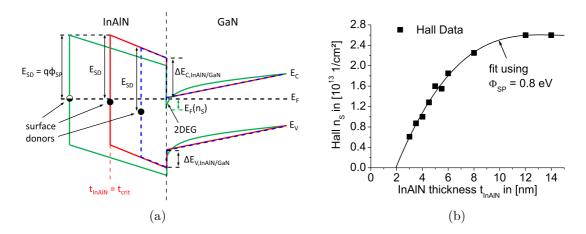

| 2.4  | (a) Schematic band diagram of the InAlN/GaN heterostructure. (b)                                  |     |

|      | Change of n <sub>S</sub> with InAlN thickness                                                     | 13  |

| 2.5  | (a) Schematic cross section of an InAlN/GaN HEMT and (b) correspond-                              |     |

|      | ing band diagram                                                                                  | 15  |

| 2.6  | (a) Sketch of gate diode with possible leakage paths. (b) Typical IV                              |     |

|      | characteristics of a gate diode                                                                   | 17  |

| 2.7  | (a) Cross section illustrating leakage through the buffer volume. (b)                             |     |

|      | Semilogarithmic transfer characteristics compared to gate leakage current.                        | 18  |

| 2.8  | (a) Schematic cross-section of a InAlN/GaN/AlN DHFET. (b) Schematic                               |     |

|      | band diagram of a DHFET with improved carrier confinement in the                                  |     |

|      | channel                                                                                           | 19  |

| 2.9  | Top view of a HEMT illustration leakage paths outside the device                                  | 20  |

| 0.1  |                                                                                                   | ~~  |

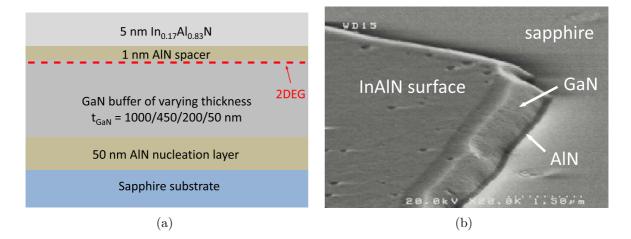

| 3.1  | (a) Sketch of the used layer structure. (b) SEM graph of mesa edge                                | 25  |

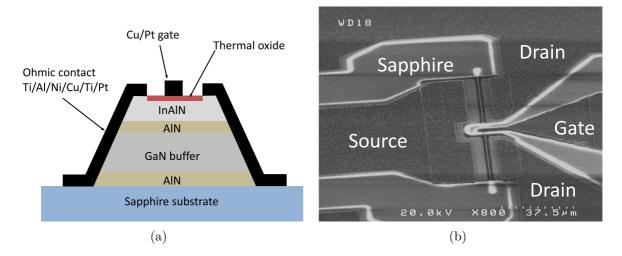

| 3.2  | (a) Cross-section of final MISHEMT. (b) SEM graph of fully fabricated                             | 00  |

| 0.0  | MISHEMT                                                                                           | 26  |

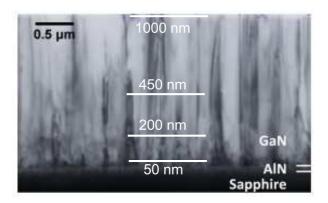

| 3.3  | TEM cross-section of an InAlN/GaN heterostructure                                                 | 27  |

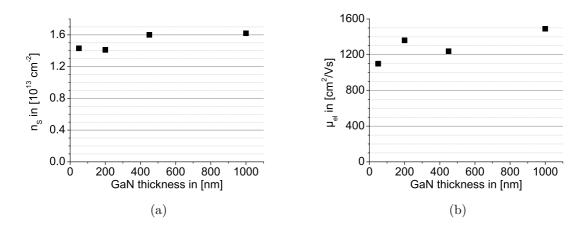

| 3.4  | Hall $n_S$ (a) and $\mu_{el}$ (b) vs. GaN buffer layer thickness                                  | 28  |

| 3.5  | Comparison of (a) $R_{\rm sh}$ and (b) $\rho_{\rm C}$ vs. GaN buffer layer thickness for the      | 00  |

| 0.0  | different GaN technologies                                                                        | 29  |

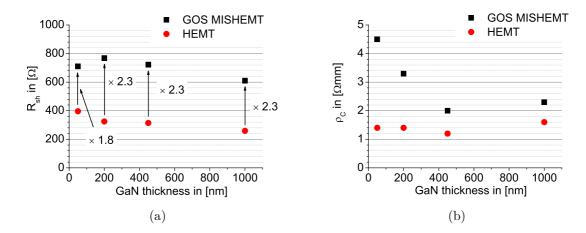

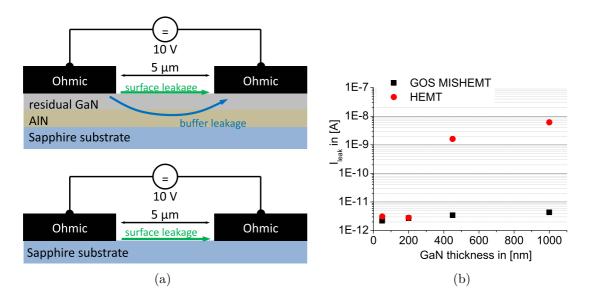

| 3.6  | Sketch of the isolation current test structure (a) and comparison of leakage                      | 200 |

| 2.7  | currents at 10 V for the two different technologies (b)                                           | 30  |

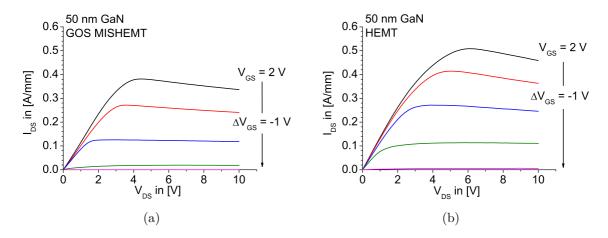

| 3.7  | Output characteristics of the 50 nm GaN system for (a) the GOS MISHEMT                            | 01  |

| 2.0  | and (b) the conventional HEMT                                                                     | 31  |

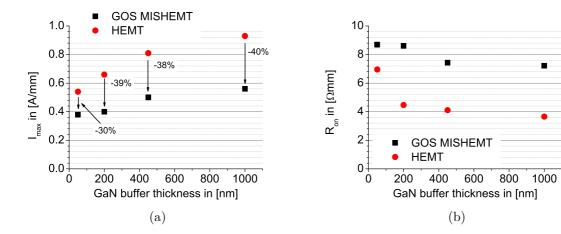

| 3.8  | Extracted (a) peak current density I <sub>max</sub> and (b) on-resistance R <sub>on</sub> vs. GaN | 20  |

| 2.0  | buffer thickness                                                                                  | 32  |

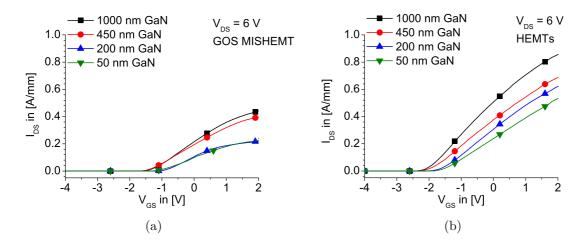

| 3.9  | Linear transfer characteristics at $V_{DS} = 6$ V of (a) the HISHEMTs and                         | 20  |

| 9 10 | (b) the HEMTs                                                                                     | 33  |

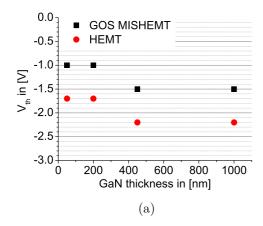

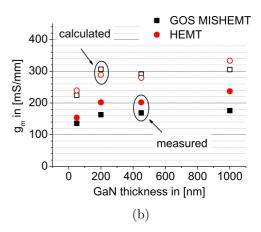

| 3.10 | Extracted threshold voltages $V_{th}$ (a) and maximum transconductance $g_m$                      | 2.4 |

|      | (b) vs. GaN buffer thickness                                                                      | 34  |

vi List of Figures

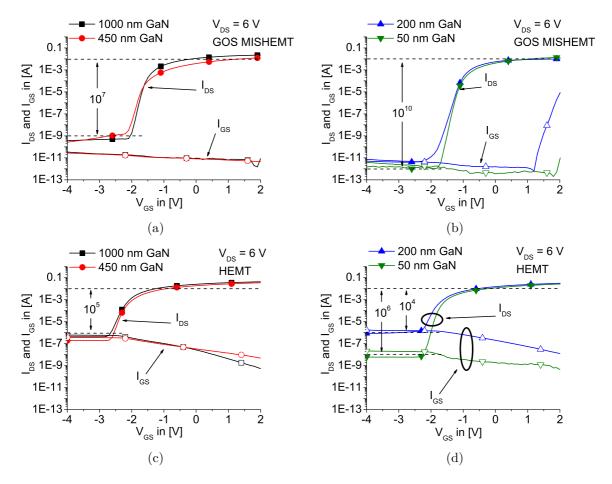

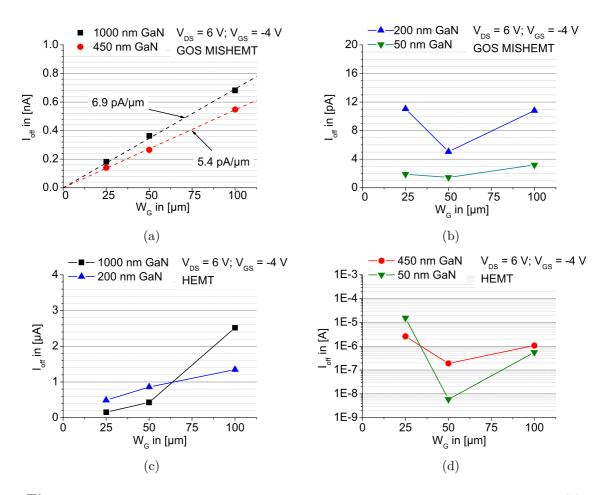

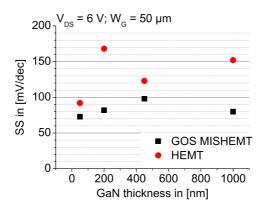

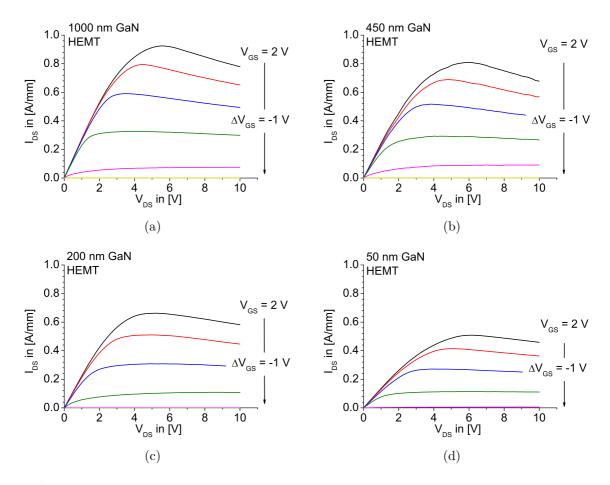

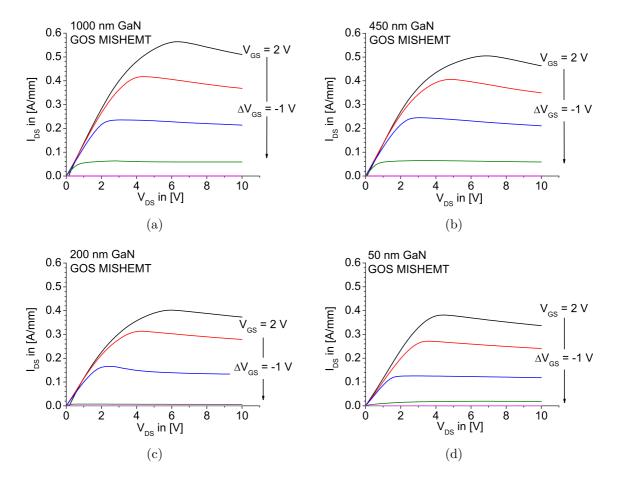

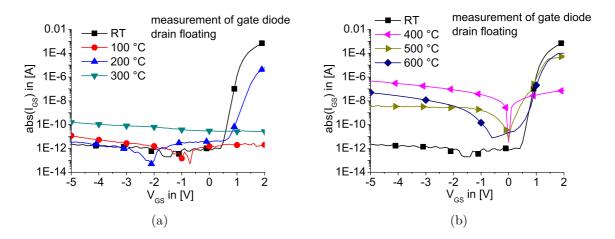

| 3.12 | Transfer characteristics in semilogarithmic scale of (a) the 1000 nm and 450 nm MISHEMTs, (b) the 200 nm and 50 nm MISHEMTs, (c) the 1000 nm and 450 nm HEMTs, and (d) the 200 nm and 50 nm HEMTs  Extracted I <sub>off</sub> vs. W <sub>G</sub> of (a) the 1000 nm and the 450 nm MISHEMTs, (b) the 200 nm and 50 nm MISHEMTs, (c) the 1000 nm and 200 nm HEMTs, and (d) the 450 nm and 50 nm HEMTs | 35<br>37<br>38 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4.1  | Change of (a) $R_{sh}$ and (b) $V_{th}$ with temperature                                                                                                                                                                                                                                                                                                                                             | 42             |

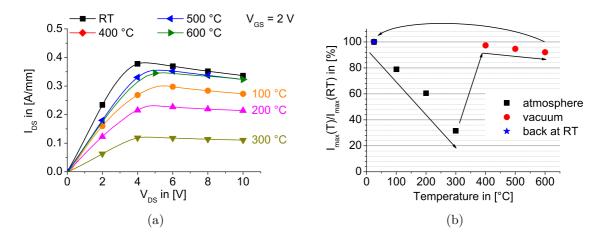

| 4.2  | Temperature dependent output characteristics at $V_{GS} = 2 \text{ V}$ (a) and                                                                                                                                                                                                                                                                                                                       | 43             |

| 4.3  | corresponding extracted peak current density (b)                                                                                                                                                                                                                                                                                                                                                     |                |

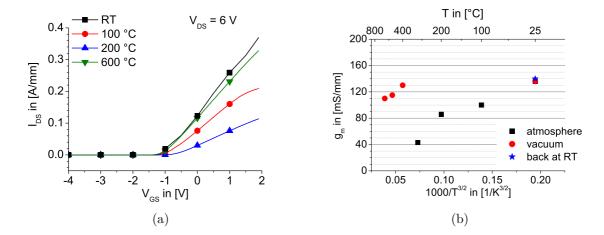

| 4.4  | (b)                                                                                                                                                                                                                                                                                                                                                                                                  | 44<br>45       |

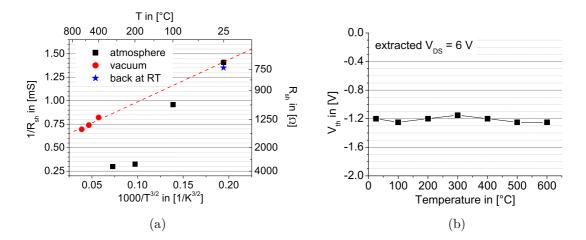

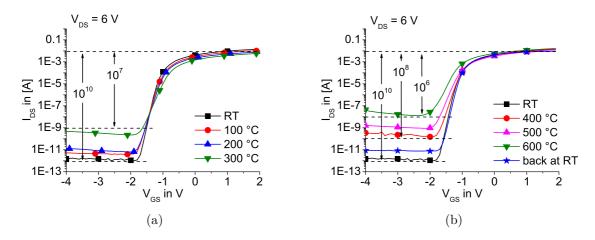

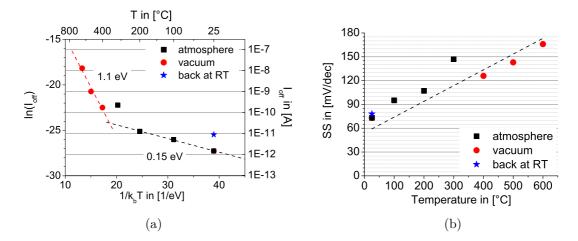

| 4.5  | Arrhenius plot of $I_{\rm off}$ (a) and change of SS with temperature (b)                                                                                                                                                                                                                                                                                                                            | 46             |

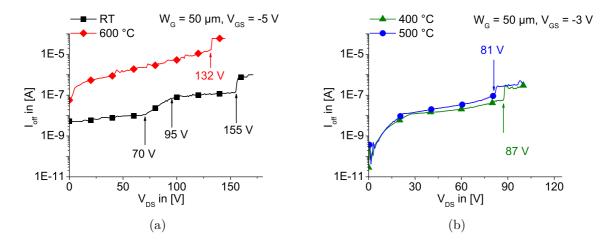

| 4.6  | Breakdown measurements at different temperatures                                                                                                                                                                                                                                                                                                                                                     | 47             |

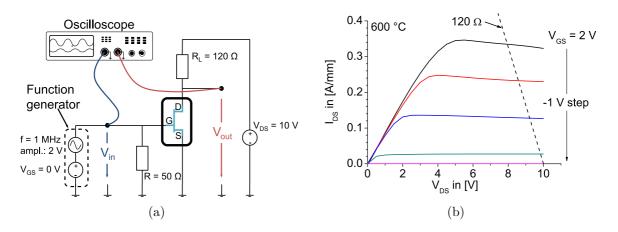

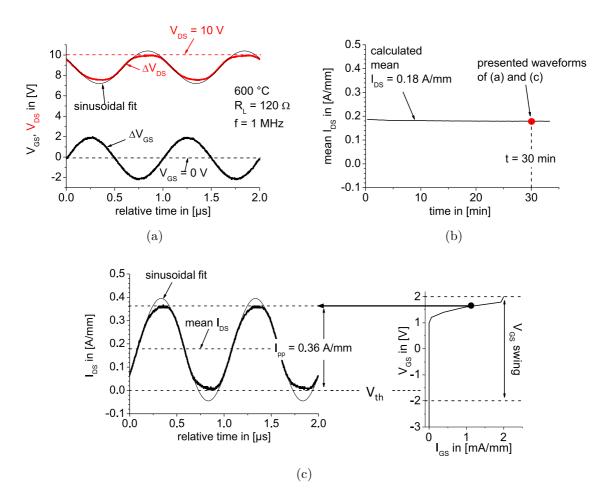

| 4.7  | (a) Sketch of the measurement setup and (b) position of load line in output characteristics                                                                                                                                                                                                                                                                                                          | 48             |

| 4.8  | Results of 600 °C large-signal operation                                                                                                                                                                                                                                                                                                                                                             | 50             |

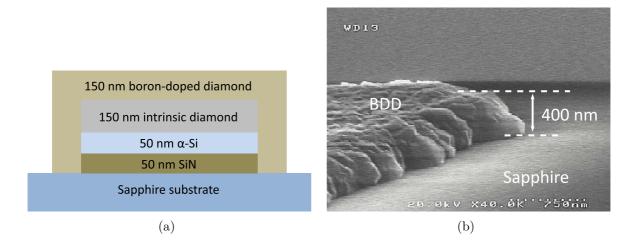

| 5.1  | (a) Schematic representation of the BDD electrode structure. (b) SEM zoom to an electrode edge with BDD overgrown sidewalls                                                                                                                                                                                                                                                                          | 55             |

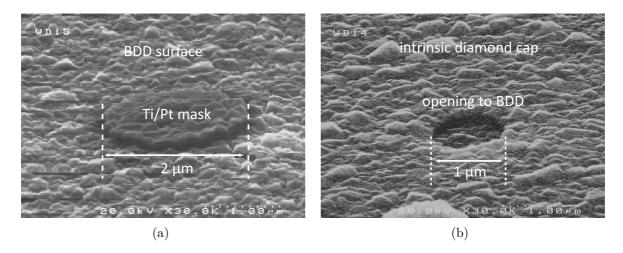

| 5.2  | SEM pictures of (a) Ti/Pt growth mask and (b) opening in intrinsic diamond                                                                                                                                                                                                                                                                                                                           | 56             |

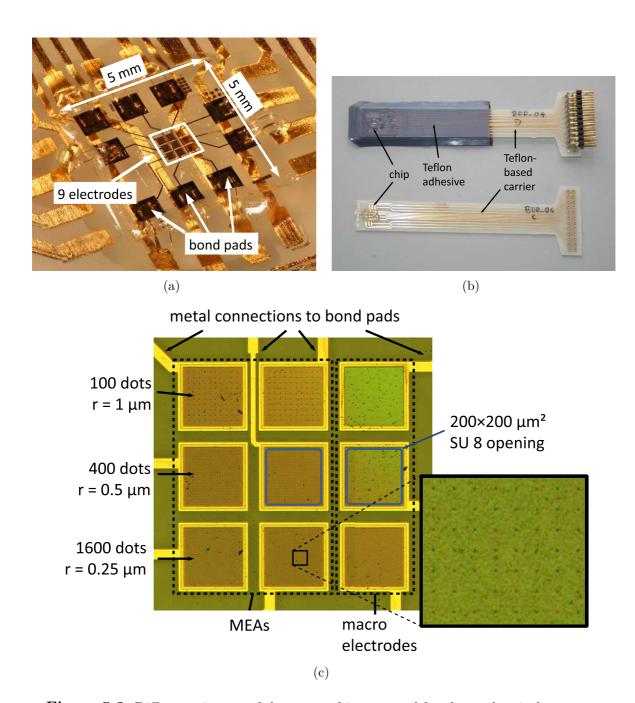

| 5.3  | Different pictures of the sensor chip prepared for electrochemical measurements                                                                                                                                                                                                                                                                                                                      | 58             |

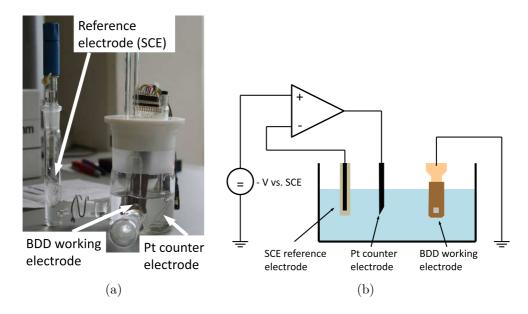

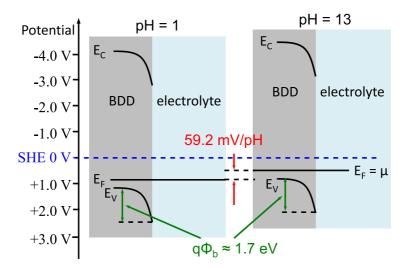

| 5.4  | Photograph of electrochemical cell (a) and simplified sketch of the three electrode measurement setup controlled by a potentiostat (b)                                                                                                                                                                                                                                                               | 59             |

| 5.5  | Schematic representation of the BDD/electrolyte interface                                                                                                                                                                                                                                                                                                                                            | 61             |

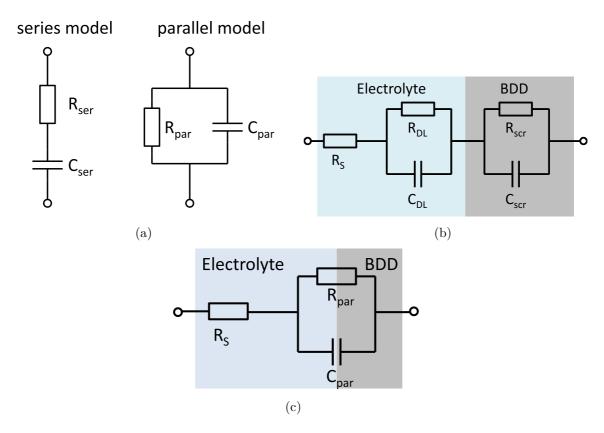

| 5.6  | (a) Simple series and parallel equivalent circuit model used for CV mea-                                                                                                                                                                                                                                                                                                                             |                |

|      | surements. (b) Real equivalent circuit model                                                                                                                                                                                                                                                                                                                                                         | 63             |

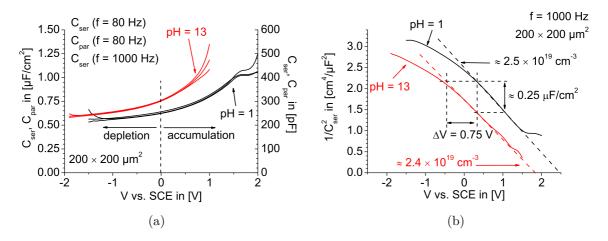

| 5.7  | Resulting capacitance of CV measurements                                                                                                                                                                                                                                                                                                                                                             | 64             |

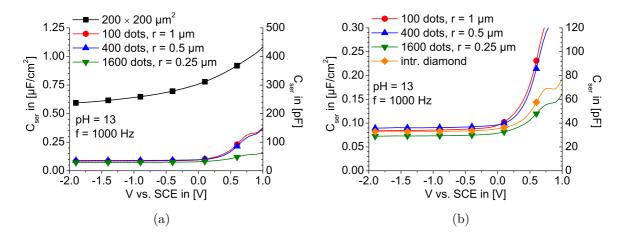

| 5.8  | (a) Extracted capacitances of different MEAs compared to large area BDD electrode and (b) capacitances of the different MEAs compared to an all intrinsic diamond electrode                                                                                                                                                                                                                          | 65             |

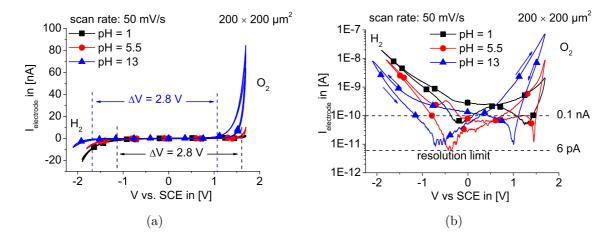

| 5.9  | Results of cyclic voltammetry measurements in linear (a) and semiloga-                                                                                                                                                                                                                                                                                                                               |                |

|      | rithmic (b) scale                                                                                                                                                                                                                                                                                                                                                                                    | 66             |

| 5.10 | Cyclic voltammetry measurements of different BDD electrodes in pH = 1 $(0.1 \text{ M H}_2\text{SO}_4)$ in linear (a) and semilogarithmic (b) scale                                                                                                                                                                                                                                                   | 67             |

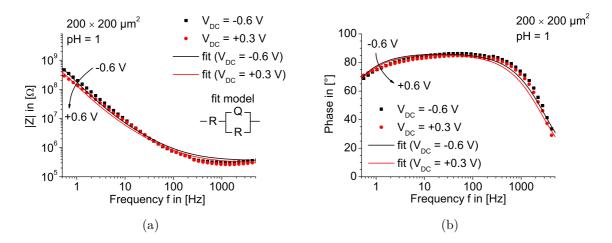

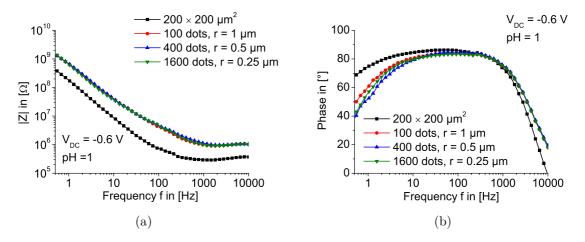

| 5.11 | Results of impedance spectroscopy measurements depicted in (a) Bode magnitude and (b) Bode phase diagram                                                                                                                                                                                                                                                                                             | 69             |

|      |                                                                                                                                                                                                                                                                                                                                                                                                      |                |

List of Figures vii

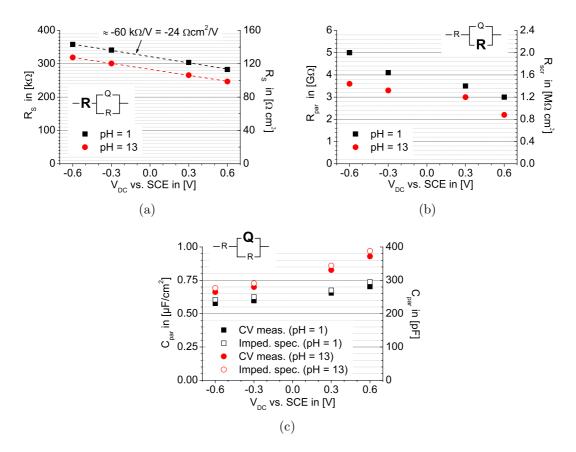

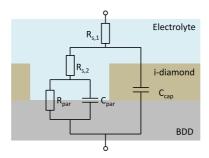

| 5.13        | Values of $R_S$ (a), $R_{par}$ (b), and $C_{par}$ (c) extracted by numerical fitting of impedance spectroscopy at different potentials                                                                                  | 71<br>72<br>72 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

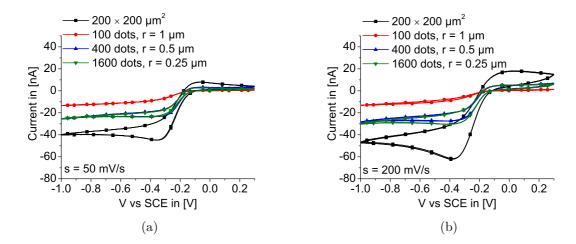

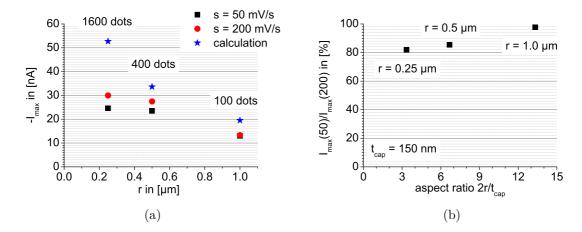

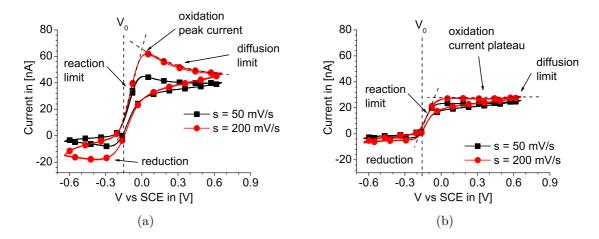

|             | Cyclic voltammograms for the reduction of 1 mMol Ru $(NH_3)_6^{3+}$ at a scan rate of $s = 50$ mV/s (a) and $s = 200$ mV/s (b)                                                                                          | 75             |

| 3113        | ratio $I_{max}(s=50 mV/s)/I_{max}(s=200 mV/s)$ with aspect ratio $2r/t_{cap}$                                                                                                                                           | 76             |

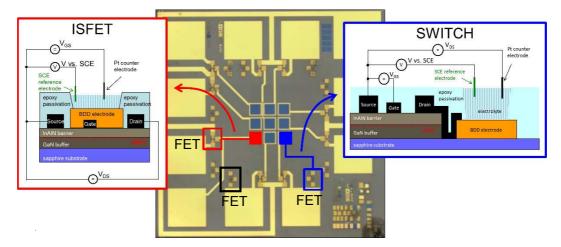

| 6.1<br>6.2  | Picture of the fabricated sensor array chip                                                                                                                                                                             | 79             |

| 6.3<br>6.4  | integration of diamond and InAlN/GaN HEMTs                                                                                                                                                                              | 81<br>82<br>83 |

| 6.5         | DC HEMT output characteristics of a 50 $\mu$ m wide device                                                                                                                                                              | 84             |

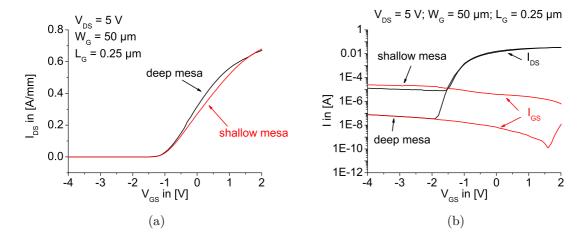

| 6.6         | Linear (a) and semilogarithmic (b) transfer characteristics at $V_{DS} = 5$ .                                                                                                                                           | 85             |

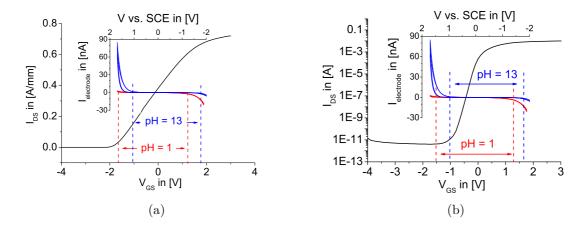

| 6.7         | InAlN/GaN HEMT transfer characteristics in (a) linear and (b) semilogarithmic scale correlated to the cyclic voltammogram of a BDD electrode.                                                                           | 88             |

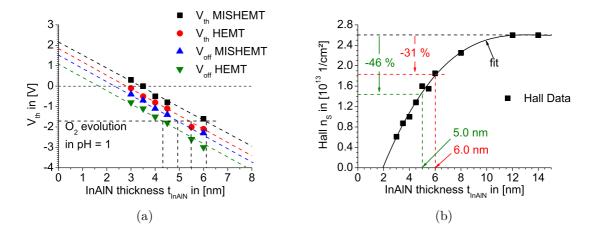

| 6.8         | (a) Change of threshold and pinch-off voltage with InAlN barrier thick-                                                                                                                                                 | 89             |

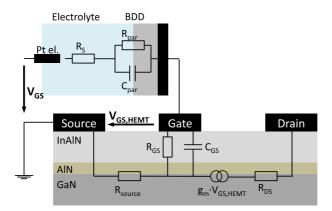

| 6.0         | ness. (b) Sheet charge density vs. t <sub>InAlN</sub>                                                                                                                                                                   | 90             |

| 6.9<br>6.10 | Depiction of the combined equivalent circuit model                                                                                                                                                                      | 90             |

| 6.11        | (a) HEMT output characteristics in the subthreshold regime with BDD IV characteristics as load line. (b) Constructed switch characteristics                                                                             | 95             |

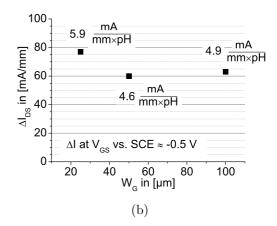

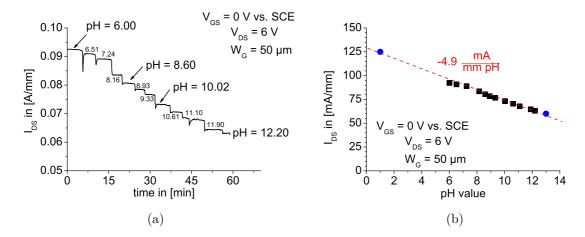

| 6 12        | Transfer characteristics of the hybrid ISFET system in different electrolytes.                                                                                                                                          | 98             |

|             | Voltage shift $\Delta V$ (a) and current shift $\Delta I_{DS}$ (b) obtained for different                                                                                                                               |                |

|             | gate-widths $W_G$                                                                                                                                                                                                       | 99             |

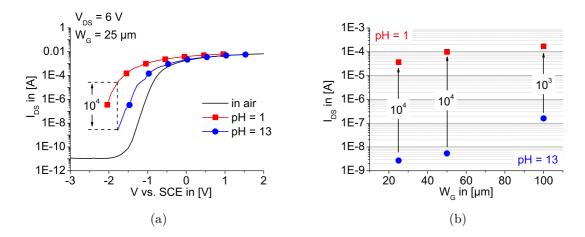

|             | (a) $I_{DS}$ monitored with time. (b) Change of $I_{DS}$ with pH value (a) Transfer characteristics in pH = 1 and pH = 13 in semilogarithmic scale. (b) Change of $I_{DS}$ in the subthreshold regime from pH = 1 to pH | 100            |

|             | = 13 for different $W_G$                                                                                                                                                                                                | 101            |

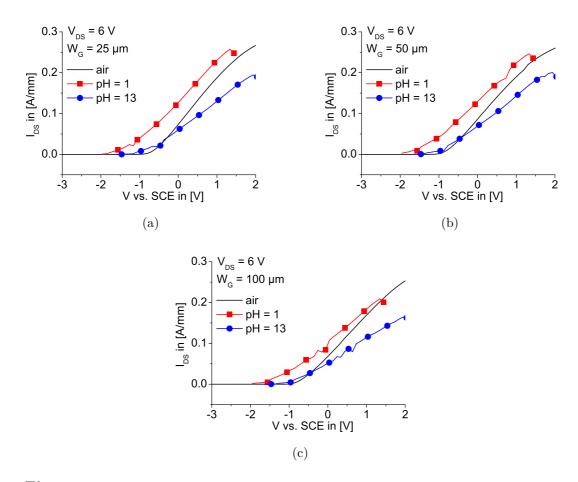

| 6.16        | Linear transfer characteristics of the MEA combined to (a) a 25 $\mu$ m, (b) a 50 $\mu$ m, and (c) a 100 $\mu$ m wide InAlN/GaN HEMT                                                                                    | 103            |

| 6.17        | (a) Voltage shift $\Delta V$ vs. $W_G$ extracted at $I_{DS}=0.05$ A/mm. (b) Current shift $\Delta I_{DS}$ vs. $W_G$ extracted at $V_{GS}=0$ V vs. SCE                                                                   | 104            |

| 6.18        | Linear transfer characteristics at $V_{DS} = 1$ vs. SCE with (a) a large                                                                                                                                                | 105            |

| 6.19        | Switching experiments with time in combination with (a) the large area                                                                                                                                                  | 106            |

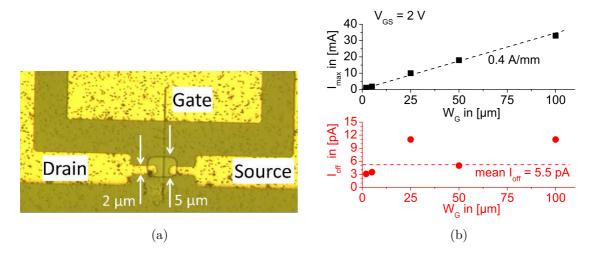

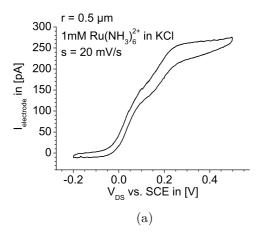

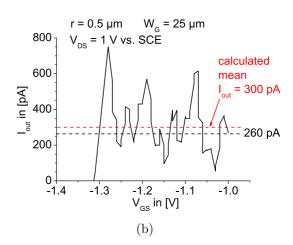

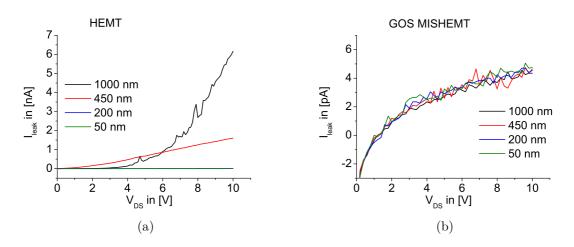

| 7.1<br>7.2  | (a) Picture of a 2 $\mu$ m wide MISHEMT. (b) $I_{DS}$ and $I_{off}$ vs. $W_{G}$ Cyclic voltammetry (a) and FET switch experiment (b) of 4 microelectrodes.                                                              |                |

viii List of Figures

| B.1<br>B.2<br>B.3        | Measurements of isolation currents                                                                                                                                                                                     | 0           |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| C.1                      | Measurements of the gate diode at different temperatures                                                                                                                                                               |             |

| D.1<br>D.2               | Electrochemical and physical energy scale                                                                                                                                                                              | 7           |

| D.3<br>D.4<br>D.5<br>D.6 | fusion layer                                                                                                                                                                                                           | 9<br>1<br>2 |

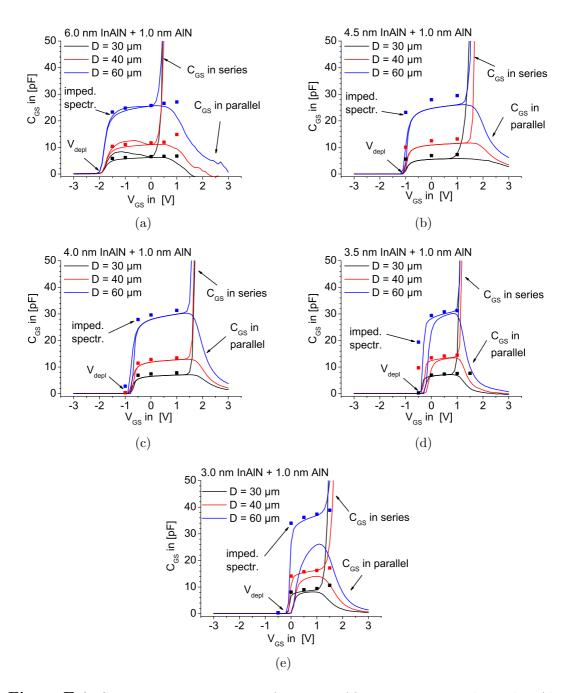

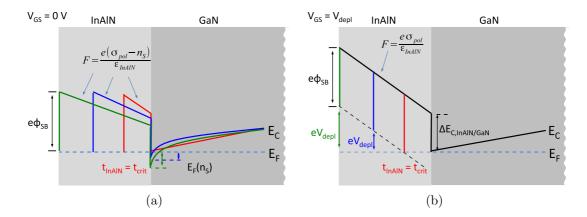

| E.1<br>E.2               | CV measurements on samples with different InAlN barrier layer thickness. 14 Band diagram of the InAlN/GaN HEMTs with different barrier layer thicknesses under (a) equilibrium conditions and (b) under depletion con- | 7           |

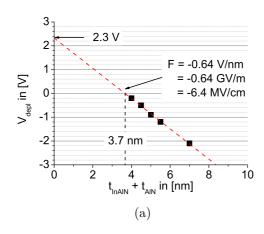

| E.3                      | ditions                                                                                                                                                                                                                |             |

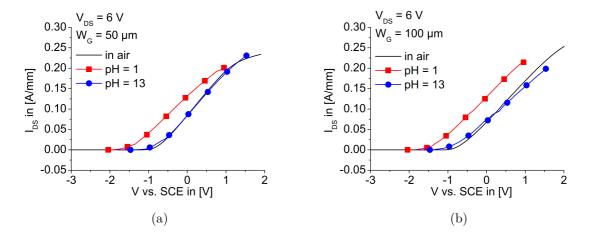

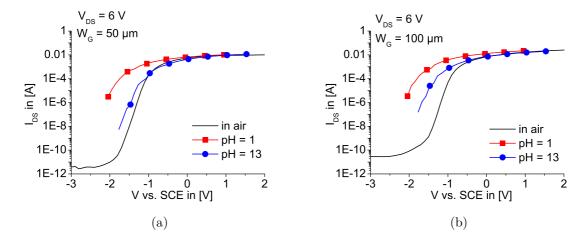

| F.1                      | Linear transfer characteristics of the whole system in ISFET configura-<br>tion. The large area electrode is connected to (a) a 50 $\mu$ m wide and to<br>(b) a 100 $\mu$ m wide gate device                           | 1           |

| F.2                      | (b) a 100 $\mu$ m wide gate device                                                                                                                                                                                     |             |

# **List of Tables**

| 1.1 | Selected material properties of Si, GaAs and the wide band gap materials SiC, GaN, and diamond at room temperature                                                                                                          | ]  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Material properties of standard substrates for GaN heteroepitaxy at room temperature                                                                                                                                        | 26 |

| 3.2 | Comparison of the standard HEMT and the GOS MISHEMT fabrication scheme.                                                                                                                                                     |    |

| 5.1 | Values of the individual circuit components (figure 5.13) obtained by numerical fitting of the measured frequency response of a microelectrode array. The measurement conditions were: $pH = 1$ : $V_{DC} = -0.6 \text{ V}$ | 73 |

# List of Abbreviations and Symbols

#### List of Acronyms

2DEG Two-Dimensional Electron Gas 2DHG Two-Dimensional Hole Gas

Al Aluminum

AlGaN Aluminum Gallium Nitride

AlN Aluminum Nitride

BDD Boron-Doped Diamond

BEN Bias-Enhanced Nucleation

CV Capacitance-Voltage

CVD Chemical Vapor Deposition

DHFET Double Heterostructure Field-Effect Transistor

$\varepsilon$  Permittivity

E<sub>C</sub> Conduction Band Energy

$\begin{array}{ccc} E_F & & Fermi \; Energy \\ E_G & & Band \; Gap \end{array}$

$\begin{array}{ll} E_{SD} & Surface \ Donor \ Energy \\ E_{V} & Valence \ Band \ Energy \\ \Delta E_{C} & Conduction \ Band \ Offset \end{array}$

$\begin{array}{ccc} F_{pol} & Polarization \ Field \\ FET & Field-Effect \ Transistor \\ g_m & Transconductance \\ GaAs & Gallium \ Arsenide \\ GaN & Gallium \ Nitride \\ GOS & GaN-On-Sapphire \\ \end{array}$

HEMT High Electron-Mobility Transistor

HFCVD Hot-Filament Chemical Vapor Deposition HTMC High-Temperature Measurement Chamber

InAlN Indium Aluminum Nitride InGaN Indium Gallium Nitride

InN Indium Nitride

ISFET Ion-Sensitive Field-Effect Transistor

$\mu$  Electrochemical Potential

$\mu_{\rm C}$  Chemical Potential Electron Mobility

xii List of Tables

MEA MicroElectrode Array

MEMS Micro Electro-Mechanical System

MISHEMT Metal-Insulator-Semiconductor High Electron-Mobility Tran-

sistor

MOCVD Metal-Organic Chemical Vapor Deposition

MOSFET Metal-Oxide-Semiconductor High Electron-Mobility Transis-

tor

n<sub>S</sub> 2DEG Sheet Charge Carrier Concentration

$\Phi_{SB}$  Schottky Barrier Height

$\Phi_{SP}$  Surface Potential

P<sub>SP</sub> Spontaneous Polarization

P<sub>tot</sub> Total Polarization

PECVD Plasma-Enhanced Chemical Vapor Deposition

Pt Platinum

$\rho_{\rm C}$  Specific Contact Resistance

$\begin{array}{ccc} R_{sh} & Sheet \ Resistance \\ RF & Radio \ Frequency \\ RIE & Reactive \ Ion \ Etching \\ RT & Room \ Temperature \end{array}$

$\begin{array}{ccc} \text{RTA} & \text{Rapid Thermal Annealing} \\ \sigma_{\text{int}} & \text{Bound Interface density} \\ \text{SCE} & \text{Saturated Calomel Electrode} \\ \text{SEM} & \text{Scanning Electron Microscope} \\ \text{SHE} & \text{Standard Hydrogen Electrode} \end{array}$

Si Silicon

SiC Silicon-Carbide

SiN Silicon-Nitride

SOI Silicon-On-Insulator

SS Subthreshold Swing

TEM Tunneling Electron Microscope

#### List of Constants

$\begin{array}{lll} F & = 96485 \ C/mol & Faraday \ Constant \\ k_b & = 1.380 \times 10^{-23} \ J/K & Boltzmann \ Constant \\ q & = 1.6022 \times 10^{-19} \ C & Elementary \ Charge \\ R_g & = 8.314 \ \frac{J}{mol \cdot K} & Universal \ Gas \ Constant \end{array}$

# 1 Introduction and Motivation

In terms of speed, efficiency, heat and power handling capability, wide band gap semiconductor devices are predicted to exhibit device performances beyond that of conventional silicon (Si) or gallium arsenide (GaAs) electronics. Such predications are based on the existence of the large band gap and on certain materials properties of the wide band gap materials. Some important material parameters of Si, GaAs, and the wide band gap materials silicon carbide (SiC), gallium nitride (GaN), and diamond are compared in table 1.1. A large band gap essentially means an increased distance between electrons in the conduction band and holes in the valence band, which makes devices less susceptible to impact ionization and is associated with a large breakdown field F<sub>br</sub>. This allows for higher driving voltages at smaller device dimensions, thus potentially increasing speed and power density. The intrinsic carrier concentration n<sub>i</sub> is also linked to the band gap  $E_G$  and, in case of Si, it is in the range of  $10^{10}$  cm<sup>-3</sup> at room temperature. In contrast, the intrinsic carrier concentration of wide band gap materials at room temperature is well below 1 cm<sup>-3</sup> [1] leading to reduced noise and leakage, thus leading to a reduced overall power consumption. While their electron mobility  $\mu_{\rm el}$  is comparable to that of Si (except  $\mu_{el}$  of SiC), the saturation velocity  $v_{sat}$  of the wide band gap materials is above that of Si, thus enabling high-power microwave devices based on wide band gap semiconductors.

Furthermore, III-Nitride semiconductors are robust materials exhibiting an exceptionally high thermal and chemical stability. This means that electronic devices compatible with harsh environments, that cannot be tolerated by conventional Si or GaAs devices, may be feasible using wide band gap materials. This, i.e. the development of electronic

|                                                          | Si   | GaAs | GaN  | SiC | Diamond <sup>1</sup> |

|----------------------------------------------------------|------|------|------|-----|----------------------|

| Band gap $E_g$ [eV]                                      | 1.1  | 1.4  | 3.4  | 2.9 | 5.45                 |

| Electron mobility $\mu_{\rm el} \ [{\rm cm}^2/{\rm Vs}]$ | 1500 | 8500 | 1500 | 900 | 2200                 |

| Saturation velocity $v_{sat}$ [10 <sup>7</sup> cm/s]     | 1.0  | 1.0  | 1.3  | 2.0 | 2.7                  |

| Breakdown field F <sub>br</sub> [MV/cm]                  | 0.3  | 0.6  | 5    | 3   | 100                  |

**Table 1.1:** Selected material properties of Si, GaAs and the wide band gap materials SiC, GaN, and diamond at room temperature after [1, 2, 3, 4]. <sup>1</sup> Values of limited technological use.

devices for harsh environments, is one aim of this work. Subject of chapter 4 will be high-temperature electronics, in this work up to 600 °C. Chapter 5 and chapter 6 will discuss chemical sensor applications also for the use in strong acidic (pH = 1) or alkaline (pH =13) liquid media. Chemical sensor applications take advantage of the high corrosion resistivity and high-temperature electronics take advantage of the high thermal stability and the initially low intrinsic carrier concentration, where an extrapolation of  $n_i$  towards higher temperatures yields, that the room temperature carrier concentration of Si is reached at temperatures as high as 500 °C, 700 °C and 1250 °C for SiC, GaN, and diamond, respectively.

In this work, the materials chosen to address such applications were GaN and diamond. Diamond was chosen as chemical sensor, because of its superior chemical stability and inertness. Combined with its biocompatibility, high transparency, and especially the possibility to use it for potentiometric as well as for amperometric measurements, i.e. for pH tracking and the detection of redox reactions, diamond is the state-of-the-art material for chemical sensors applicable in aggressive media and in biomedical applications [5, 6, 7, 8]. Considering the material parameters, it would also present the ideal choice for the development of high-performance field-effect transistors (FETs). However, up to now diamond faces some severe technological challenges limiting the development of diamond electronic devices. Some of these hurdles, but also achievements in diamond technology are subject of chapter 5. Currently, the material superseding all others for the fabrication of high-grade electronic devices is GaN. Therefore, GaN was chosen for the development of high electron-mobility transistors (HEMTs) compatible with high temperatures and the integration with diamond electrodes for the fabrication of an electrochemical sensor system. Thus, such prepared sensor systems can take advantage of both, the superior chemical properties of diamond and the excellent electronic properties of GaN HEMTs. To accomplish a possible dual mode operation, i.e. pH tracking and detection of redox reactions, two different combinations of these two elements will be discussed in chapter 6, introducing the HEMT as transducer in an ion-sensitive field-effect transistor (ISFET) and as electronic switch to turn on and off redox reactions. Since they present the core elements, a large part of this work is dedicated to the description and analysis of GaN FETs (chapter 3) and diamond electrodes (chapter 5) in light of the two envisaged applications.

The term GaN HEMT usually refers to a material system comprising at least two of the group-III nitrides or nitride semiconductors. This material group is constituted of the binary compounds indium nitride (InN), aluminum nitride (AlN), and gallium nitride (GaN), their ternary alloys aluminum-gallium nitride (AlGaN), indium-gallium nitride (InGaN), indium-aluminum nitride (InAlN) or even quaternary alloys thereof. In contrast to conventional HEMTs, a two-dimensional electron gas (2DEG) can be created without the need of intentional doping, but results from the high polarity of the nitride semiconductors. More precisely, the 2DEG is generated due to the polarization discontinuity at the heterointerface of two nitrides. The first GaN-based HEMT exploiting the high resulting polarization discontinuity, was established using an AlGaN

barrier/GaN buffer heterostructure. However, today the InAlN/GaN heterostructure system is gaining increasing interest for the development of GaN-based HEMTs. The advantage of InAlN as barrier layer material is that it can be grown lattice-matched onto GaN when the Al-content is around 83 %. Thus, the material system experiences no strain, which potentially increases stability. As will be explained in chapter 3, a further advantage of such Al-rich alloys is a larger polarization discontinuity to GaN, thus leading to a high carrier concentration in the 2DEG, in case of the lattic-matched InAlN/GaN material system up to  $2.6 \times 10^{13}$  cm<sup>-2</sup> [9]. Additionally, these high carrier densities can be achieved at thin barrier layer thicknesses, which would allow for further device scaling, while maintaining a rather high aspect ratio [2, 10, 11]. Hence, compared to more conventional AlGaN/GaN HEMTs lattice-matched InAlN/GaN HEMTs can be faster with even higher power densities. Indeed, rather impressive results were obtained with this lattice-matched InAlN/GaN material system. A high output current density of 2.3 A/mm [12] and device operation at 1000 °C [13, 14] were already demonstrated, indicating a high capability in power applications and an extremely high, ceramic-like thermal stability. Its high-speed capability was recently demonstrated with a high transit frequency of  $f_T = 370$  GHz at a gate length of 30 nm [15]. Output power densities of  $P_{out} = 10 \text{ W/mm}$  at a frequency of 10 GHz were obtained with a rather conventional device technology [16]. Furthermore, normally-off, enhancement mode devices with a high output current density of 1.9 A/mm and a very high extrinsic transconductance of  $g_m = 800 \text{ mS/mm}$  were obtained employing a gate-recess technology [17]. All these numbers express the high degree of maturity this material system already reached and are convincing arguments for the use of lattice-matched InAlN/GaN HEMTs in the two targeted applications. Additionally, because of its exceptional, ceramic-like stability, the lattice matched InAlN/GaN heterostructure is the only material system known presently, which allows the overgrowth of fully fabricated HEMTs with high quality polycrystalline diamond [18]. Therefore, this material system currently is the only material system allowing the realization of the envisaged electrochemical sensor system.

This previous statement can be made because the deposition of diamond films is linked to an extremely harsh growth process, especially if the film is prepared for electrochemical applications. Prepared for electrochemistry means that the amount of sp²-bonded carbon (graphitic phases) in the polycrystalline diamond film is low, which is necessary to exploit the full potential of diamond electrodes. This means a high chemical stability, a large potential window, i.e. the potential difference between hydrogen and oxygen evolution (electrolysis), and a low background current within the potential window [5, 19]. However, to this day diamond films of high electrochemical grade are obtained at growth temperatures above 750 °C [20]. Another prerequisite to allow electrochemical applications in terms of both, amperometric and potentiometric measurements, is a diamond layer exhibiting metal-like conductivity on the electrode surface. This is mostly realized by the deposition of a heavily boron-doped diamond (BDD) film, with a surface which is sensitive to the pH value, i.e. the concentration of hydronium ions (H<sub>3</sub>O<sup>+</sup>) in an electrolyte, but also allows for charge transfer across the BDD/electrolyte phase boundary. Compared to conventional noble metal electrodes such BDD electrodes can

then exhibit extraordinary device properties, like the large potential window of approximately  $\Delta V = 3 \text{ V } (\Delta V \approx 1.5 \text{ V } \text{for metal electrodes})$  and a background current in the range of  $\mu A/\text{cm}^2$  (compared to approximately mA/cm² of metal electrodes). This enables the detection of redox reactions, which usually occur at potentials outside the stability window of water and allows the detection of lower signal currents, i.e. lower concentrations with higher resolution. This already lead to the realization of individually addressable BDD micro- and nanoelectrodes, e.g. arranged in a 3 by 3 matrix with 2  $\mu$ m pitch, for the spatial and time resolved detection of single cell activities [21, 22]. In these experiments, the resulting ion currents were in the range of 15 pA to 25 pA and were observed for a few milliseconds.

Obviously both elements, the lattice-matched InAlN/GaN HEMT and the BDD electrode, have successfully demonstrated their capabilities within their respective applications, however so far mainly as individual components. The challenge for the development of the sensor system, where these two elements are combined, is to engineer the lattice-matched InAlN/GaN HEMT in a way that it is compliant with specific requirements established by the BDD electrode, especially for the perspective of array integration possibly with high integration density, thus high spatial resolution, of individual addressable microelectrodes. Among others, one specific and important requirement is the need of a low overall FET leakage. Considering for example the above mentioned ion current of 15 pA means, in case of individual addressable electrodes, that the In-AlN/GaN HEMT (as switch) must be able to block this low current. In case of ISFET measurements gate leakage can cause an unbalanced bias distribution, in turn causing a drop of the extrinsic transconductance, thereby limiting the achievable pH resolution. Additionally, leakage currents between separate devices of an integrated system may lead to noise and cross-talk [21, 23], thus limiting the spatial resolution. Similar thoughts also apply to high-temperature electronics. Here, an initially low leakage current is desired, since leakage may be further activated, when rising the ambient temperature. Excessive gate leakage, for instance, can limit the applicable input voltage drive, thus limiting the resulting output current swing. A residual drain-source leakage can prevent complete pinch-off. In consequence the resulting output voltage swing, hence the output power in RF applications is decreased. Both phenomena were already observed in previous high-temperature experiments [13, 24].

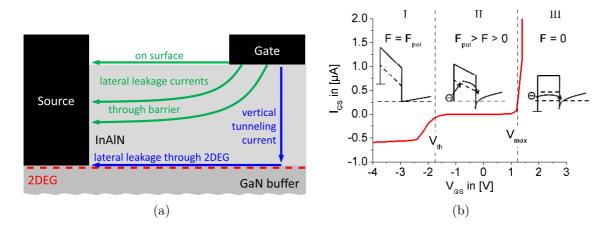

Thus, in order to accomplish good performances in high-temperature electronics and in electrochemical sensor applications, the elimination of parasitic leakage currents, here especially of the InAlN/GaN HEMT, is of high priority. However, device leakage in GaN-based HEMTs is still one of the main hurdles preventing optimum performance, especially under extreme operations [13, 25, 26, 27, 28]. The dominating leakage current in GaN-based devices seems gate leakage, which is commonly ascribed to tunneling across the Schottky gate [29, 30]. Thus, in a number of experiments it was tried to increase the tunneling barrier by e.g. the deposition of an additional gate oxide [31, 32, 33], or by other surface modification techniques like post processing annealing [34], oxygen plasma treatment [35, 36] and thermal oxidation [37, 38], where the Schottky diode is then

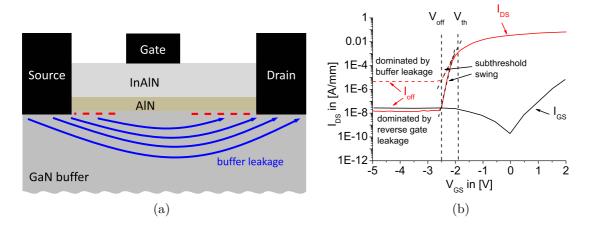

essentially replaced by a metal insulator semiconductor (MIS) diode. All these methods are capable to reduce the gate leakage currents by several orders of magnitude. Gate leakage currents in the lower nA/mm regime are typically reported. However, with an efficient reduction of gate leakage other leakage mechanisms, e.g. buffer leakage (drain to source) or, more general, off-state leakage, may become equally important. Buffer leakage is usually considered a matter of materials quality, which is why strategies to cope with buffer leakage usually focus on improvements in the heterostructure growth technology [39].

In this work, the limit of "acceptable" device leakage certainly is established by the 15 pA ion current, which is seen using individual BDD microelectrodes. Nevertheless, a residual off-current I<sub>off</sub> of the lattice-matched InAlN/GaN HEMT, significantly lower than these 15 pA, would be needed to achieve a reliable detection of such a signal. Therefore, in this work a new InAlN/GaN HEMT technology on sapphire substrates was developed, which is capable to reduce the overall device leakage of a 50  $\mu$ m wide HEMT to approximately 1 pA. This technology is inspired by the Silicon-on-Insulator (SOI) technology (essentially Si on sapphire) and employs a deep isolation process leaving small, confined mesa islands on the substrate, thin buffers (here as thin as 50 nm) heterostructures, and thermal oxidation of the InAlN barrier. Thus, in reference to SOI this technology may be referred to as GaN-on-Sapphire (GOS) technology leading to lattice-matched InAlN/GaN MISHEMTs. Although it seems already outdated as substrate material, especially for the fabrication of high power, high frequency GaN HEMTs, here sapphire presents one of the key features of this technology, which is linked to its high insulation properties. The capabilities of such lattice-matched InAlN/GaN MISHEMTs prepared in this way, were then tested at high ambient temperatures and in combination with BDD electrodes for electrochemical applications.

Thus, the outline of this thesis follows the route from the development of low leakage lattice-matched InAlN/GaN HEMTs to their applications in high-temperature electronics and in electrochemical applications, here as extended-gate ISFET or as switch for individual electrode pixels. The initial chapter Lattice-Matched InAlN/GaN **HEMT Device Basics** introduces the material system of the group-III nitrides and the basic operation principles of GaN-based HEMTs, however, clearly focusing on the lattice-matched InAlN/GaN material system, also giving an insight into three important contributions to the leakage currents of GaN HEMTs. Then, the chapter Low-Leakage Lattice-Matched InAlN/GaN HEMTs on Sapphire introduces the GOS technology, which was developed to eliminate the leakage current. The corresponding device characterization compares the GOS MISHEMT technology to a conventional GaN HEMT technology, here especially with respect to the leakage or subthreshold behavior. Afterwards, the chapter Thin Body InAlN/GaN MISHEMT: Device Operation up to 600 °C discusses the change of device characteristics at elevated temperatures. First long-term stability experiments by means of high-temperature storage and high-temperature large-signal class A measurements at radio frequency (RF) are presented for this new, thin material configuration. After the discussion of hightemperature electronics, the focus of the thesis is moved to the field of electrochemical sensors. This starts in chapter 5 Diamond Electrodes for the Integration with *InAlN/GaN HEMTs* with the introduction of the BDD electrode as chemical sensor. All relevant parameters, which establish the specific electrochemical requirements for the InAlN/GaN HEMT in a combined measurement system are extracted in this chapter. This is linked to a discussion of the BDD/electrolyte phase boundary, which is used to explain the pH sensitivity. Since it is of particular interest for the design of ISFETs, an equivalent circuit model of this interface is derived mainly relying on electrochemical impedance spectroscopy. Additionally, microelectrode arrays (MEAs) are introduced as electrode structures for advanced amperometric measurements. The actual combination of BDD electrodes and InAlN/GaN MISHEMTs is then discussed in chapter 6 Combining InAlN/GaN HEMTs and BDD Electrodes for Electrochemical Sensing **Applications**, where initially two different technologies to achieve the monolithic integration of diamond and GaN HEMTs are presented. During this work, a new "diamond first" integration technique was investigated, which could eliminate concerns about the compatibility of electronic materials with the harsh diamond growth conditions. Subsequently, the two different measurement configurations, i.e. the ISFET configuration for pH tracking and the switch configuration to switch on/off redox currents, are discussed with respect to the boundary conditions given through the BDD electrode. In other words, this means a deduction of certain design criteria for the FET to be compliant with the electrochemical requirements, hence stressing the importance of a low FET leakage characteristic. The chapter closes with the presentation of the achieved results in both measurement configurations. Finally, the chapter *Closing Remarks* provides a summary of the main ideas and results obtained during this work and presents an perspective for the development of a miniaturized electrochemical sensor system.

# 2 Lattice-Matched InAIN/GaN HEMT Device Basics

High-temperature electronics and the integration with diamond for the development of electrochemical sensor systems are two applications, which supplement the application range of InAlN/GaN electronic devices, which, so far, is mainly centered around highpower operation at high-frequencies. All these applications benefit from the excellent materials properties, where the key enabling parameter for the two applications being discussed in this work, namely high-temperature electronics beyond the limit of silicon devices (chapter 4) and the integration with diamond for electrochemistry (chapter 6), is the extremely high, ceramic-like thermal stability, especially of the lattice-matched InAlN/GaN heterostructure. Indeed, HEMT operation at temperatures up to 1000 °C [13] and the integration with diamond [18] (of high electrochemical grade <sup>1</sup>) had already been demonstrated using lattice-matched InAlN/GaN HEMTs. One parameter limiting the performance of GaN-based devices under high-temperature operation, but also in power applications, is parasitic leakage. Thus, a technological implementation to address leakage phenomena is welcome to further enhance the device performance in the different applications. A precise control of leakage currents, however, is of particular interest for high-temperature electronics, since leakage currents may be further activated with temperature. In case of electrochemical sensor systems, where in this work a diamond electrode is connected either to the gate or the drain of the transistor, leakage currents may cause an unbalanced bias distribution, thus limiting the sensor output range. Additionally, leakage currents present a hurdle for the realization of sensor systems with high integration density, especially with respect to biomedical applications, where measurements of single cells with high spatial resolution are targeted and signals in the range of 15 pA are expected [22].

The term leakage, however, is used for a rather wide spectrum of different phenomena depending on the application being discussed, thus also referring to different sources of leakage currents with a possibly predefined evaluation technique. In digital applications, for instance, leakage may refer to the dynamic losses when switching from high (low) to low (high) state, but also to the residual drain-source current due to a insuffi-

<sup>&</sup>lt;sup>1</sup>high electrochemical grade shall refer to a low amount of sp<sup>2</sup>-bonded carbon (graphitic phases) in the diamond lattice, which is only achieved at diamond growth temperatures above T > 750 °C (see chapter 5)

ciently depleted channel in the low state ( $V_{GS} = 0$  V [40]). Under radio-frequency (RF) operation leakage may be linked to dis-/charging of (parasitic) capacitances or traps [41, 42, 43]. However, the two applications being presented later in this work are mainly discussed within the frame of DC-operation. Therefore, the discussion and investigation of leakage currents, that will be given in this chapter, shall also be limited to DC device characteristics.

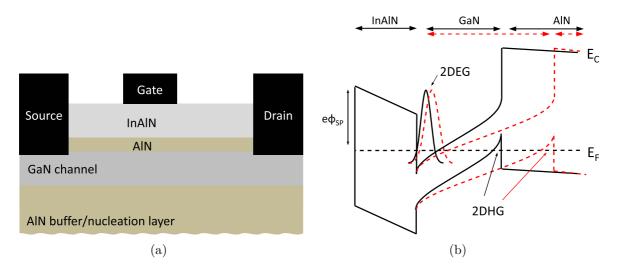

Since the group-III nitride semiconductors are already well established materials, there do exist a number of textbooks explaining the origin of polarization or the device physics of heterostructure systems comprised of these materials [2, 10, 11]. Therefore, a detailed discussion of the complete set of group-III nitrides and their ternary alloys will be omitted. Instead, this part shall briefly summarize the properties of the InAlN/GaN heterostructure system, especially in its lattice-matched configuration, explain the formation of the two-dimensional electron gas (2DEG) at the heterointerface, and give an insight into the InAlN/GaN HEMT operation technology. Since they are of high relevance for this work, also a first description of parasitic conduction paths shall be provided.

## 2.1 Crystal Structure of Nitride Semiconductors

The group-III nitrides are polar materials and crystallize in the noncentrosymmetric hexagonal close-packed (hcp) wurtzite structure exhibiting both, piezoelectric polarization  $P_{pz}$  and spontaneous polarization  $P_{sp}$ . Figure 2.1(a) schematically shows the wurtzite structure for the example of a GaN crystal, but is generally valid for InN, AlN or the ternary alloys InAlN, AlGaN and InGaN by replacing the Ga-atoms with the corresponding metal atom of the binary or ternary alloy. The crystal is described by the lattice constant  $a_0$  for the length of the basal hexagon and  $c_0$  for the height of the hexagonal prism (the subscript 0 indicates relaxed conditions), where, like in this work,  $a_0$  is generally perpendicular to and  $c_0$  parallel to the growth direction. Among the ternary alloys the In<sub>x</sub>Al<sub>1-x</sub>N system is special, because it can be grown latticematched to GaN. Since growth is carried out along the c-axis, lattice-matched refers to the lattice constant a<sub>0</sub>. The change of this lattice constant with the alloy composition x is predicted by Vegard's law and is shown for the different ternary alloys Al<sub>x</sub>Ga<sub>1-x</sub>N,  $In_xAl_{1-x}N$ , and  $In_xGa_{1-x}N$  in figure 2.1(b). At an In-content of approximately 17 % the InAlN alloy is grown lattice-matched to GaN. Thus, a heterostructure comprised of a lattice-matched InAlN barrier and a GaN buffer does not bear internal strain, which might be the reason for its extremely high thermal stability even allowing the HEMT operation at temperatures as high as 1000 °C [13, 14].

**Figure 2.1:** (a) Hexagonal structure of the GaN crystal. Figure redrawn after [44]. (b) Change of lattice constant  $a_0$  with alloy composition x. The InAlN alloy can be grown lattice-matched to GaN when its In-content is approximately 17 %.

## 2.2 Formation of 2DEG in InAIN/GaN Heterostructures

In contrast to Si or GaAs devices, where the formation of a conductive channel relies on doping, the formation of the 2DEG at the heterointerface of two nitride materials relies on the discontinuity of the total polarization  $P_{tot}$  between the two materials, where  $P_{tot}$  is the sum of  $P_{sp}$  and  $P_{pz}$ . The formation of the 2DEG shall be illustrated with the help of figure 2.2, where InAlN is considered as the barrier and GaN as the buffer material. A gradient of the total polarization  $P_{tot}$  is associated with a fixed polarization charge density  $\sigma$  given by

$$\sigma = -\nabla P_{tot}. (2.1)$$

The fixed polarization sheet charges cause an accumulation of mobile charges of the same magnitude, but of opposite sign labeled as polarization-induced sheet charges. Assuming an abrupt interface of an InAlN/GaN heterostructure, where the two nitrides possess a different total polarization, the bound polarization charge at the interface will partially compensate leaving a net fixed polarization interface density equal to

$$\sigma_{int} = P_{tot,GaN} - P_{tot,InAlN}. \tag{2.2}$$

A positive  $\sigma_{\rm int}$  causes an accumulation of free mobile electrons (the 2DEG) at the heterointerface in the material with lower band gap (here, GaN). Thus, the sheet carrier concentration  $n_{\rm S}$  of the 2DEG should be given by the difference of the total polarization between these two materials. However, as will be explained below, this presents a maximum  $n_{\rm S}$ , which neglects the influence of the pinned surface potential (see below) resulting in a dependency on the InAlN barrier thickness.

Figure 2.2: Illustration of polarization-induced charges at an InAlN/GaN heterointerface.

**Figure 2.3:** (a) Change of the spontaneous polarization  $P_{sp}$  dependent on the material composition of random ternary alloys. (b) Fixed interface carrier density  $\sigma_{int}/q$ . The interface density of the lattice-matched InAlN/GaN system is  $\sigma/q = 2.6 \times 10^{13}$  cm<sup>-2</sup>. Calculated after [9].

In case of the lattice-matched InAlN/GaN configuration, where no strain is present in the material system, the total polarization is equal to the spontaneous polarization  $(P_{tot} = P_{sp})$ . Thus, the fixed interface density  $\sigma_{int}$  solely arises from the difference in spontaneous polarization. Figure 2.3(a) shows the change of the spontaneous polarization of random ternary alloys with the alloy composition x. The corresponding calculations follow the routine described in [45]. The spontaneous polarization of GaN is  $P_{\rm sp} = -0.034 \text{ C/m}^2$  and that of lattice-matched  $In_{0.17}Al_{0.83}N$  is  $P_{\rm sp} = -0.075 \text{ C/m}^2$ . According to equation (2.2) this results in a fixed interface density of  $\sigma_{\rm int} = 0.041 \text{ C/m}^2$ . Thus, the maximum 2DEG carrier concentration, which could be obtained from a latticematched InAlN/GaN heterostructure, is as high as  $n_S = 2.6 \times 10^{13}$  cm<sup>-2</sup>. For comparisons figure 2.3(b) shows the maximum n<sub>S</sub>, which could be obtained by any other GaN-based heterostructure also taking into account piezoelectric polarization (the corresponding calculations again follow [45]). In the more conventional AlGaN/GaN material system a similar high carrier concentration can only be achieved for an Al-content of approximately 50 %, which then inherits a significant lattice mismatch, thus internal strain in the barrier.

As mentioned above, the bound interface density  $\sigma_{\rm int}$  can be considered as an upper limit for the 2DEG carrier concentration, which can be obtained in a heterostructure neglecting the effect of the surface potential, thus the influence of the barrier layer thickness. In GaN heterostructures this surface potential  $\Phi_{\rm SP}$  (of the free surface) is given by a donor-like trap density (equal to  $\sigma_{\rm int}$ , also referred to as surface states) on the barrier surface, which represents the induced counter charges of the electrons in the channel [46], causing a dependency of the 2DEG concentration on the barrier layer thickness. This effect shall be explained with the help of figure 2.4(a), which compares the schematic band diagrams of three InAlN/GaN heterostructures with different barrier

layer thicknesses. The circle indicates the energy level of the surface donors  $E_{\rm SD}$ , where their states can be occupied (filled circle) or partially occupied (partially filled circle). The energy level of the surface donors is constant with respect to the conduction band  $E_{\rm C}$  and here assumed as a single trap level. Considering initially the band diagram of the thin InAlN barrier (dashed blue) means that the level of the surface donors is located below the Fermi energy. Thus, their states are completely filled with electrons. Hence, the source of electrons (the surface donor) is not ionized meaning that no electrons accumulate in the 2DEG ( $n_{\rm S}=0$ ). In this case the surface potential increases linearly with the barrier layer thickness and the electrical field across the barrier is equal to

$$F = \frac{q\sigma_{int}}{\varepsilon_{InAlN}}. (2.3)$$

With increasing barrier layer thickness the energy level of the surface donor approaches the Fermi energy enabling electron transfer from the surface donor to unoccupied states (of lower energy) in the GaN 2DEG channel. This barrier thickness is the critical thickness  $t_{\rm crit}$  (red band diagram in figure 2.4(a)). As the InAlN thickness increases further more electrons transfer from the donor to the channel until the surface state is empty (maximum  $n_{\rm S}$ ). As long as the surface donor is partially filled, the Fermi energy will remain at the donor level meaning that the surface potential is equal to the surface donor level ( $\Phi_{\rm SP}=E_{\rm SD}$ ) and independent of the barrier thickness. Since the polarization is then partially screened by the accumulated electrons, the electrical field across the barrier decreases with increasing  $n_{\rm S}$  (increasing  $t_{\rm InAlN}$ ) and is given by

$$F = \frac{q(\sigma_{int} - n_S)}{\varepsilon_{InAlN}}. (2.4)$$

The 2DEG concentration n<sub>S</sub> of the InAlN/GaN heterostructure is calculated by [9]

$$n_S = \frac{\sigma_{int}}{q} - \frac{\varepsilon_{InAlN}}{t_{InAlN} \cdot q} \left( \Phi_{SP} + \frac{E_F(n_S)}{q} - \frac{\Delta E_{C,InAlN/GaN}}{q} \right), \tag{2.5}$$

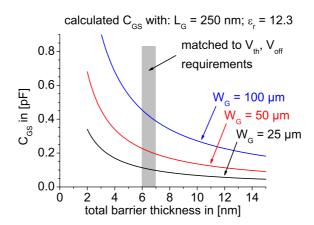

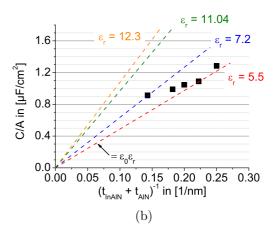

where  $\varepsilon_{InAIN} = 12.3$  is the permittivity of the barrier (see appendix E),  $t_{InAIN}$  is the barrier layer thickness,  $E_F(n_S)$  is the position of the Fermi-level with respect to the conduction band edge at the heterointerface, and  $\Delta E_{C,InAIN/GaN} = 0.65$  eV (see appendix E) is the conduction band discontinuity between GaN and InAlN (compare figure 2.4).

The resulting 2DEG concentrations of lattice-matched InAlN/GaN heterostructures for different barrier layer thicknesses (determined by Hall measurements) are shown in figure 2.4(b). For barrier layer thicknesses larger than 10 nm the carrier concentration in the channel is equal to the bound interface density  $(2.6 \times 10^{13} \text{ cm}^{-2})$ . In case of thinner barriers the 2DEG is partially depleted due to the pinned surface potential and vanishes completely at the critical barrier layer thickness  $t_{crit} = 2 \text{ nm}$ . The surface donor energy level of the lattice-matched InAlN/GaN heterostructure was identified by numerical fitting of experimental data (using Atlas Silvaco) to approximately  $E_{SD} = 0.6 \text{ eV} \dots 0.8 \text{ eV}$  below the conduction band edge (assuming a single trap level [47, 48]).

Figure 2.4: (a) Schematic representation of diagrams corresponding to three different InAlN barrier thicknesses. Green:  $t_{InAlN} > t_{crit}$ ; red:  $t_{InAlN} = t_{crit}$ ; dashed blue:  $t_{InAlN} \leq t_{crit}$ . (b) Change of the 2DEG carrier concentration of lattice-matched In-AlN/GaN heterostructures with barrier layer thickness. Squares correspond values of  $n_S$  obtained through Hall measurements (in part from [47]). The black curve presents a fit based on equation (2.5) with  $\Phi_{SP} = 0.8$  eV.

It is worth mentioning again that the ionized surface donors correspond to positive surface charges, which consequently represent the surface counter charges to the electrons in the 2DEG. Thus, the 2DEG charge carriers can be depleted by discharging these positive surface counter charges. For instance, this phenomenon is observed in the virtual gate effect, where electrons are injected from the gate to the surface states of the neighboring free barrier partially compensating the counter charges, thus depleting the 2DEG [44]. This phenomenon is coped with by a proper surface passivation scheme, like e.g. SiN passivation on top of the barrier or thermal oxidation of the InAlN surface, which is capable of stabilizing the surface counter charge [37]. Moreover, an ideal surface passivation scheme can reduce the influence of the surface potential by moving the surface states from the InAlN surface to the surface of the passivation layer [49]. Hence, a carrier concentration as high as the bound interface density ( $n_S \approx \sigma_{\rm int}/q$ ) can be obtained even in combination with thin barrier layers provided that an efficient surface passivation is applied [17].

In GaN-based HEMTs the dependency of  $n_S$  on the barrier layer thickness can be used to achieve normally-off devices. Typically, the barrier layer is then recessed underneath the gate down to the critical thickness, thereby eliminating the 2DEG in the gate region [17]. However, of special interest for the electrochemical application proposed in this work are lattice-matched InAlN barrier layers with a thickness of approximately 5 nm to 6 nm, because the resulting threshold voltage should be in the range of  $V_{\rm th}=-2~V$  (see chapter 6). In turn, the resulting  $n_S$  in that region is very sensitive to small variations of the barrier thickness. Using a linearized relation for that thickness range results in a variation of the carrier concentration of  $\frac{\Delta n_S}{\Delta t_{\rm InAlN}} \approx \frac{0.4~{\rm cm}^{-2}}{\rm nm}$ .

### 2.3 Principles of InAIN/GaN HEMT Operation

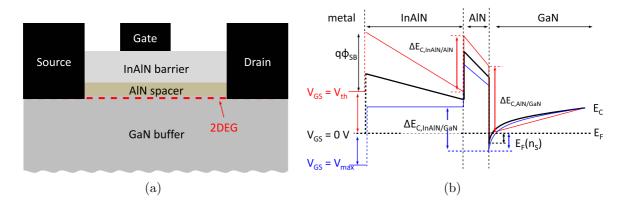

In an InAlN/GaN HEMT the current modulation is based on the modulation of the carrier concentration n<sub>S</sub> in the 2DEG channel and therefore is closely related to the discussion above. Here, the modulation of charges is done by varying the potential of the gate contact. Depicted in figure 2.5(a) is a typical cross section of an InAlN/GaN HEMT. The current path in such a HEMT device is from source through the 2DEG channel to the drain terminal. Source and drain present ohmic contacts to the 2DEG. The gate contact in between is a rectifying contact used to accumulate or deplete electrons of the 2DEG underneath the gate metal, thereby modulating the conductivity of the channel. A striking difference between the above discussed heterostructures and the presented device structure is the insertion of the AlN spacer between the InAlN barrier and the GaN buffer. The AlN spacer leads to a reduced roughness at the heterointerface and prevents a deep penetration of the electron wave function into the InAlN barrier layer. This leads to a reduction of alloy scattering, thus to an enhanced electron mobility in the channel [50]. It was shown through experiments and calculations that a 1 nm thin AlN layer is sufficient to efficiently suppress the penetration of the electron wave function into the barrier, while its influence on the bound interface density remains negligible [50]. Therefore, all calculations concerning the exact device structure (as depicted in figure 2.5(a)) can be carried out using the simplified model of the InAlN/GaN heterostructure.

The effect of carrier modulation by different gate potentials is illustrated in figure 2.5(b), which shows the corresponding band diagrams in case of three different gate potentials. For the sake of simplification only the conduction band is depicted, which is sufficient for n-channel InAlN/GaN devices. At the gate contact the surface potential  $\Phi_{SP}$  is then replaced by the Schottky barrier height  $\Phi_{SB}$ . Due to Fermi level pinning  $\Phi_{SB}$  is independent of the chosen gate metal [51, 52]. Initially, the black band diagram under equilibrium ( $V_{GS} = 0$  V) shall be considered. The fact that at 0 V gate bias the 2DEG channel is (partially) occupied implicitly states that the corresponding InAlN barrier thickness is larger than the critical barrier thickness (in reference to  $\Phi_{SB}$ ). Negative gate voltages will start depleting the 2DEG, which is completely depleted if the threshold voltage  $V_{GS} = V_{th}$  is applied (red band diagram). In that case the electrical field across the barrier is again equal to the polarization field given by equation (2.3). Through a positive gate voltage more electrons can accumulate in the 2DEG channel until the maximum  $n_S$  is reached at  $V_{GS} = V_{max}$ , where the polarization field is completely screened (flat band in the barrier, blue band diagram).

With the help of charge balance equations and the band diagrams of figure 2.5(b), the two voltages  $V_{th}$  and  $V_{max}$  can be calculated provided that the corresponding material parameters are known (here,  $\Delta E_{C,InAlN/GaN}$ ,  $\Phi_{SB}$ ,  $\varepsilon_{InAlN}$ ,  $E_F(n_S)$ , and  $\sigma_{int}$ ). The charge balance equation is written as

$$qV_{GS} + q\Phi_{SB} = F \times t_{InAlN} + \Delta E_{C,InAlN/GaN} + E_F(n_S). \tag{2.6}$$

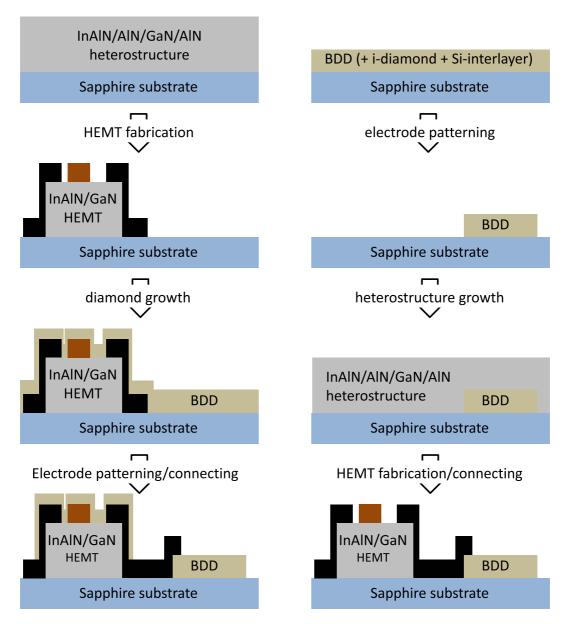

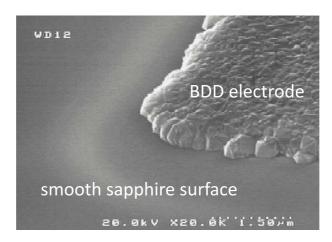

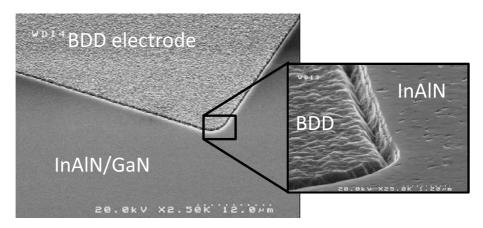

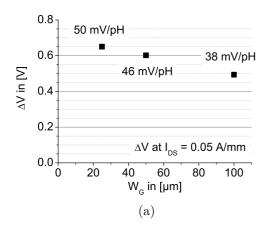

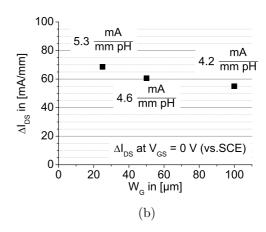

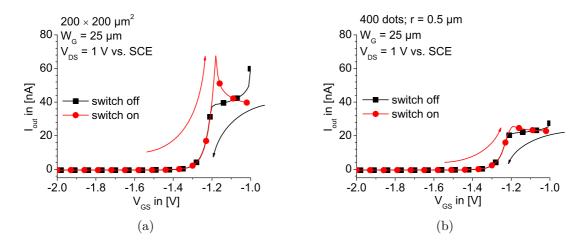

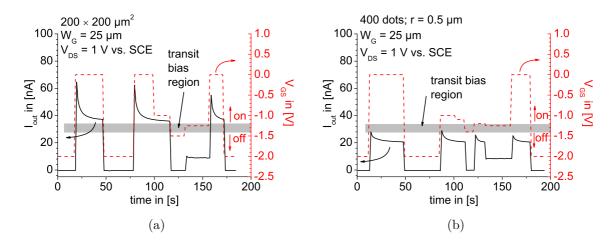

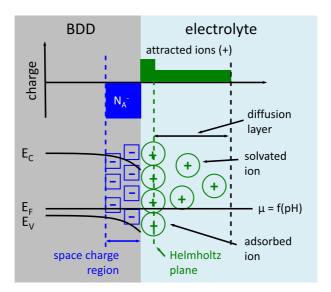

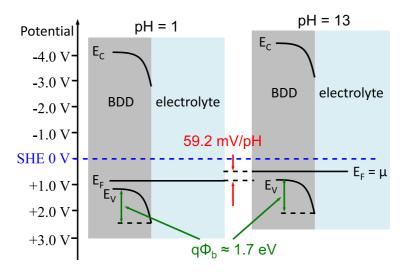

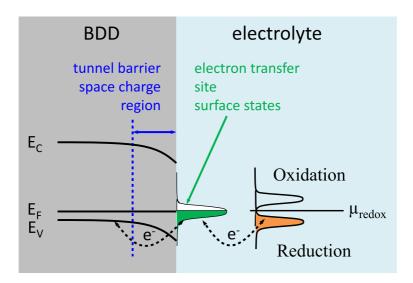

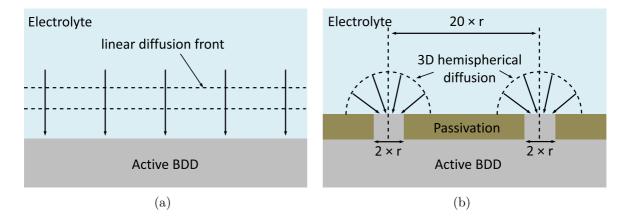

**Figure 2.5:** (a) Schematic cross section of an InAlN/GaN HEMT with the AlN spacer between the InAlN barrier and the GaN buffer layer. The 2DEG forms at the AlN/GaN interface inside the GaN. (b) Sketch of a corresponding band diagrams of the HEMT of (a) at three different gate potentials.